标题: Quartus EDA实验指导书下载(详解9个项目) [打印本页]

作者: 刺刀he 时间: 2017-12-6 16:58

标题: Quartus EDA实验指导书下载(详解9个项目)

EDA 实验指导书

实验一Quartus软件的使用

[实验目的] 掌握Quartus软件的使用。

[实验内容] 学习Quartus软件的设计操作步骤。

[实验原理]Quartus软件功能介绍。

Quartus软件功能简介:

1) 原理图输入(Graphic Editor)

Quartus软件具有图形输入能力,用户可以方便的使用图形编辑器输入电路图,图中的元器件可以调用元件库中元器件,除调用库中的元件以外,还可以调用该软件中的符号功能形成的功能块。

2) 硬件描述语言输入(Text Editor)

Quartus软件中有一个集成的文本编辑器,该编辑器支持VHDL,AHDL和Verilog硬件描述语言的输入,同时还有一个语言模板使输入程序语言更加方便,该软件可以对这些程序语言进行编译并形成可以下载配置数据。

3) 波形编辑器(waveform Editor)

Quartus9.1版本软件,在进行逻辑电路的行为仿真时,需要在所设计电路的输入端加入一定的波形,波形编辑器可以生成和编辑仿真用的波形,使用该编辑器的工具条可以容易方便的生成波形和编辑波形。

4) 编译与仿真

Quartus9.1版本软件,当设计文件被编译好,并在波形编辑器中将输入波形编辑完毕后,就可以进行行为仿真了,通过仿真可以检验设计的逻辑关系是否准确。Quartus11.0版本软件没有仿真功能,需要其它仿真软件的支持,例如:Modelsim 软件。

5) 管脚配置

这里需要参考实验板提供的管脚配置TCL脚本文件。开发板实验指导手册中也有介绍。

6) 器件编程下载

当设计全部完成后,就可以将形成的目标文件下载到实验板的FPGA芯片中,实际验证设计的准确性。

[实验步骤]

可以按照电子版的开发板实验指导手册进行学习,熟练掌握Quartus11.0版本软件的开发流程。注意采用的芯片要改为EP2C8Q208C8。

注意事项:请牢记工程未使用到的 IO引脚请设置为三态输入(As input tri-stated),

一定不能将未使用的引脚设置为输出(As outputs driving ground), 否则可能会造成核心板主芯片及存储芯片冲突损坏!或是造成其它意想不到的损坏!

如何设置未使用的引脚为三态?

答:Quartus--菜单 Assignments--Device---Device and Pin Options---Unused

Pins---Reserve all unused pins==改为 As input tri-stated

每个例程下载前都养成习惯,先查下设置对不对,不对的话,改好,要重新编译一下(别

忘记这步!)如果程序下载进去,数码管、LED 灯都乱亮了,那肯定是没设置好,请严格遵照上面的修改好,重新编译!

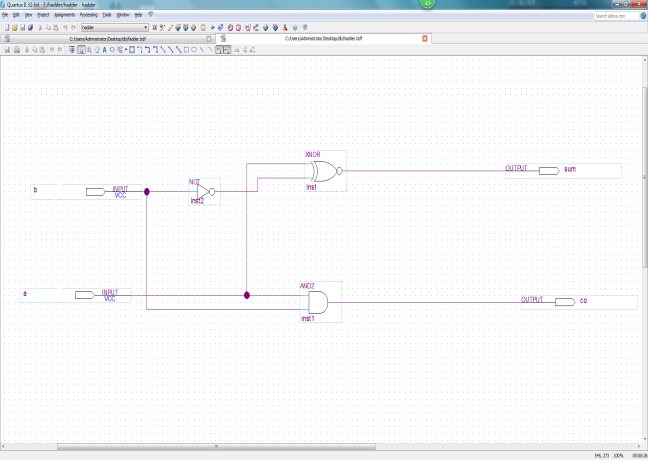

注意:用绘图法设计半加器和全加器来学习软件的操作过程. 半加器电路图如下所示。

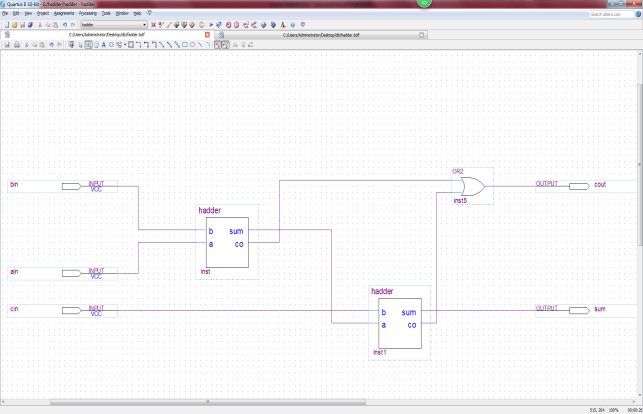

然后生成图形符号再设计全加器。全加器电路图如下所示。

[实验报告]

不做要求。注意实验板的电路原理图要事先看看。

实验二简单组合逻辑电路设计

[实验目的] 1 掌握组合逻辑电路的设计方法。

2 熟悉实验板上FPGA芯片的管脚配置分配表。

[实验内容]

[实验原理]

根据以上组合电路的真值表,利用行为级的编程风格来设计。

[实验步骤]

启动Quartus11.0软件,将编写的设计文件编译后再根据实验板的管脚配置表分配好管脚,最后下载相应的.sof文件测试。注意在选管脚时可以将输入用拨码开关代替,输出可以采用发光二极管代替。

[实验报告]

要求用VHDL语言编程完成以上8-3线优先编码器,3-8译码器的设计,并且比较图形输入法与语言输入法的优劣。

参考程序如下:

(1)3-8译码器

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY YMQ38 IS

PORT (A : IN STD_LOGIC_VECTOR( 2 DOWNTO 0) ;

EN : IN STD_LOGIC ;

Y : OUT STD_LOGIC_VECTOR( 7 DOWNTO 0)) ;

END YMQ38 ;

ARCHITECTURE DEC_BEHAVE OF YMQ38 IS

SIGNAL SEL : STD_LOGIC_VECTOR( 3 DOWNTO 0) ;

BEGIN

SEL(0) <= EN ;

SEL(1) <= A(0) ;

SEL(2) <= A(1) ;

SEL(3) <= A(2) ;

WITH SEL SELECT

Y<= "00000001" WHEN "0001",

"00000010" WHEN "0011",

"00000100" WHEN "0101",

"00001000" WHEN "0111",

"00010000" WHEN "1001",

"00100000" WHEN "1011",

"01000000" WHEN "1101",

"10000000" WHEN "1111",

"11111111" WHEN OTHERS ;

END DEC_BEHAVE;

(2)4-2线优先编码器

library ieee;

use ieee.std_logic_1164.all;

entity encode42 is

port(

d: in std_logic_vector(3 downto 0);

a0n,a1n: out std_logic);

end encode42;

architecture behav of encode42 is

signal q : std_logic_vector(1 downto 0);

begin

a0n<=q(0);a1n<=q(1);

process(d)

begin

if d(3)='0' then

q<="00";

elsif d(2)='0' then

q<="01";

elsif d(1)='0' then

q<="10";

elsif d(0)='0' then

q<="11";

else

q<="00";

end if;

end process;

end behav;

实验三简单时序电路设计

[实验目的]

1、 掌握D触发器的逻辑功能。

2、 掌握简单时序电路的设计方法。

[实验内容]

[实验原理]

1、D触发器:

正沿触发的D触发器的电路符号如下图所示。它是一个正边沿触发的D触发器,有一个数据输入端d,一个时钟输入端clk和一个数据输出端q。D触发器的真值表如下表所示。从表中可以看到,D锁存器的输出端只有在正沿脉冲过后,输入端d的数据才可以传递到输出端q。

表1 D锁存器真值表

2.同步四位加法计数器,要求有使能端控制,enable=1时,开始计数。

[实验步骤]

启动Quartus11.0软件,将编写的设计文件编译后再根据实验板的管脚配置表分配好管脚,最后下载相应的.sof文件测试。注意在选管脚时可以将输入用拨码开关代替,输出可以采用发光二极管代替。

[实验报告]

要求用VHDL语言编程完成D触发器和四位加法计数器的设计。

思考题:能否利用移位寄存器实现八位流水灯的设计电路。

参考程序如下:

(1)D触发器

LIBRARY ieee;

use ieee.std_logic_1164.all;

entity dff1 is

port(clk,d: in std_logic;

q: out std_logic);

end dff1;

architecture dff1_behave of dff1 is

begin

process(clk)

begin

if (clk'event and clk='1') then

q<=d;

end if;

end process;

end dff1_behave;

(2)同步四位加法计数器

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity count4 is

port(clk,en: in std_logic;

qa,qb,qc,qd: out std_logic);

end count4;

architecture behave of count4 is

signal count_6: std_logic_vector(3 downto 0);

signal clk2:std_logic;

begin

process(clk) --分频模块

variable count11:integer range 0 to 2500000;

begin

if clk'event and clk='1' then

if count11=2500000 then

count11:=0;

clk2<=not clk2;

else

count11:=count11+1;

end if;

end if;

end process;

process(clk2)

begin

if (clk2'event and clk2='1') then

if(en='1') then

count_6<=count_6+'1';

end if;

end if;

end process;

qa<=count_6(0);

qb<=count_6(1);

qc<=count_6(2);

qd<=count_6(3);

end behave;

(3) 设计参考程序:流水灯的控制电路。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; --这3个程序包足发应付大部分的VHDL程序设计

USE IEEE.STD_LOGIC_Arith.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

USE IEEE.NUMERIC_STD.ALL;

ENTITY ledwater IS

PORT(clk: IN STD_LOGIC;

led: OUT STD_LOGIC_VECTOR(8 DOWNTO 1));

END;

ARCHITECTURE one OF ledwater IS

signal led_r: std_logic_vector(9 downto 1);

signal clk2:std_logic;

BEGIN

led<=led_r(8 DOWNTO 1);

process(clk) --分频模块

variable count11:integer range 0 to 2500000;

begin

if clk'event and clk='1' then

if count11=2500000 then

count11:=0;

clk2<=not clk2;

else

count11:=count11+1;

end if;

end if;

end process;

PROCESS(clk2)

BEGIN

IF RISING_EDGE(clk2) THEN

led_r<=led_r(8 DOWNTO 1) & '0';

IF led_r="000000000" THEN--循环完毕吗?

led_r<="111111111";--是,则重新赋初值

END IF;

END IF;

END PROCESS;

END;

实验四LED显示译码电路的设计

[实验目的]

- 掌握LED显示译码电路的设计。

- 熟悉用数码管实现十六进制计数的动态显示原理。

[实验内容]

- 编写能够同时在八个数码管上轮换显示0~F十六进制数的电路。

- 编写能够用动态扫描方式显示数字:12345678的电路。

[实验原理]

用数码管除了可以显示0~9的阿拉伯数字外,还可以显示一些英语字母。在实验电路板的原理图上要分析出数码管是共阴极接法还是共阳极接法。

[实验步骤]

启动Quartus11.0软件,将编写的设计文件编译后再根据实验板的管脚配置表分配好管脚,最后下载相应的.sof文件测试。

[实验报告]

要求用VHDL语言编程完成以上LED显示译码器与动态扫描电路的设计。

思考题:如何实现一个N(偶数)分频器的设计。

(1)0~F计数显示电路。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY sled IS

PORT(clk:IN STD_LOGIC;

dig: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

seg: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --七段译码输出

END;

ARCHITECTURE ONE OF sled IS

signal seg_r:STD_LOGIC_VECTOR(7 DOWNTO 0); --定义数码管输出寄存器

signal count_4: std_logic_vector(3 downto 0);

signal clk2:STD_LOGIC;

BEGIN

seg<=seg_r; --输出数码管译码结果

dig<="00000000";

process(clk) --分频器

variable count11:integer range 0 to 25000000;

begin

if clk'event and clk='1' then

if count11=25000000 then

count11:=0;

clk2<=not clk2;

else

count11:=count11+1;

end if;

end if;

end process;

process(clk2)

begin

if (clk2'event and clk2='1') then

count_4<=count_4+'1';

end if;

end process;

PROCESS(count_4) --七段译码

BEGIN

CASE count_4 IS

WHEN X"0"=> seg_r<=X"c0";--显示0

WHEN X"1"=> seg_r<=X"f9";--显示1

WHEN X"2"=> seg_r<=X"a4";--显示2

WHEN X"3"=> seg_r<=X"b0";--显示3

WHEN X"4"=> seg_r<=X"99";--显示4

WHEN X"5"=> seg_r<=X"92";--显示5

WHEN X"6"=> seg_r<=X"82";--显示6

WHEN X"7"=> seg_r<=X"f8";--显示7

WHEN X"8"=> seg_r<=X"80";--显示8

WHEN X"9"=> seg_r<=X"90";--显示9

WHEN X"a"=> seg_r<=X"88";--显示a

WHEN X"b"=> seg_r<=X"83";--显示b

WHEN X"c"=> seg_r<=X"c6";--显示c

WHEN X"d"=> seg_r<=X"a1";--显示d

WHEN X"e"=> seg_r<=X"86";--显示e

WHEN X"f"=> seg_r<=X"8e";--显示f

WHEN OTHERS=> seg_r<=X"FF";

END CASE;

END PROCESS;

END;

(2)动态扫描显示数字:12345678电路设计。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity dled is

port(

clk:in std_logic;

dig:out std_logic_vector(7 downto 0); --数码管选择输出引脚

seg:out std_logic_vector(7 downto 0) ); --数码管段输出引脚

end entity;

architecture one of dled is

constant d: std_logic_vector(31 downto 0):= x"12345678";

signal seg_r: std_logic_vector(7 downto 0); --定义数码管输出寄存器

signal dig_r: std_logic_vector(7 downto 0); --定义数码管选择输出寄存器

signal disp_dat: std_logic_vector(3 downto 0); --定义显示数据寄存器

signal count: std_logic_vector(2 downto 0); --定义计数寄存器

signal clk_1k: std_logic;

begin

dig<=dig_r;

seg<=seg_r;

process(clk)

variable count11:integer range 0 to 25000;

begin

if clk'event and clk='1' then

if count11=25000 then

count11:=0;

clk_1k<=not clk_1k;

else

count11:=count11+1;

end if;

end if;

end process;

process(clk_1k)

begin

if rising_edge(clk_1k) then

count<=count+1;

end if;

end process;

PROCESS(clk_1k)

BEGIN

IF rising_edge(clk_1k) THEN

CASE count IS

WHEN "000"=> disp_dat<=d(31 DOWNTO 28); --第一个数码管

WHEN "001"=> disp_dat<=d(27 DOWNTO 24); --第二个数码管

WHEN "010"=> disp_dat<=d(23 DOWNTO 20); --第三个数码管

WHEN "011"=> disp_dat<=d(19 DOWNTO 16); --第四个数码管

WHEN "100"=> disp_dat<=d(15 DOWNTO 12); --第五个数码管

WHEN "101"=> disp_dat<=d(11 DOWNTO 8); --第六个数码管

WHEN "110"=> disp_dat<=d(7 DOWNTO 4); --第七个数码管

WHEN "111"=> disp_dat<=d(3 DOWNTO 0); --第八个数码管

END CASE;

CASE count IS --选择数码管显示位

WHEN "000"=> dig_r<="01111111"; --选择第一个数码管显示

WHEN "001"=> dig_r<="10111111"; --选择第二个数码管显示

WHEN "010"=> dig_r<="11011111"; --选择第三个数码管显示

WHEN "011"=> dig_r<="11101111"; --选择第四个数码管显示

WHEN "100"=> dig_r<="11110111"; --选择第五个数码管显示

WHEN "101"=> dig_r<="11111011"; --选择第六个数码管显示

WHEN "110"=> dig_r<="11111101"; --选择第七个数码管显示

WHEN "111"=> dig_r<="11111110"; --选择第八个数码管显示

END CASE;

END IF;

END PROCESS;

PROCESS(disp_dat)

BEGIN

CASE disp_dat IS

WHEN X"0"=> seg_r<=X"c0";--显示0

WHEN X"1"=> seg_r<=X"f9";--显示1

WHEN X"2"=> seg_r<=X"a4";--显示2

WHEN X"3"=> seg_r<=X"b0";--显示3

WHEN X"4"=> seg_r<=X"99";--显示4

WHEN X"5"=> seg_r<=X"92";--显示5

WHEN X"6"=> seg_r<=X"82";--显示6

WHEN X"7"=> seg_r<=X"f8";--显示7

WHEN X"8"=> seg_r<=X"80";--显示8

WHEN X"9"=> seg_r<=X"90";--显示9

WHEN X"a"=> seg_r<=X"88";--显示a

WHEN X"b"=> seg_r<=X"83";--显示b

WHEN X"c"=> seg_r<=X"c6";--显示c

WHEN X"d"=> seg_r<=X"a1";--显示d

WHEN X"e"=> seg_r<=X"86";--显示e

WHEN X"f"=> seg_r<=X"8e";--显示f

END CASE;

END PROCESS;

END;

实验五数字钟设计

[实验目的]

1. 掌握多位计数器相连的设计方法。

2. 掌握十进制、六十进制、二十四进制计数器的设计方法。

3. 掌握喇叭的驱动方法。。

4. 掌握层次化设计方法。

[实验内容]

1. 具有时、分、秒计数显示功能,以24小时循环计时。

2. 具有清零,调节小时、分钟的功能。

3. 具有整点报时功能,整点报时的同时LED灯花样显示。

[实验原理]

在同一块FPGA芯片集成了如下电路模块:

1. 时钟计数:秒——60进制BCD码计数;分——60进制BCD码计数;时——24进制BCD码计数;同时整个计数器有清零,调分,调时功能。在整点时间能提供报时信号。

2. 有驱动8位七段共阴极扫描数码管的片选驱动信号输出和七段字行译码输出。

3. 喇叭在整点时有报时驱动信号产生。

4. LED灯根据设计在整点时有花样显示信号产生。

[实验步骤]

1、启动Quartus11.0软件,将编写的设计文件编译后再根据实验板的管脚配置表分配好管脚,最后下载相应的.sof文件测试

实验现象:当程序下载完毕后数码管从00时00分00秒开始计时,通过按键K1可以调节时钟的分钟显示,通过按键K2可以调节时钟的小时显示。当时钟走到整点时,喇叭开始鸣叫1分钟,发光二极管LED1~LED3循环闪烁。

[实验报告]

1. 画出整个数字钟电路的结构框图。

2. 用VHDL语言完成顶层图形文件中各个子模块的设计。如果设计中的某些模块在以前

的实验中使用过,该模块可以不要再写,例如LED显示译码器。

实验六频率计设计

[实验目的]

1、掌握多位计数器相连的设计方法。

2、掌握频率计的工作原理。

3、掌握EDA技术的层次化设计方法。

[实验内容]

设计一个频率计,其测频范围为1HZ<f<50MHz.。

[实验原理]

本实验所设计的频率计由三个模块组成:测频控制信号发生器TESTCTL、8个有时钟使能的十进制计数器CNT10和一个32位锁存器REG32B。以下分别叙述频率计各个逻辑模块的功能与设计方法。

测频控制信号发生器的设计要求:频率测量的基本原理是计算每秒钟内待测信号的脉冲个数。这就要求TESTCTL的计数使能信号TSTEN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的ENA使能端进行同步控制。当TSTEN为高电平时,允许计数;为低电平时停止计数,并保持其所计的脉冲个数。在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的计数值锁存进32位锁存器REG32B中,并由外部的7段译码器译出,并稳定显示。设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。锁存信号之后,必须有一个清零信号CLR_CNT对计数器进行清零,为下1秒钟的计数操作作准备。测频控制信号发生器的工作时序如下图所示。为了产生这个时序图,需首先建立一个由D触发器构成的二分频器,在每次时钟CLK上升沿到来时其值翻转。

其中控制信号时钟CLK的频率取1HZ,那么信号TSTEN的脉宽恰好为1S,可以用作计数闸门信号。然后根据测频的时序要求,可得出信号LOAD和CLR_CNT的逻辑描述。由上图可见,在计数完成后,即计数使能信号TSTEN在1S的高电平后,利用其反相值的上跳沿产生一个锁存信号LOAD,0.5S后,CLR_CNT产生一个清零信号上跳沿。高质量的测频控制信号发生器的设计十分重要,设计中要对其进行仔细的实时防真,防止可能产生的毛刺。

寄存器REG32B设计要求:若已有32位BCD码存在于此模块的输入口,在信号LOAD的上升沿后即被锁存到寄存器REG32B的内部,并由REG32B的输出端输出,然后由实验板上的7段译码器译成能在数码管上显示输出的相应数值。

计数器CNT10设计要求:此十进制计数器的特殊之处是,有一时钟使能输入端ENA,用于锁定计数值。当高电平时计数允许,低电平时禁止计数。

[实验步骤]

1. 启动Quartus11.0软件,将编写的设计文件编译后再根据实验板的管脚配置表分配好管脚,最后下载相应的.sof文件测试。

2. 注意要测量的信号源可以采用多个分频器实现。做实验时可以选择分频器的一个输出信号进行测试。

[实验报告]

1、画出设计的顶层文件原理图。

2、对照频率计波形图分析电路工作原理。

3、写出各功能模块的VHDL语言源程序,并且给出相应的注释。如果设计中的某些模块

在以前的实验中使用过,该模块可以不要再写,例如LED显示译码器,LED位选扫描产生电路。

实验七 乐曲演奏电路设计

[实验目的]

1. 了解乐曲演奏电路的原理。

2. 掌握利用可编程逻辑器件实现乐曲演奏的设计方法。

[实验内容]

用VHDL语言设计一个“梁祝”乐曲演奏电路。

[实验原理]

与利用微处理器(CPU或MCU)来实现乐曲演奏相比,以纯硬件完成乐曲演奏电路的逻辑要复杂得多,如果不借助于功能强大的EDA工具和硬件描述语言,仅凭传统的数字逻辑技术,即使最简单的演奏电路也难以实现。

本实验设计项目作为“梁祝”乐曲演奏电路的实现,其工作原理是这样的:我们知道,组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能连续演奏所需的两个基本要素,问题是如何来获取这两个要素所对应的数值以及通过纯硬件的手段来利用这些数值实现所希望乐曲的演奏效果。

本实验设计由四个模块组成,其每一个模块的功能如下所述。模块一为一个数控分频器SPEAKERA,其CLK端输入一具有较高频率(本实验为1MHz)的信号,通过SPEAKERA分频后由SPKOUT输出。由于直接从数控分频器中出来的输出信号是脉宽极窄的脉冲式信号,为了有利于驱动喇叭,需另加一个D触发器以均衡其占空比,但这时的频率将是原来的1/2。SPEAKERA对CLK输入信号的分频比由11位预置数TONE[10..0]决定。SPKOUT的输出频率将决定每一音符的音调,这样分频计数器的预置值TONE[10..0]与SPKOUT的输出频率就有了对应关系。例如在TONETABA模块中若取TONE[10..0]=1036,将发音符为“3”音的信号频率。

模块二TONETABA是确定乐曲的速度以及每个音符的节拍数。TONETABA的功能首先是为SPEAKERA提供决定所发音符的分频预置数,而此数在SPEAKERA输入口停留的时间即为此音符的节拍值。模块TONETABA是乐曲简谱码对应的分频预置数查表电路,其中设置了“梁祝”乐曲全部音符所对应的分频预置数,共13个,每一音符的停留时间由音乐节拍和音调发生器模块NOTETABS的CLK的输入频率决定,在此为4Hz。这13个值的输出由对应于TONETABA的4位输入值Index[3..0]确定,而Index[3..0]最多有16种可选值。输向TONETABA中的值ToneIndex[3..0]的输出值与持续的时间由模块NOTETABS决定。

模块三NOTETABS为音调发生器,在NOTETABS中设置了一个8位二进制计数器(计数最大值为138),这个计数器的计数频率选为4Hz,即每一计数值的停留时间为0.25S,恰为当全音符设为1S时,四四拍的4分音符的持续时间。例如,NOTETABS在以下的VHDL逻辑描述中,“梁祝”乐曲的第一个音符为“3”,此音在逻辑中停留了4个时钟节拍,即为1S时间,相应地所对应的“3”音符分频预置值为1036在SPEAKERA的输入端停留了1S。随着NOTETABS中的计数器按4Hz的时钟频率作加法计数时,“梁祝”乐曲就开始连续自然地演奏起来了。

模块四fengping是个分频器,实现将50MHZ的时钟生成1MHZ和4HZ的时钟。

下表为简谱中音名与频率的关系:

[实验步骤]

启动Quartus11.0软件,将编写的设计文件编译后再根据实验板的管脚配置表分配好管脚,最后下载相应的.sof文件测试,下载完毕后就开始连续演奏“梁祝”乐曲,

[实验报告]

1、画出设计的顶层设计原理图。

2、写出原理图中各功能模块的VHDL语言源程序并加上注释。模块三NOTETABS音调发生

器的“梁祝”乐曲音符可以压缩写三行即可。

思考题:如何设计一个简易电子琴控制器。

实验八抢答器设计

[实验目的]

1. 熟悉四路抢答器的工作原理。

2. 了解原理图、VHDL语言层次化设计方法。

[实验内容]

设计一个四人抢答器电路。

[实验原理]

(1) 设计制作一个可容纳四组参赛者的数字智力抢答器,每组设置一个抢答按钮供抢答者使用。

(2) 电路具有第一抢答信号的鉴别和锁存功能。

(3) 设置计分电路。

(4) 设置犯规电路。

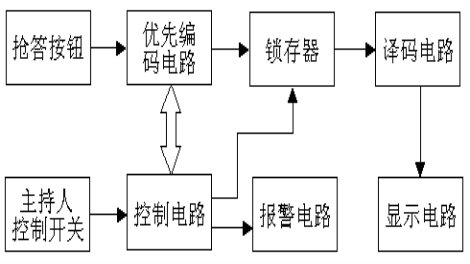

一般说来,多路智力竞赛抢答器的的组成框图为:

图1 多路智力竞赛抢答器的的组成框图

其工作过程是:接通电源下载完毕后,节目主持人将开关置于清除位置,抢答器处于禁止工作状态,编号显示器数码管熄灭,当节目主持人宣布抢答开始并将开关置于开始位置,抢答器处于工作状态,当选手按键抢答时,优先编码器立即分辨出抢答器的编号,并由锁存器锁存,然后由编码显示电路显示编号,同时,控制电路对输入编码进行封锁,避免其他选手再次进行抢答。当选手将问题回答完毕,主持人操作控制开关,对选手进行加分,再使系统恢复到禁止工作状态,以便进行下一轮的抢答。

[实验步骤]

启动Quartus11.0软件,将编写的设计文件编译后再根据实验板的管脚配置表分配好管脚,最后下载相应的.sof文件测试。

[实验报告]

画出本实验电路的原理图和并给出相应模块的VHDL语言源程序。如果设计中的某些模块

在以前的实验中使用过,该模块可以不要再写,例如LED显示译码器,LED位选扫描产生电路等。

实验九交通灯控制器设计(课程设计:题目可自选)

[设计目的]

掌握VHDL语言的层次化设计方法,自己设计简单的交通灯控制器电路。

[设计内容]

1、能显示十字路口东西、南北两个方向的红、黄、绿灯的指示状态。

2、用两组红、黄、绿三色灯作为两个方向的红、黄、绿灯。能实现正常的倒计时功能以及用两组数码管作为东西和南北方向的倒计时显示。

3、用VHDL语言设计符合上述功能要求的交通灯控制器,并用层次化设计方法设计该电路。

[实验原理]

以下给出了本设计的一个演示实例:首先必须了解交通路灯的燃灭规律。本实例需要用到实验箱上交通灯模块中的发光二极管,即红、黄、绿各三个。依人们的交通常规,“红灯停,绿灯行,黄灯提醒”。其交通灯的燃灭规律为:初始态是两个路口的红灯全亮,之后,东西路口的绿灯亮,南北路口的红灯亮,东西方向通车,延时一段时间后,东西路口绿灯开始闪烁,一段时间后绿灯灭,黄灯开始闪烁。闪烁若干次后,东西路口红灯亮,同时南北路口的绿灯亮,南北方向开始通车,延时一段时间后,南北路口的绿灯开始闪烁,一段时间后绿灯灭,黄灯开始闪烁。闪烁若干次后,再切换到东西路口方向,重复上述过程。该控制器可以采用有限状态机来实现。

[实例演示步骤]

1. 启动Quartus11.0软件,将编写的设计文件编译后再根据实验板的管脚配置表分配好管脚,最后下载相应的.sof文件测试。

实验现象:程序下载完毕后,首先东西方向通行,当数码管倒计时计到还剩5秒时绿灯开始闪烁,当计到1秒时黄灯开始闪烁,0秒过后转向南北方向通行。其现象与东西向一致,

15秒后又转向东西向通行。以后都重复上述过程。

[设计报告]

1、课程设计题目可以自由选取,按照课程设计的规范要求进行设计报告的撰写。

2、书写设计报告时应结构合理,层次分明,在分析时注意语言的流畅。

3、要给出完整的设计过程和设计源码,并且要在实验箱上进行实物验证。

-

-

新版EDA实验指导书.docx

341.28 KB, 下载次数: 53, 下载积分: 黑币 -5

作者: Wikkings_Bob 时间: 2019-5-7 22:59

太给力了,我们正在学!

| 欢迎光临 (http://www.51hei.com/bbs/) |

Powered by Discuz! X3.1 |