(1)计时部分由0.1s位、s个位、s十位和min个位四个计数器组成。其中min个位、0.1s位分别为8421BCD码十进制计数器,个位和十位组成六十进制8421BCD码计数器。计数范围0~10min,精度为0.1s。

(2)用一个按键实现清零、计时、停止三种工作状态。当按键第一次按下时,秒表开始计时;第二次按下时,秒表停止计时。按键按下超过2s,则秒表清零。

(3)脉冲源可通过555多谐振荡器提供。

首先,需要一准确的时钟脉冲,脉冲频率为10Hz。在一般教学实验箱中有连续可调的时钟脉冲,而在Multisim软件中可用模拟的信号发生器,为了进一步熟悉和应用数字电路模块,我们模拟应用了555多谐振荡器。而开关控制电路,用集成D触发器作为控制电路。最后,需要显示电路,显示电路输出结果。

三、选择器件

1.电子秒表所用全部的器件如表1元器件清单所示。

表1 元器件清单

序号 | 名称 | 型号 | 数量 | 备注 |

1 | 计数器 | 74LS192 | 5 | —— |

2 | 555定时器 | NE555 | 1 | —— |

3 | 与非门 | 74LS00 | 2 | —— |

4 | 或非门 | 74LS02 | 1 | —— |

5 | 开关 | SPST | 1 | —— |

6 | 电阻

| RESISTOR | 1 | 5.1KΩ |

7 | 1 | 4.7KΩ | ||

8 | 2 | 10.0KΩ | ||

9 | 电容 | CAP | 1 | 10uF |

10 | 1 | 100nF | ||

11 | D触发器 | 74LS279 | 1 | —— |

12 | 七段译码显示器 | DCD-HEX | 4 | —— |

13 | 译码器 | 74LS248 | 4 | —— |

2.用555定时器构成方波发生器

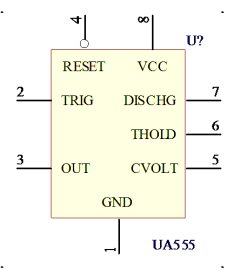

555定时器引脚排列及功能表如图2所示。

图2 555定时器引脚排列及功能表

它的各个引脚功能如下:

1脚:外接电源负端VSS或接地,一般情况下接地。

8脚:外接电源VCC,双极型时基电路VCC的范围是4.5 ~ 16VCMOS型时基电路VCC的范围为3 ~ 18V。一般用5V。

3脚:输出端Vo

2脚:![]() 低触发端

低触发端

6脚:TH高触发端

4脚:![]() 是直接清零端。当

是直接清零端。当![]() 端接低电平,则时基电路不工作,此时不论

端接低电平,则时基电路不工作,此时不论![]() 、TH处于何电平,时基电路输出为“0”,该端不用时应接高电平。

、TH处于何电平,时基电路输出为“0”,该端不用时应接高电平。

5脚:VC为控制电压端。若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF电容接地,以防引入干扰。

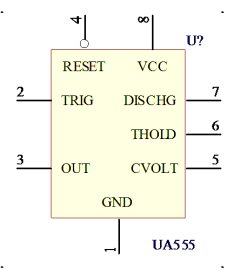

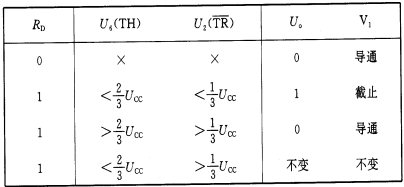

7脚:放电端。该端与放电管集电极相连,用做定时器时电容的放电。 在1脚接地,5脚未外接电压,两个比较器A1、A2基准电压分别为![]() 的情况下,555时基电路的功能表如下表2所示。

的情况下,555时基电路的功能表如下表2所示。

3. D触发器

下图4是具有异步置位和复位端的边沿触发双D触发器74LS74的引脚排列图。

由图可知,异步置位和复位信号不仅直接触发从触发器,而且封锁同步输入端D和时钟端CLK,所以异步置位和复位在有效电平时,能够使同步输入端的作用失效。

图4 D触发器74LS74的引脚排列图

下表表3是74LS74的特性表。由表可知,异步输入端电平有效时,同步输入端D与时钟端CLK的作用无效。

输 入 | 输 出 | 说 明 |

Qn+1 | ||

0 1 × × 1 0 × × 0 0 × × 1 1 ↑ 0 1 1 ↑ 1 1 1 0 × | 1 0 1 0 1 Q0 | 预置1 预置零 不允许 置零 置1 保持 |

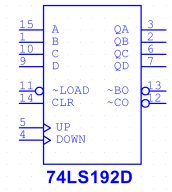

4.计数器芯片 (74LS192)

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下图5、表4所示。

图5 74LS192的管脚图

表4 74LS192的功能表

输入 | 输出 | ||||||||||

MR |

|

|

| P3 | P2 | P1 | P0 | Q3 | Q2 | Q1 | Q0 |

1 | × | × | × | × | × | × | × | 0 | 0 | 0 | 0 |

0 | 0 | × | × | d | c | b | a | d | c | b | a |

0 | 1 |

| 1 | × | × | × | × | 加计数 | |||

0 | 1 | 1 |

| × | × | × | × | 减计数 | |||

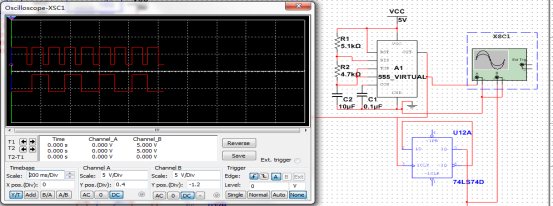

1.555时钟发生模块设计

利用555定时器实现多谐振荡电路能够完成时钟信号发生器的功能,通过调节电路中电阻电容值使多谐振荡器的输出信号频率为10Hz。为设计方便,取R1=5.1![]() ,R2=4.7

,R2=4.7![]() 电阻,C=10uF 构成一个能产生周期为0.1s(频率为10Hz)的脉冲的多谐振荡器。如图6所示。

电阻,C=10uF 构成一个能产生周期为0.1s(频率为10Hz)的脉冲的多谐振荡器。如图6所示。

图6 多谐振荡器

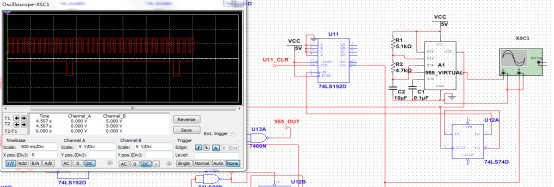

2. 控制模块

控制部分用按键、D触发器和与非门、或非门实现。

一个D触发器二分频和一个192十分频 用来对时间信号二十分频,产生一个周期为两秒的清零信号,如图7所示。

图7 二分频 十分频

另一个D触发器对按键信号二分频,产生两种状态,用来控制暂停和开始。

用与非门和或非门来判断并处理按键的状态,进而控制开始,暂停,清零状态。

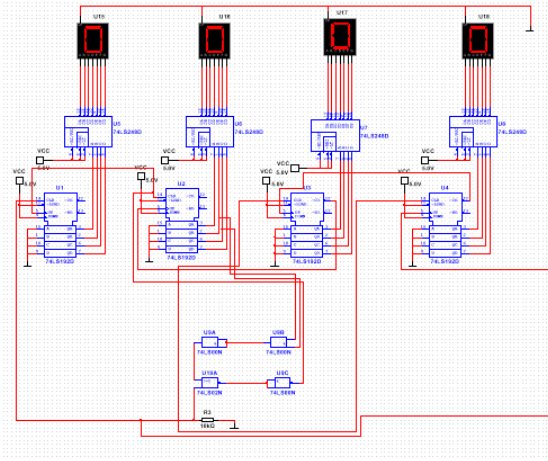

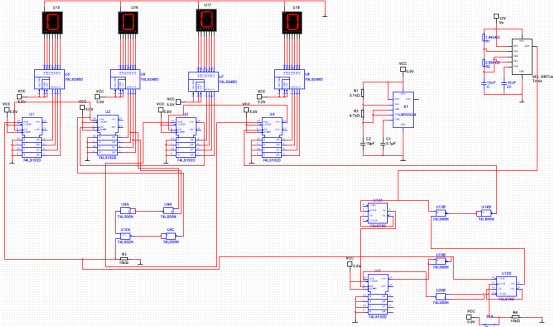

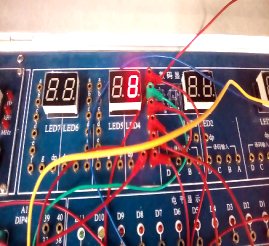

3.输出及显示模块

利用4个74LS192分别连接成六十进制、十制计数器,每一片计数器负责计数一位时间,并通过74LS248连接四个数码显示器显示0——9分59秒9的秒表数值。其中将基准脉冲信号源输出的所需脉冲接入第一个芯片的时钟输入端,并将第一个芯片的四个对应输出接入相应的数码显示器的相应端,构成秒表的小数部分。第一个芯片的进位输出端再接入第二个芯片的时钟输入端,同第一片芯片,构成电子秒表的个位显示,同理连接第三个芯片,构成电子秒表的十位显示,以此类推。输出及显示模块电路原理图如图8所示。

利用D触发器两种不同的输入状态来控制秒表,模拟电子秒表的按钮,实现开始计数,停止并保持计数和清零重新开始计数。用555实现脉冲时钟输出10HZ,周期为0.1s的计数脉冲,利用译码/驱动电路输出显示在数码电路输出显示在数码管,数码管显示电子秒表的0——9分59秒9。

电子秒表(二).doc

(1.55 MB, 下载次数: 95)

电子秒表(二).doc

(1.55 MB, 下载次数: 95)

| 欢迎光临 (http://www.51hei.com/bbs/) | Powered by Discuz! X3.1 |