实验一:

LED实验

一、实验目的- 熟悉ISE8.2开发环境,掌握工程的生成方法;

- 熟悉SEED-XDTK_V4实验环境;

二、实验内容- 创建工程;

- 添加HDL资源文件;

- 配置一个应用程序完成设计。

三、实验准备- 通过USB口下载电缆将计算机的USB口及SEED-FEM025板的J9 连接好;

- 启动计算机,打开SEED-XDTK_V4实验箱电源开关。观察SEED-FEM025板上的+5V(D11)的电源指示灯是否均亮。若有不亮的,请断开电源,检查电源。

四、实验步骤- 双击桌面Xilinx ISE8.2快捷方式打开ISE工程管理器(Project Navigator);

- 打开Project Navigator后,选择File → New Project,弹出新建工程对话框;

- 在工程路径中单击“…”按钮,将工程指定到如下目录D: \02. V4_lab,单击确定;

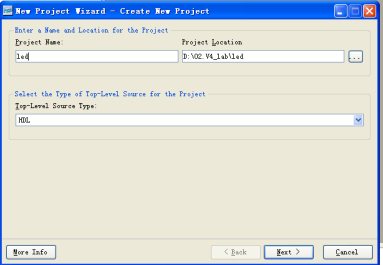

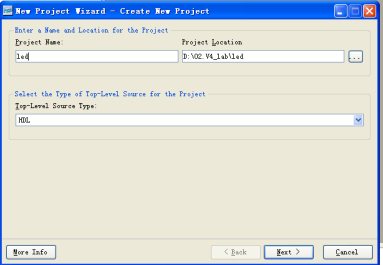

- 在工程名称中输入led,点击Next按钮,如图1.1所示;

图1.1

- 弹出器件特性对话框。器件族类型(Device Family)选择“Virtex4”,器件型号(Device)选“XC4VSX25 FF668 -10”,综合工具(Synthesis Tool)选“XST (VHDL/Verilog)”,仿真器(Simulator)选“ISE Simulator”,如图1.2;

图1.2

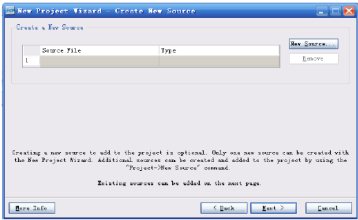

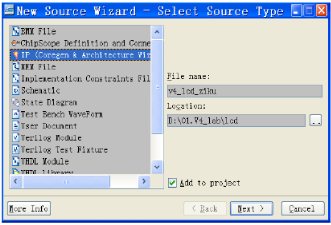

- 单击Next按钮,弹出创建新资源(Create New Soure)对话框,可以使用这个对话框来创建新的HDL资源文件,或者也可以创建工程后,新建HDL资源文件,如图1.3;

图1.3

- 单击Next按钮,弹出添加存在资源对话框;可以使用这个对话框来添加已经存在的HDL资源文件,或者也可以创建工程后,添加HDL资源文件;在本实验中我们采用创建工程后,添加HDL资源文件的方式,如图1.4;

图1.4

- 单击Next按钮,将弹出工程建立完成对话框,单击finish按钮完成工程建立流程;

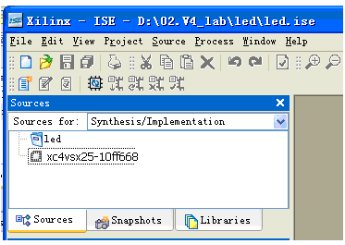

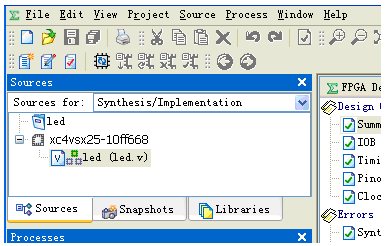

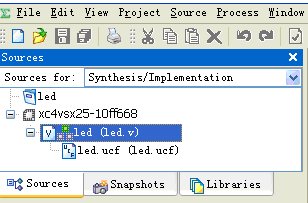

- 观察工程资源管理窗口,将会看到工程已经建立成功,如图1.5。

图1.5

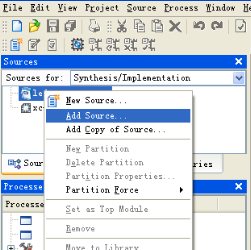

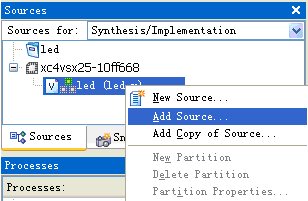

- 选择Project → Add Source命令,弹出的文件添加对话框;或者右键单击Sources中的led弹出的文件添加对话框,如图1.6;

图1.6

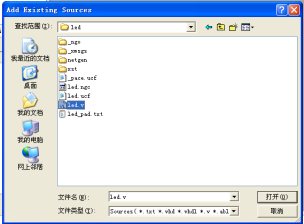

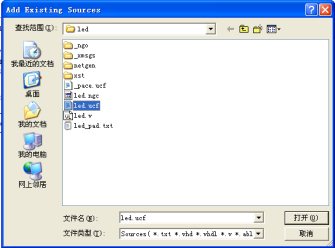

- 在弹出的对话框中将文件添加路径指向D:\02.V4_lab.2\led文件夹下,选择led.v文件,单击Open按钮,如图1.7;

图1.7

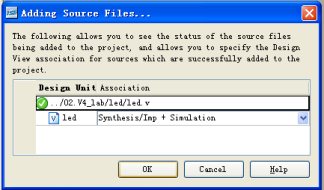

图1.8

图1.9

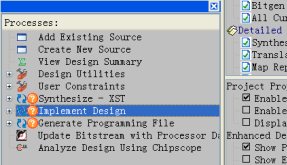

- 在工程的资源操作窗(Processes),双击Implement Design; 如图1.10

图1.10

- 当设计实现(Implement Design)运行的过程中,展开设计实现命令(Implement Design),会看到实现过程中,首先是进行综合(Synthesis),然后才依次完成实现的步骤。

- 工程的Sources窗口,右键单击Sources中的led.v文件,弹出的文件添加对话框,如图1.11;

图1.11

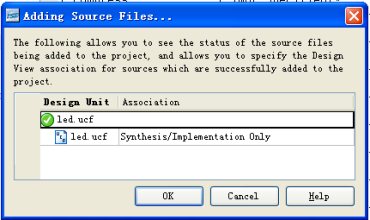

- 添加led.ucf文件,顺序与上述添加HDL资源文件相类似如图1.12-1.14;

图1.12 鼠标左键单击“打开(O)”

图1.13 鼠标左键单击“OK”

图1.14 鼠标左键单击“led左侧+”

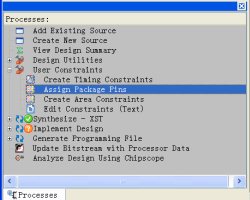

- 在Processes窗口,扩展User Constraints并双击Assign Package Pins打开PACE,如图1.15;注意在PACE能启动之前必须先进行综合。

图1.15

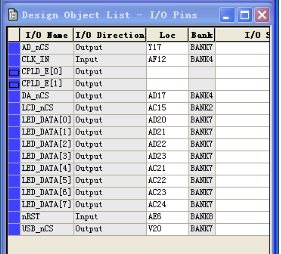

- 在PACE中浏览Design Object List-I/O Pins窗口,可看到所列的信号名称和信号方向是Output还是Input。在Loc栏里每个信号对应的FPGA的管脚。信号连接如下,在FPGA的管脚分配需查看原理图,如图1.16;

CLK_IN: 管脚编号为AF12

LED_DATA[0]: 管脚编号为AD20

其余管脚在此就不一一列出了。

图1.16

- 在所有信号链接完成后,然后选择保存文件,如图1.17箭头所示位置;

图1.17

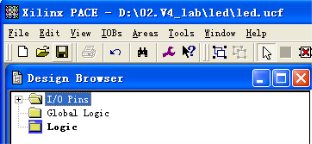

- 在Device Architecture窗口放大直到可以看清每个管脚;如图1.18;

注意:图中粉红色彩条说明管脚在同一个bank中。单击每个蓝色I/O管脚,则对应着Design Object List-I/O Pins窗口相应的管脚。

图1.18

- 单击菜单栏中的File → Exit,退出PACE;

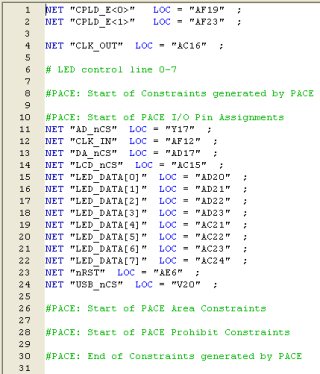

- 单击工程中Sources窗口中的led.ucf文件,然后双击Prosesses窗口中User Constraints目录下的Edit Constraints (Text),就可以看到由PACE生成的led.ucf管脚约束文件;当然我们也可以使用该命令,直接在文本中编写led.ucf文件;

图1.19

- 在工程的资源操作窗(Processes),双击Implement Design;对设计重新实现;

- 本例程中led.ucf文件早已存在,我们可以使用上文介绍过的文件添加方式将led.ucf文件直接添加到工程文件中。

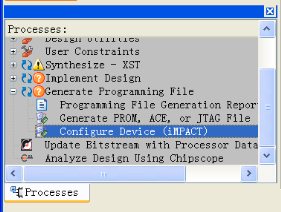

- 在工程的Sources窗口单击顶层文件LED.v文件,展开Processes窗口中的Generate Programming File,双击Configure Device (iMPACT),如图1.20;

图1.20

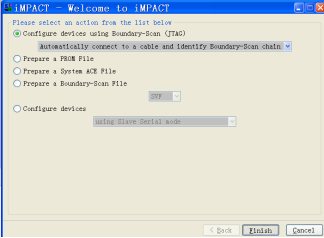

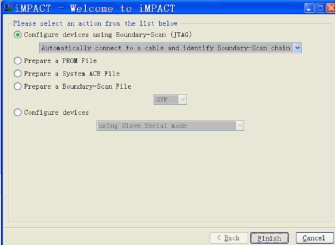

- 弹出Welcome iMPACT对话框后,选择“Configure devices using Boundary-Scan(JTAG)”,单击Finish按钮,如图1.21;

图1.21

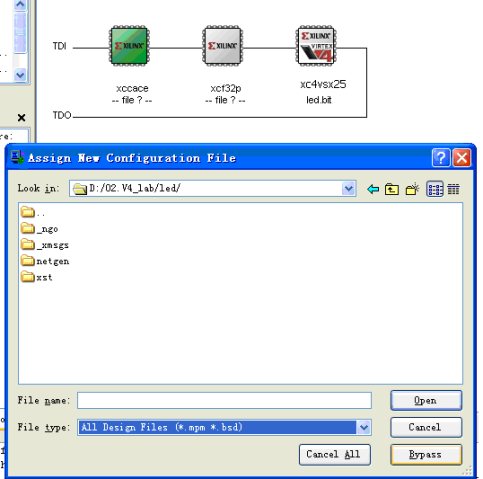

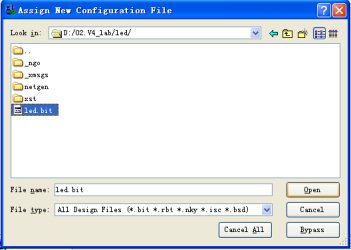

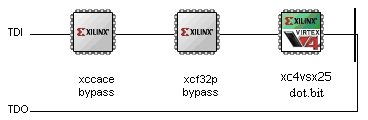

- 在弹出的器件添加对话中,第一个器件选择bypass按钮,如图1.22;第二个器件也选择bypass按钮,如图1.23;

图1.22

图1.23

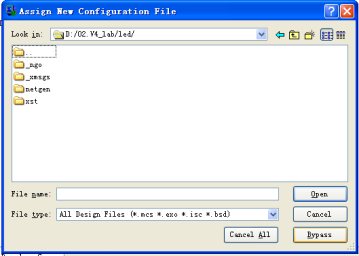

- 最后一个器件单击所要下载的led.bit文件(此文件所在目录不可有中文),单击Open按钮,如图1.24;会弹出如图1.25的“Add Virtex-/II Pro/Virtex04...”对话框,单击OK按钮后弹出一个警告信息,单击OK按钮;

图1.24

图1.25

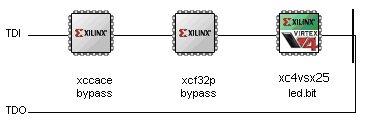

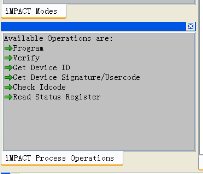

- 单击xc4vsx25这个device,变成绿色,且 iMPACT Processes Operations窗口出现可执行的操作; 如图1.26和1.27

图1.26

图1.27

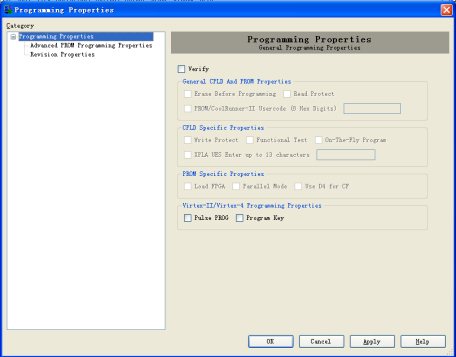

- 在图1.27中,双击iMPACT Processes Operations窗口中的Program,或者在图1.26中,直接右键单击xc4vsx25这个device,选择Program。会弹出Programming Properties对话框,如图1.28所示,单击OK按钮;

图1.28

程序开始下载,如果下载程序成功则出现Program Succeeded,否则如果失败则出现Program Failed,需要重新查找问题(尝试重新下载或者断电后重新下载程序);

- 程序下载成功后,可观察到SEED-XDTK_MBOARD板卡上LED灯依次点亮。

五、实验程序led.v

六、思考题:- FPGA的中英文全称各是什么?

- 实验箱所用FPGA型号是什么?共有多少个引脚?引脚可以分为哪几类?

- 概述对FPGA进行编程下载的流程。

- 实验程序中,输入输出引脚各有几个?两个always块语句各自的作用是什么?

实验二:LED点阵实验一、实验目的- 熟悉ISE8.2开发环境,掌握工程的生成方法;

- 熟悉SEED-XDTK_V4实验环境;

- 了解HDL语言在FPGA中的使用;

- 了解定时器的HDL实现。

二、实验内容三、实验说明本实验的功能是将SEED-XDTK_MBOARD板上LED点阵点亮(合众达图标)。根据硬件原理,通过对FPGA的输入时钟进行分频,实现一个定时器,该定时器主要用于定时扫描控制SEED-XDTK_MBOARD板卡上的LED点阵。

SEED-XDTK_MBOARD板上LED点阵共有16*16点,既有16根控制线与16根数据线。 控制线用来选中一组LED灯,16根数据线用来点亮相应的LED灯。

四、实验准备1. 通过USB 口下载电缆将计算机的USB 口及SEED-FEM025 板的J9 连接好;

2. 启动计算机,打开SEED-XDTK_V4 实验箱电源开关。观察SEED-FEM025 板上的+5V(D11)的电源指示灯是否均亮。若有不亮的,请断开电源,检查电源。

五、实验步骤注意:选择器件(Device)为“XC4VSX25 FF668 -10”

其他步骤同实验一,请参考。

- 双击Configure Device (iMPACT)命令,打开iMPACT窗口;

- 弹出Welcome iMPACT对话框后,选择“Configure devices using Boundary-Scan(JTAG)”,单击Finish按钮;

- 在弹出的器件添加对话中,第一个器件选择bypass按钮;第二个器件也选择bypass按钮;

最后一个器件单击所要下载的dot.bit文件(此文件所在目录不可有中文),单击Open按钮,弹出“Add Virtex-/II Pro/Virtex04...”对话框,单击OK按钮后弹出一个警告信息,单击OK按钮;

- 单击xc4vsx25这个device,变成绿色,且 iMPACT Processes Operations窗口出现可执行的操作;

- 双击iMPACT Processes Operations窗口中的Program,或者直接右键单击xc4vsx25这个device,选择Program。弹出Programming Properties对话框,单击OK按钮;

- 程序开始下载,如果下载程序成功则出现Program Succeeded,否则如果失败则出现Program Failed,需要重新查找问题(尝试重新下载或者断电后重新下载程序);

- 程序下载成功后,观察LED点阵点亮(合众达图标)。

六、实验程序 dot.v//dot.v:程序顶层文件,对输入时钟进行分频,依次点亮相应的LED;

//dot.ucf:FPGA用户约束文件。

`timescale 1ns / 1ps

// Company:

// Engineer:

//

// Create Date:

// Design Name:

// Module Name: dot

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

module dot(CLK_IN, nRST, CPLD_E,DOT_DATA , DOT_CON ,AD_nCS , DA_nCS ,USB_nCS,LCD_nCS );

input CLK_IN;

input nRST;

output [1:0] CPLD_E;

output [15:0] DOT_DATA;

output [15:0]DOT_CON;

output USB_nCS;

output AD_nCS;

output DA_nCS;

output LCD_nCS;

reg CLK_OUT = 1'b1;

reg [15:0]DOT_CON =16'h0000;

reg [15:0]DOT_DATA =16'h0000;

reg [13:0] DIV_counter = 14'h000;

reg [3:0] cnt= 4'h0;

parameter DIV_FACTOR = 14'h3f98;

//CPLD功能切换

assign CPLD_E = 2'b11;

//其他芯片功能禁止

assign USB_nCS = 1'b1;

assign AD_nCS = 1'b1;

assign DA_nCS = 1'b1;

assign LCD_nCS = 1'b1;

//时钟分频

always@(posedge CLK_IN)

begin

if(!nRST)

begin

CLK_OUT <= 1'b1;

DIV_counter <= 10'h000;

end

else

begin

if(DIV_counter <= DIV_FACTOR )

begin

DIV_counter <= DIV_counter + 1;

end

else

begin

DIV_counter <= 12'h000;

CLK_OUT <= !CLK_OUT;

end

end

end

//点亮点阵

always@(posedge CLK_OUT)

begin

cnt = cnt+1;

if(cnt == 4'h0)

begin

DOT_CON <= 16'h8000;

DOT_DATA <= 16'hd800;

end

else if(cnt == 4'h1)

begin

DOT_CON <= 16'h4000;

DOT_DATA <= 16'h6c00;

end

else if(cnt == 4'h2)

begin

DOT_CON <= 16'h2000;

DOT_DATA <= 16'hb600;

end

else if(cnt == 4'h3)

begin

DOT_CON <= 16'h1000;

DOT_DATA <= 16'hdb00;

end

else if(cnt == 4'h4)

begin

DOT_CON <= 16'h0800;

DOT_DATA <= 16'h6d80;

end

else if(cnt == 4'h5)

begin

DOT_CON <= 16'h0400;

DOT_DATA <= 16'h2480;

end

else if(cnt == 4'h6)

begin

DOT_CON <= 16'h0200;

DOT_DATA <= 16'h1240;

end

else if(cnt == 4'h7)

begin

DOT_CON <= 16'h0100;

DOT_DATA <= 16'h0920;

end

else if(cnt == 4'h8)

begin

DOT_CON <= 16'h0080;

DOT_DATA <= 16'h0490;

end

else if(cnt == 4'h9)

begin

DOT_CON <= 16'h0040;

DOT_DATA <= 16'h0248;

end

else if(cnt == 4'ha)

begin

DOT_CON <= 16'h0020;

DOT_DATA <= 16'h0124;

end

else if(cnt == 4'hb)

begin

DOT_CON <= 16'h0010;

DOT_DATA <= 16'h0092;

end

else if(cnt == 4'hc)

begin

DOT_CON <= 16'h0008;

DOT_DATA <= 16'h0000;

end

else if(cnt == 4'hd)

begin

DOT_CON <= 16'h0004;

DOT_DATA <= 16'h0000;

end

else if(cnt == 4'he)

begin

DOT_CON <= 16'h0002;

DOT_DATA <= 16'h0000;

end

else if(cnt == 4'hf)

begin

DOT_CON <= 16'h0001;

DOT_DATA <= 16'h0000;

end

end

endmodule

七、思考题1、CLK_OUT是CLK_IN的几分频?

2、.UCF文件是做什么用的?

3、实验中的点阵LED是规格是什么?程序中用哪些引脚来控制LED?

实验三:LCD显示实验(一)一、实验目的- 熟悉ISE8.2开发环境,掌握工程的生成方法;

- 熟悉SEED-XDTK_V4实验环境;

- 了解LCD的HDL实现;

- 了解Memory模块的使用。

二、实验内容- FPGA的memory模块的生成及例化;

- 系统时钟设计;

- LCD点亮。

三、实验例程1、LCD芯片介绍

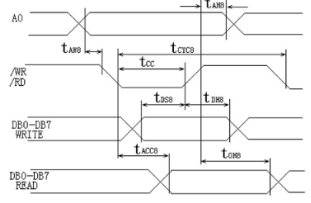

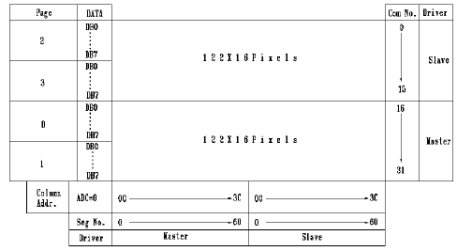

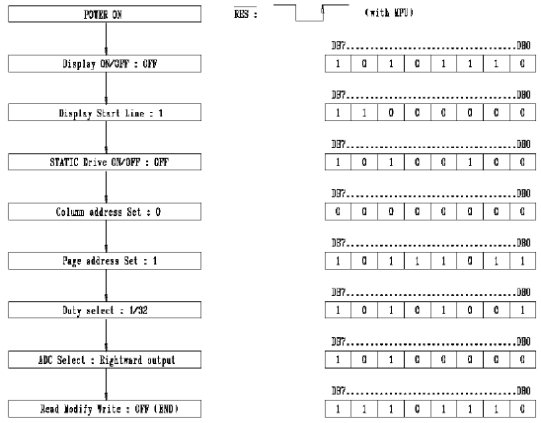

LCD模块采用是LCM122326图形点阵模快,该模块是由2块NJU6450芯片构成,不带字库。其工作时序图如下图所示:

LCD模块行列分配:

LCD初始化如下所示

2 例程包含文件

- main.v:程序顶层文件,实现LCD的初始化以及液晶显示;

- v4_dcm.xaw:DCM的IP核,将外部输入时钟(50M)进行10分频;

- CLK_DIV.v:系统运行时钟分频文件,将系统运行时间进行分频,提供100K的模块处理时钟;

- LCD_DISPLAY.v:LCD初始化,以及数据显示文件;

- LCD_WRITE.v:LCD写操作函数文件;

- v2_lcd_ziku.xco:汉字字库存储文件;

- main.ucf:FPGA用户约束文件。

- //main.v

- `timescale 1ns / 1ps

- module main(CLK, nPROCESSOR_RESET_Z, D, LCD_E, LCD_A0, LCD_R_nW, LCD_LED, LCD_nCS, CPLD_E, AD_nCS, DA_nCS, USB_nCS,);

- input CLK;//100M aj15

- input nPROCESSOR_RESET_Z;//ah5

- inout [7:0] D;

-

- output [1:0] LCD_E;

- output LCD_A0;

- output LCD_R_nW;

- output LCD_LED;

- output LCD_nCS;

- output [1:0] CPLD_E;

- output AD_nCS;

- output DA_nCS;

- output USB_nCS;

-

- wire CLK_LOCKED;

- wire [7:0] DATA_OUT;

- wire CLK_100K;

- parameter DIV_FACTOR = 100;

-

- //LCD功能始能

- assign LCD_nCS = 1'b0;

- //CPLD功能切换

- assign CPLD_E = 2'b11;

- //其他芯片功能禁止

- assign AD_nCS = 1'b1;

- assign DA_nCS = 1'b1;

- assign USB_nCS = 1'b1;

-

- //系统时间分频

- //输入 50M 输出10M

- v4_dcm CLK_DIV_10M (

- .CLKIN_IN(CLK),

- .RST_IN(!nPROCESSOR_RESET_Z),

- .CLKDV_OUT(CLK_10M),

- .CLKIN_IBUFG_OUT(),

- .CLK0_OUT(),

- .LOCKED_OUT(CLK_LOCKED)

- );

- //模块时间分频

- //输入 10M 输出100K

- CLK_DIV CLK_DIV_100K (

- .CLK_IN(CLK_10M),

- .nRST(CLK_LOCKED),

- .CLK_OUT(CLK_100K)

- );

- defparam CLK_DIV_100K.DIV_FACTOR = DIV_FACTOR;

-

- /////////// LCD TEST ///////////////

- reg r_nw = 1'b1;

- reg [6:0] zimo_num = 7'h00;

- reg [6:0] mem_addr = 7'h00;

- reg lcd_en = 1'b0;

- reg [6:0] col_addr = 121;

- reg [1:0] page_addr = 2'b11;

- reg [4:0] disp_addr = 5'h00;

-

- wire [7:0] lcd_data;

- wire lcd_done;

- reg [16:0] tLCD_counter = 17'h00000;

-

- LCD_DISPLAY LCD (

- //输入参数

- .CLK(CLK_100K),

- .R_nW(r_nw),

- .DISP_ADDR(disp_addr),

- .PAGE(page_addr),

- .COL_ADDR(col_addr),

- .DISP_DATA(lcd_data),

- //输出参数

- .LCD_E(LCD_E),

- .LCD_A0(LCD_A0),

- .LCD_R_nW(LCD_R_nW),

- //输入、出参数

- .LCD_DB(D),

- //输出参数

- .LCD_LED(LCD_LED),

- .DATA_OUT(),

- .DONE(lcd_done)

- );

-

- v4_lcd_ziku ZIMO(

- .addr(mem_addr),

- .clk(CLK_100K),

- .dout(lcd_data),

- .en(lcd_en));

-

- always@(posedge CLK_100K)

- begin

- if(tLCD_counter == 17'h0c350)//0.5s

- begin

- disp_addr <= disp_addr - 1; //显示地址

- tLCD_counter <= 17'h00000;

- end

- else

- begin

- tLCD_counter <= tLCD_counter + 1;

- end

-

- if(!lcd_done)

- begin

- r_nw <= 1'b0;

- lcd_en <= 1'b0;

- end

- else

- begin

-

- r_nw <= 1'b1;

- if(!r_nw)

- begin

- lcd_en <= 1'b1;

- mem_addr <= zimo_num;

- if(zimo_num == 95)

- zimo_num <= 0;

- else

- zimo_num <= zimo_num + 1;

-

- case(zimo_num)

- 0:

- begin

- col_addr <= 23;

- page_addr <= 2'b00;

- end

- 16:

- begin

- col_addr <= 23;

- page_addr <= 2'b01;

- end

- 32:

- begin

- col_addr <= 68;

- page_addr <= 2'b00;

- end

- 48:

- begin

- col_addr <= 68;

- page_addr <= 2'b01;

- end

- 64:

- begin

- col_addr <= 113;

- page_addr <= 2'b00;

- end

- 80:

- begin

- col_addr <= 113;

- page_addr <= 2'b01;

- end

- default: col_addr <= col_addr - 1;

- endcase

- end

- else

- begin

- lcd_en <= 1'b0;

- end

- end

- end

- endmodule

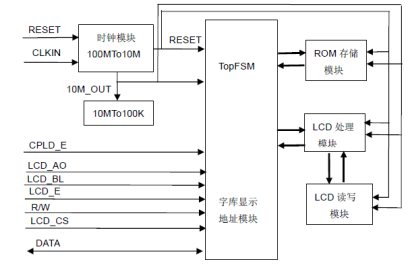

3 模块划分图

4 Memory 模块的建立及其例化

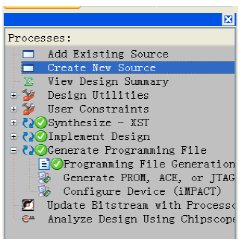

- 双击Processes窗口中的Creat New Source,弹出新资源向导窗口;

- 在弹出新资源向导窗口,选择IP (CoreGen & Architecture Wizard),在File name 栏里输入v4_lcd_ziku;

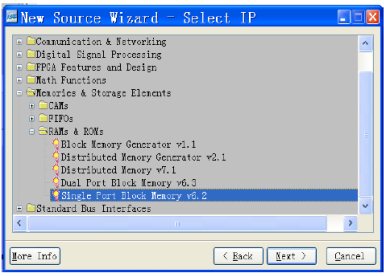

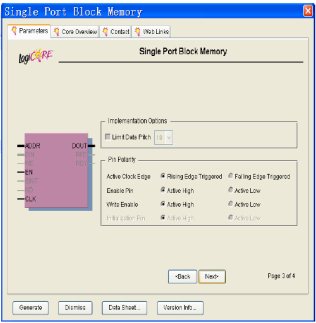

- 单击Next按钮,弹出Select IP窗口,依次展开Memories & Storage Element和RAMs & ROMs目录,选择Sigle Port Block Memory V6.2;

- 单击Next按钮,显示新建资源信息,单击Finish按钮;

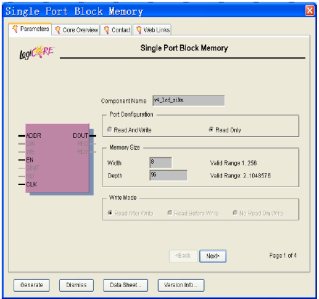

- 弹出Sigle Port Block Memory窗口,在Port Configuration选项卡中选中Read Only;Memory Size选项卡中Width 填写8。Depth填写96;Write Mode 选项卡中选中Read After Write;单击Next命令;

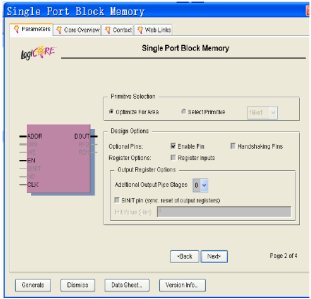

- 单击Next按钮,Primitive Selection选项卡中选中 Optimize For Area,Design Options选项卡中选中 Enable Pin,Output Register Options 选项卡中Additional Output Pins Stages 填写 0,单击next命令;

- 单击Next按钮,不选中Implementation Option选项卡;管脚极性选项卡中选择上升沿有效或者高电平有效;

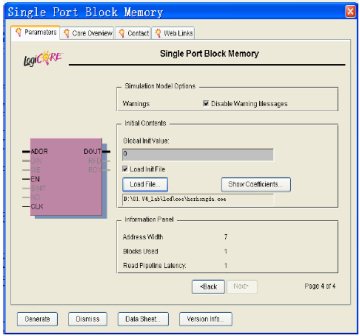

- 单击Next按钮,Simulation Mode Options选项卡中选中Disable Waring Messages;Initial Contents选项卡中 Global init Value 填写 0,选中 Load Init File添加hezhongda.coe(路径为D:\02.V4_lab\ lcd\coe);

- 单击 Generate 命令,生成v4_lcd_ziku.xco文件;

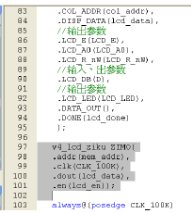

10、Memory模块的例化与DCM模块例化方法一致,请参考键盘实验中关于该部分的内容。下图中,黑色部分为Memory模块的例化语句。

四、实验准备- 将光盘下03. Examples of Program\02. V4_lab文件夹拷贝到D:盘根目录下;

- 通过USB口下载电缆将计算机USB口及SEED-FEM025板的J9 连接好;

- 启动计算机,打开SEED-XDTK_V4实验箱电源开关。观察SEED-FEM025板上的+5V(D11)的电源指示灯是否均亮。若有不亮的,请断开电源,检查电源。

五、实验步骤- 打开ISE8.2,装载lcd.ise工程文件;

- 双击Configure Device (iMPACT)命令。弹出Welcome iMPACT对话框后,选择“Configure devices using Boundary-Scan(JTAG)”,单击Finish按钮;

- 在弹出的器件添加对话中,第一个器件选择bypass按钮。最后一个器件单击所要下载的载main.bit文件;

- 单击xc4vsx25这个device,变成绿色,且 iMPACT Processes 窗口出现可执行的操作;

- 双击iMPACT Processes 窗口中的Program,或者直接右键单击xc4vsx25这个device,选择Program。弹出Programming Properties对话框,单击OK按钮;

- 程序开始下载,如果下载程序成功则出现Program Succeeded,否则如果失败则出现Program Failed,需要重新查找问题(尝试重新下载或者断电后重新下载程序);

- 文件下载成功后,观察lcd显示(“合众达”刷屏显示)。

六、思考题1、顶层文件main.v的功能是什么?输入输出信号各有几个?

2、顶层文件main.v调用了几个元件例化?各自的功能是什么?

3、顶层文件main.v还使用了哪些语句?其功能是什么?

实验三:LCD显示实验(二)一、实验目的- 熟悉ISE8.2开发环境,掌握工程的生成方法;

- 熟悉SEED-XDTK_V4实验环境;

- 了解LCD汉字字模的设计方法;

- 掌握Memory模块的使用。

二、实验内容- FPGA的memory模块的生成及例化;

- 点亮LCD,定点显示学生姓名(最少2个汉字,最多14个汉字)。

三、实验步骤- 打开ISE8.2,新建lcd.ise工程文件;

- 输入所需的.v文件,生成对应的汉字字模CORE文件。设计实现整个工程。

- 双击Configure Device (iMPACT)命令。弹出Welcome iMPACT对话框后,选择“Configure devices using Boundary-Scan(JTAG)”,单击Finish按钮;

- 在弹出的器件添加对话中,第一个器件选择bypass按钮。最后一个器件单击所要下载的载main.bit文件;

- 单击xc4vsx25这个device,变成绿色,且 iMPACT Processes 窗口出现可执行的操作;

- 双击iMPACT Processes 窗口中的Program,或者直接右键单击xc4vsx25这个device,选择Program。弹出Programming Properties对话框,单击OK按钮;

- 程序开始下载,如果下载程序成功则出现Program Succeeded,否则如果失败则出现Program Failed,需要重新查找问题(尝试重新下载或者断电后重新下载程序);

- 文件下载成功后,观察lcd显示(分组学生姓名定位显示);

- 记录实验现象,下课交报告。

EDA实验指导书.doc

(1.18 MB, 下载次数: 23)

EDA实验指导书.doc

(1.18 MB, 下载次数: 23)