2.2.3 驱动方程 状态方程

状态方程:

![]() =

=![]()

![]() =

=![]() +

+

![]() =

= ![]()

驱动方程:

J2=![]() K2=

K2=

J1=1 K1=

![]() J0=

J0=![]()

![]() K0=

K0=![]()

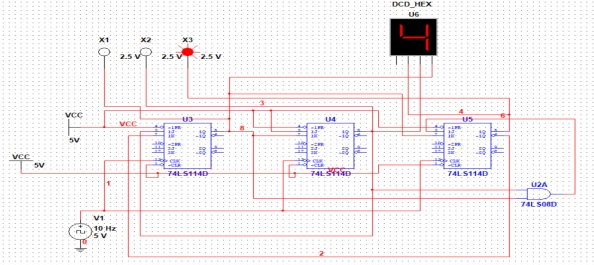

实验结果可通过数字显示器的数字变化和灯泡亮灭对比检验,较直观易懂,容易验证电路是否正确。

实验用三片74LS114芯片,一片74LS08芯片,三个灯泡一个数码管,一个信号发生器组成。

3位二进制同步减法计数器(其中的无效状态000 101)

初始状态001

图2.6 状态一

给一个脉冲变成010

图 2.7 状态二

给第二个脉冲变成011

图 2.8 状态三

给第三个脉冲变成100

图 2.9 状态四

给第四个脉冲变成110

图 2.10状态五

给第五个脉冲变成111

图 2.10 状态六

给第六个脉冲变成001(起始状态)

图 2.11 状态七

从上面的仿真图形可知,实现的功能是计六个数,分别是123467按照加法的规律递加变化,六个数计满之后触发器随即清零,从新开始计数。

检查自启动

将无效态(000,101)带入状态方程,输出方程进行计算

![]()

![]()

![]()

![]()

![]() 001 010 011 100 110 111

001 010 011 100 110 111

结果均为有效态故能自启动,次态图为:

![]()

![]() 000 101

000 101

![]()

![]()

![]()

![]()

![]()

![]()

![]() 001 010 011 100 110 111

001 010 011 100 110 111

![]()

1)了解集成芯片的性能和使用方法;

2)学习用集成芯片设计记数序列;

3)学习如何设计同步计数器。

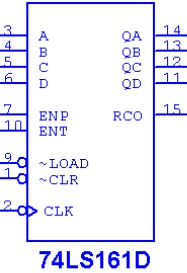

3. 2设计原理:

3. 2设计原理:右图是其芯片图,此图中,CLK是计数脉冲输入端,下降沿触发;~LOAD为同步置数端,低电平有效;~CLR是异步清零端,低电平有效;ENP和ENT是芯片的工作状态控制端;RCO是进位信号输出端,A,B,C,D是并行输入数据端,QA,QB,QC,QD是计数器状态输出端。

当同步置数端有效时,在时钟信号下降沿操作下,并行输入置数数据ABCD,是输出信号为ABCD;当异步清零端有效时,其它输入信号都不起作用,将计数器清零。

3.3设计思路:![]()

![]()

![]() 采用74LS161芯片的异步清零端完成12进制加法过程,

采用74LS161芯片的异步清零端完成12进制加法过程,![]() =

=![]() =1100,

=1100,![]() 、

、![]() (即11、12引脚)和CR连接成与非门;在同一个芯片上采用同步置数端完成7进制加法过程,利用

(即11、12引脚)和CR连接成与非门;在同一个芯片上采用同步置数端完成7进制加法过程,利用![]() 、

、![]() (即12、13引脚)和CR连接成与非门。将两个与非门的输出端和CR用一个双掷开关连接,要求完成任意一个功能只需用开关即可。

(即12、13引脚)和CR连接成与非门。将两个与非门的输出端和CR用一个双掷开关连接,要求完成任意一个功能只需用开关即可。

图2.12

图2.13

12进制加法器调试结果:

图2.14

7进制加法器调试结果:

图2.15

(1)数字原理实验系统一台

(2)集成电路芯片:74LS161一片 74LS00两片

(1) 实验结论

经过实验可知,满足时序图的变化,且可以进行自启动。

实验过程中很顺利,没有出现问题。

(2) 总结体会

经过自己的努力完成了数字电子技术课设,我已经熟练的掌握了Multisim的使用方法,可以轻松地找到许多元器件,在巩固已有知识的基础上学到了新知识。刚开始做的时候,怎么也执行不出来,最后通过多方面的调整和学习执行出了结果,这更让我明白了持之以恒的重要性,锻炼了自己的头脑和动手能力,受益匪浅。

数字电子技术基础简明教程/余孟尝主编;

清华大学电子学教研组编.-3版.-北京:高等教育出版社,

完整的Word格式文档51黑下载地址:

数电课设.docx

(772.07 KB, 下载次数: 8)

数电课设.docx

(772.07 KB, 下载次数: 8)

| 欢迎光临 (http://www.51hei.com/bbs/) | Powered by Discuz! X3.1 |