可编程时钟控制器(Programmable Time Controller,PTC),也称可编程时控器、可编程时控开关,是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

可编程时钟控制器属自动控制领域的电器件,主要用于在多段时间周期内控制多个电路的开启或关闭,即具有多周期设置和多触点输出。该类产品工业与民用兼顾,智能化程度高且操作简便。

可编程时钟控制器从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。因此,设计与制做数字钟就是为了了解数字钟的原理,从而学会制作数字钟.而且通过数字钟的制作进一步的了解在制作中用到的各种中小规模集成电路的作用及实用方法.且由于数字钟包括组合逻辑电路和时序电路.通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法.

(一)、设计方案分析

1.分析设计要求,构思总体方案

从题目克制该课题的任务主要有三个方面。其一是设计一个能以数字直接先试试的时钟电路,该电路要有能够快速校时的功能;其二是用时钟信号作为基础设计一个整点报时的电路;其三是用时钟信号实现一个工业过程的时间顺序控制。可见,课题属于控制类题目,但并无外部输入信号,而是由时钟自动产生动作信号。整个系统可分成三部分,即时钟电路、整点报时电路、顺序控制器电路,而时钟电路在起控制和主导作用。

2.时钟电路的构成方案

(1)选用中、小规模集成芯片设计;

3.时间顺序控制器

这部分电路都是以时间代码为输入信号,经译码后产生定时控制信号去推动控制设备工作。译码器完成有代码到控制信号的变换,这里的代码即时钟信号代码,控制信号是驱动控制设备的信号。实现的电路形式是多种多样的。

(1)利用集成门电路进行设计;

(2)选用合适的现成译码器;

(3)用GAL芯片进行编程,实现译码;

(4)用存储器完成译码的功能。

怎样用存储器完成译码功能?可用时钟电路输出的时钟代码作为存储器的地址信号,存储器中存放的数据作为外设工作的控制信号。当时钟运行到需要外设动作的某一时刻,是存储器的地址信号及读信号有效,读出存储器中相应的数据信号,每个数据位控制一个外设,若某位数据有效,则相应的外设即可启动。这种方法简便,时间容易修改。存储器可用RAM、EPROM及EEPROM。

外设的形式多种多样,要求的驱动功率各不相同,因而在译码输出与外设之间必须设置适当的功放电路,以提供外设工作的驱动电流与电压。应按照所选的具体执行机构选定功放电路。

(二)、确定总体方案

依据上述分析,实现题目要求的电路方案有多种选择,须要根据各人的条件、要求和其他具体情况权衡利弊,确定其中的一种。这里选择两种不同方案作具体电路设计。

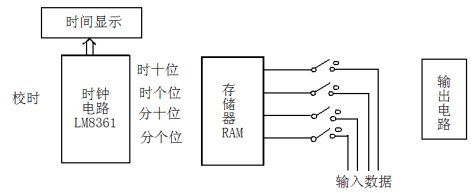

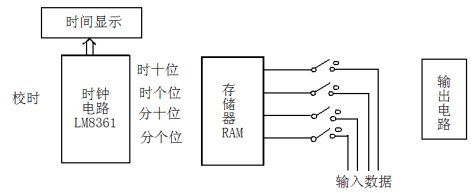

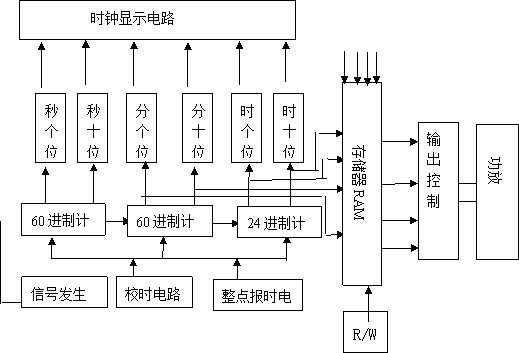

设计方案一采用的是大规模时钟集成芯片LM8361作时钟电路,用存储器RAM6264作译码器,设计工艺流程控制电路。其系统框图如下图所示:

图3-2-1 大规模顺序控制器框图

2.设计方案二

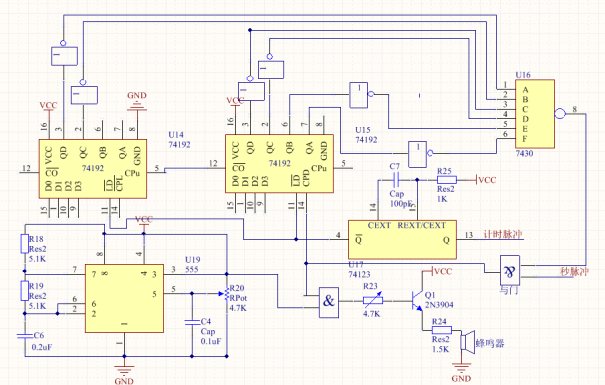

设计方案二采用的是用中小规模门电路构成的时钟电路,采用的是555定时器作为时基电路,发出1HZ的脉冲作为秒的输入脉冲,用74LS192设计24、60进制的计数器,用72LS248作为译码器,使用7段数码管来显示时间,利用门电路构建快速校时电路,用RAM62256存储器作译码器设计可编程时间顺序控制器。系统框图如图3-2-2所示。

图3-2-2 钟控顺序控制器框图

3.最终方案的选择

作为课程设计的方案,应该具有设计成本较低,可操作性强,与课程学习有较为紧密的联系等优点。由于大规模集成芯片价格较为昂贵,且可操作性较差,在实际学习中用到的机会比较少,所以方案一不适合作为本次课程设计的方案,而方案二采用的是小规模集成芯片和门电路作为电路设计的基础,具有较强的可操作性,且价格较为低廉,而所使用的芯片,门电路都是在学习中使用较为频繁的部分,所以本次课程设计采用的是方案二,利用中西规模门电路构成时钟电路,用RAM62256存储器作为译码器设计可编程顺序控制器。

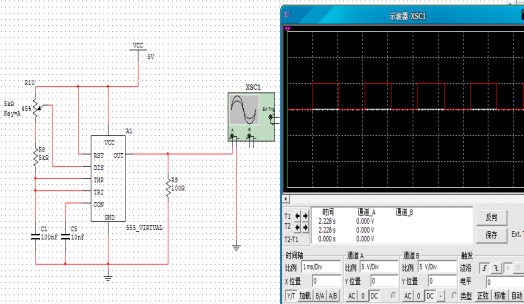

图3-2-9 555定时器组成的时基电路

555定时器成本低,性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器、单稳态触发器及施密特触发器等脉冲产生与变换电路。它也常作为定时器广泛应用于仪器仪表、家用电器、电子测量及自动控制等方面。555 定时器的内部电路框图如图 2.9.1。它内部包括两个电压比较器,三个等值串联电阻,一个 RS 触发器,一个放电管 T 及功率输出级。它提供两个基准电压VCC /3 和 2VCC /3

555 定时器的功能主要由两个比较器决定。两个比较器的输出电压控制 RS 触发器和放电管的状态。在电源与地之间加上电压,当 5 脚悬空时,则电压比较器 C1 的同相输入端的电压为 2VCC /3,C2 的反相输入端的电压为VCC /3。若触发输入端 TR 的电压小于VCC /3,则比较器 C2 的输出为 0,可使 RS 触发器置 1,使输出端 OUT=1。如果阈值输入端 TH 的电压大于 2VCC/3,同时 TR 端的电压大于VCC /3,则C1 的输出为 0,C2 的输出为 1,可将 RS 触发器置 0,使输出为 0 电平。

它的各个引脚功能如下:

1脚:外接电源负端VSS或接地,一般情况下接地。

8脚:外接电源VCC,双极型时基电路VCC的范围是4.5 ~ 16V,CMOS型时基电路VCC的范围为3 ~ 18V。一般用5V。

3脚:输出端Vo; 2脚:低触发端

6脚:TH高触发端

4脚:是直接清零端。当此端接低电平,则时基电路不工作,此时不论TR、TH处于何电平,时基电路输出为“0”,该端不用时应接高电平。

5脚:VC为控制电压端。若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF电容接地,以防引入干扰。

7脚:放电端。该端与放电管集电极相连,用做定时器时电容的放电。

利用555定时器产生1HZ的脉冲作为秒信号如下图:

(1)74ls192介绍

74192是双时钟的十进制可逆计数器。(BCD二进制),下面我们介绍74192引脚图,74192功能表等。

CPU为加计数器时钟入端,CPU为减计数器入端;

LD为预置输入控制端,异步预置;

CR为复位输入端,高电平有效,异步清除;

CO为进位输出:1001状态后负脉冲输出;

BO为借位输出:0000状态后负脉冲输出;

(2)功能表:

(3)引脚图:

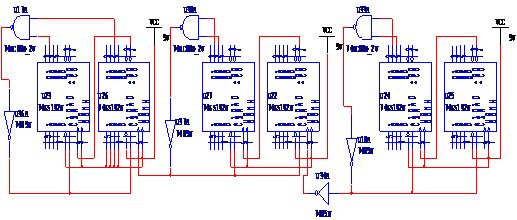

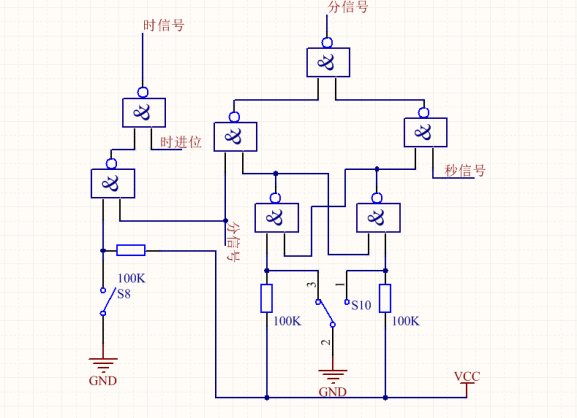

(4)十、分、秒电路总体结构图

(5)60进制计数器单元仿真电路图

电路分析:

由555定时器产生1HZ脉冲作为输入,将74ls192接成60进制计数器,经过74ls248译码后由七段数码管显示出时钟信号,构成了60进制的时钟电路。

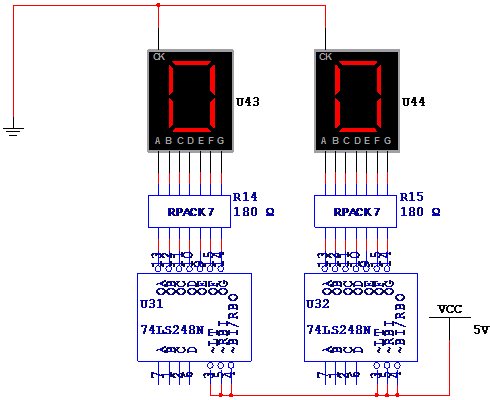

2位译码显示电路单元仿真电路图如下图:

图3-2-12-0

电路分析:

如上图所示,由74LS248芯片以及共阴极七段数码管构成译码显示电路,由74248的ABCD接收计数器的数值经转换后得到七位的七段数码管显示值,由共阴极七段数码管显示最终数值。

图3-2-14 整点报时电路

本电路设计简洁、实用,大部分模块单元选用集成运放电路。在时基电路中采用集成NE555, 在时间计数器电路中采用集成芯片CT74192,在译码、驱动及显示电路中采用集成芯片74LS248。如此设计使得电路外围结构简单,体积小巧精致,且较好的结合了各运放的优良性能,使电路能满足各项指标。现介绍各芯片列表如下:

五、设计方案总结

实验过程中遇到的问题及解决方法:

① 元器件的选择不存在问题。

② 七段显示器与驱动器连接的测量时, 有时有些数字显示断开、 不完整。 原因可能是数码管引脚接触不良,或者是通关数码管的电流过大 需 要接入排阻。 在接电路时译码管的电源和接地的没接, 直接导致译码 管无法工作,数码管无数字显示。

③ 时间计数电路的连接与测试 仔细的连接电路是非常重要的,不要忘了电源和接地的引脚连接线。 测试时秒 计数显示无法进位、跳动还较快,无法进位是因为在 74LS08D 集成管的输入输出弄错引脚, 跳动较快是因为把 4060BP 和 74LS74D 的接线引脚接在了 4060BP 的 2 引脚。 经检查发现接线错误 调整后,时间秒显示正常。

④ 校正电路 校正时有时单独校正分,时会跟着调动,原因是分与时的进位接线没 断开。

六、心得体会

通过这次实训,让我们更加了解了各种集成块的应用,也对其中一 些集成块的用途有了一定的了解。实训对于我们的动手设计能力也是一 种提高,细心,认真在其尤其重要。对于一些容易遗漏的引脚,如电源, 接地引脚特别要注意。 该电路的设计让我对数字钟的设计有了一定的了解。我知道了如何 设计出 1HZ 的信号,也对时分秒的设计有了一定的了解。并且在实际电 路一般步骤为由数字钟系统组成框图按照信号的流向分级安装,逐级级 联,这里的每一级是指组成数字钟的各功能电路。级联时如果出现时序 配合不同步,或尖峰脉冲干扰,引起逻辑混乱,可以增加多级逻辑门来 延时。经过联调并纠正设计方案中的错误和不足之处后,再测试电路的逻辑功能是否满足设计要求。 最后画出满足设计要求的总体逻辑电路图。

完整的Word格式文档51黑下载地址(内含清晰大图):

可编程时钟控制器的设计 - (2).doc

(430.5 KB, 下载次数: 12)

可编程时钟控制器的设计 - (2).doc

(430.5 KB, 下载次数: 12)

| 欢迎光临 (http://www.51hei.com/bbs/) | Powered by Discuz! X3.1 |