- 设计一个数字式竞赛抢答器,可以判断第一轮抢答者,并具备计分功能。

- 抢答器可以容纳4组参赛者同时抢答,每组设置1个按钮供抢答者使用。设置抢答器使能信号,当此信号有效时,若参赛者按下抢答开关,则抢答器能判断出第一抢答者并指示该组抢答成功,其他组参赛者的抢答者的抢答开关不起作用。若提前抢答,则对相应的参赛者发出报警。

- 系统具有清零功能。当清零复位信号有效时,抢答器对前一轮抢答的第一抢答者判断结果进行清零,恢复为初始状态。

- 数字式竞赛抢答器还具有计分功能。如果抢答成功的参赛者满足得分条件,则增加相应的分数,答错不扣分。

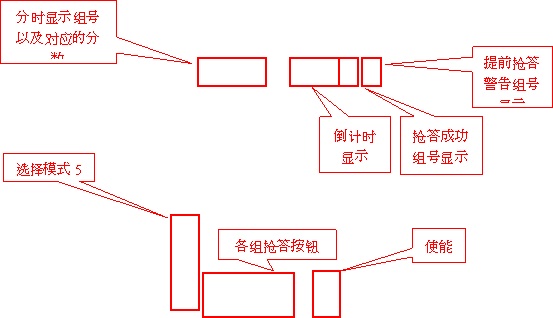

(二)系统设计方案根据系统设计要求可知,系统由4个主要的电路模块组成,分别是第一判断电路、计分电路、20s倒计时电路和显示电路。

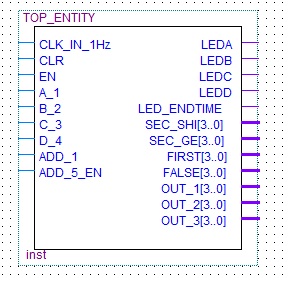

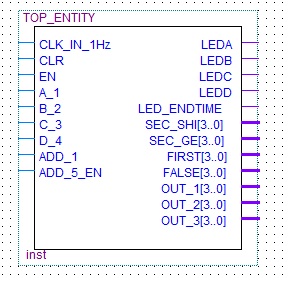

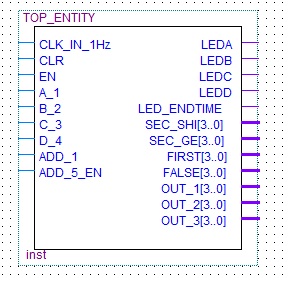

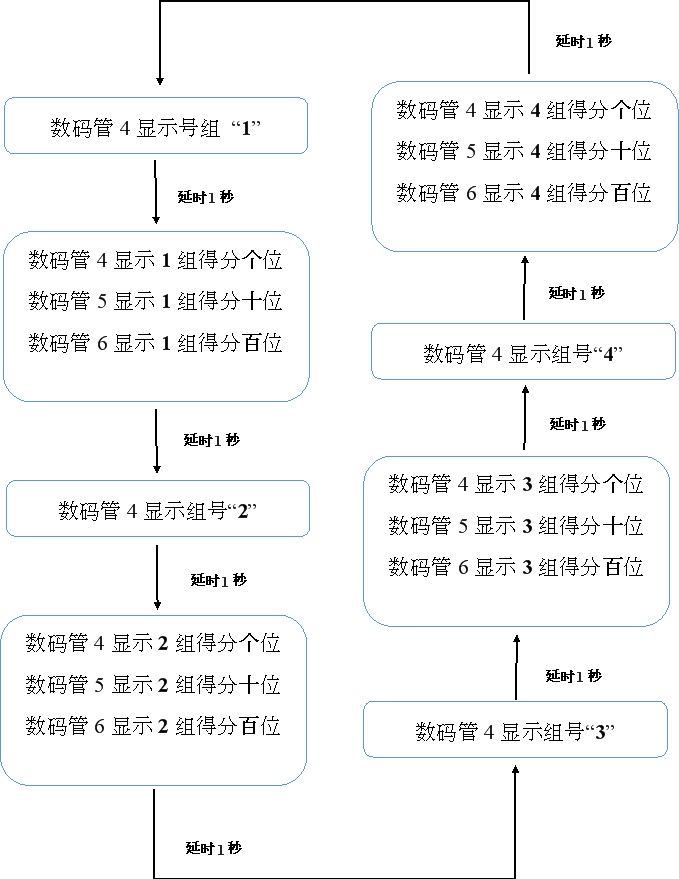

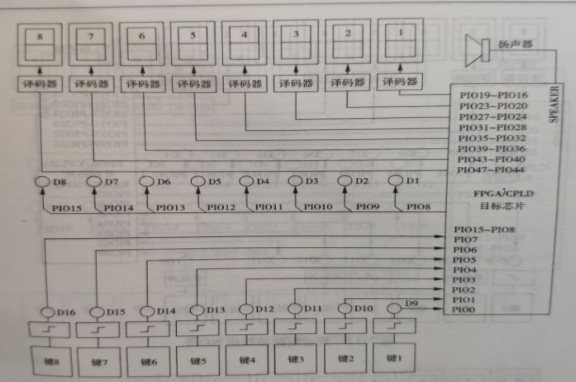

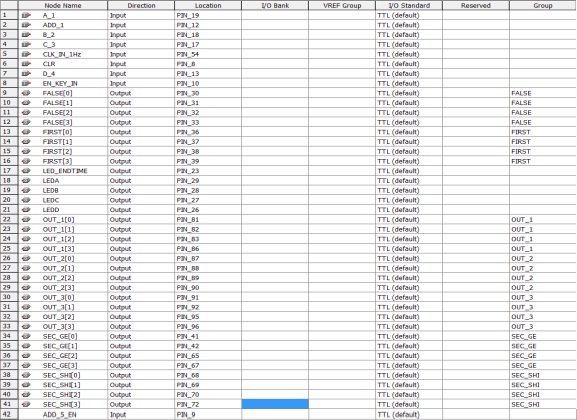

其中,第一判断电路主要完成最快抢答者的判断功能;计分电路存储每组竞赛者的分数;显示电路则显示抢答器的状态和各组的分数。因此,数字式竞赛抢答器的输入信号包括复位信号CLR、抢答器使能信号EN_KEY_IN、4组参赛者的抢答按钮A_1/B_2/C_3/D_4以及加分信号ADD_1,加5分使能信号ADD_5_EN;输出信号包括4组参赛者抢答状态的显示LEDx(x表示参赛者编号)及其对应的得分SCOREX、抢答器抢答成功的组别显示,最先抢答组显示FIRST[3..0],提前抢答组显示FALSE[3..0],轮流输出各组号以及分数OUT_1,OUT_2,OUT_3等。系统框图如图所示:

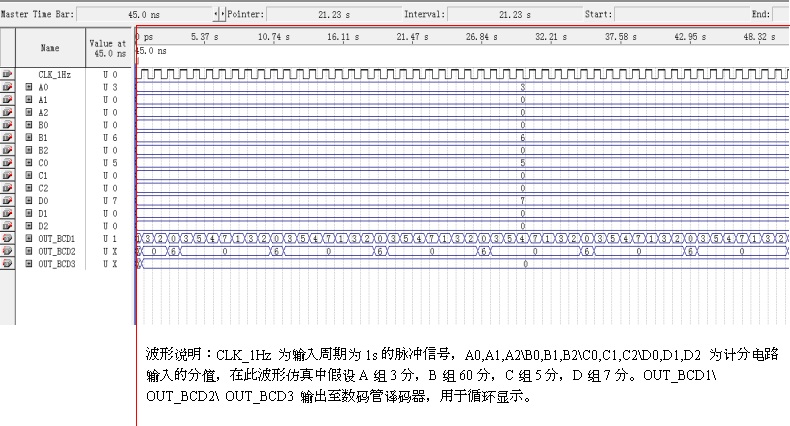

1. 抢答器的工作流程如下:如果参赛者在抢答器使能信号EN有效前按下抢答按钮,报警信号FALSE[3..0]的对应位输出高电平,以示警告;当EN信号有效时,抢答器开始工作,将报警信号FALSE清零,A、B、C、D,4个抢答者谁先按下抢答按钮,则抢答成功,对应的显示灯LEDx亮起,并通过显示电路模块显示其参赛编FIRST[3..0];抢答成功的选手进入答题阶段,如正确回答问题,则加分信号ADD有效,计分模块给相应的参赛组加分,每个参赛组得分的个位、十位、百位分别通过信号OUT_BCD1[3..0]、OUT_BCD2[3..0]、OUT_BCD3[3..0]、显示。

如果复位信号CLR有效,使得抢答器在下一轮抢答前,其抢答成功的组别判断恢复为始状态,以便重新开始新一轮抢答。复位信号不改变竞赛者的现有得分。

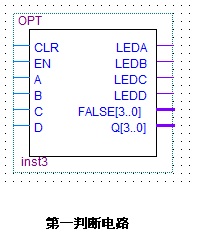

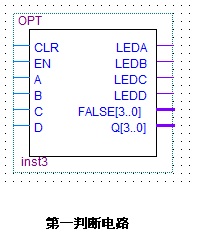

2.流程图:(三)主要模块设计1.0 第一判断电路第一判断电路模块具有第一抢答信号的鉴别和锁存功能,其电路框图如图所示。

其中,CLR为复位信号,当该信号高电平有效时,电路无论处于何种状态都恢复为初始状态即所有的输出信号都为0;EN为抢答使能信号,该信号高电平有效;A、B、C、D为抢答按钮,高电平有效。

当使能信号EN为低电平时,如果有参赛者按下抢答按钮,则提前抢答报警信号FALSE[3.0]的对应位输出高电平,以示警告;当使能信号EN为高电平时,首先将提前抢答报警信号FALSE [3.0]复位清零,然后根据选手按下抢答按钮A、B、C、D的先后顺厅选择最先抢答的信号,其对应的抢答状态显示信号LEDA~LEDD输出高电平,抢答成功组别编号由信号Q[3..0]输出,并锁存抢答器此时的 状态,直到清零信号有效为止。在每一轮新的抢答之前,都要使用复位清零信号CLR,清除上一轮抢答对判断电路留下的使用痕迹,使电路恢复初始状态。

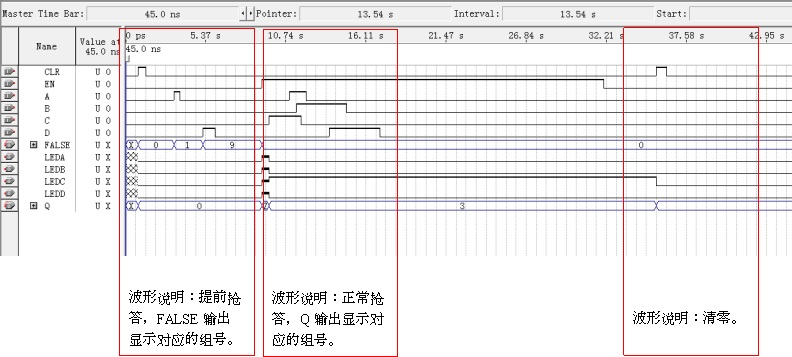

1.1 第一判断电路波形仿真图

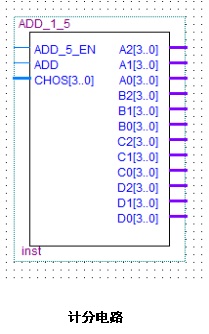

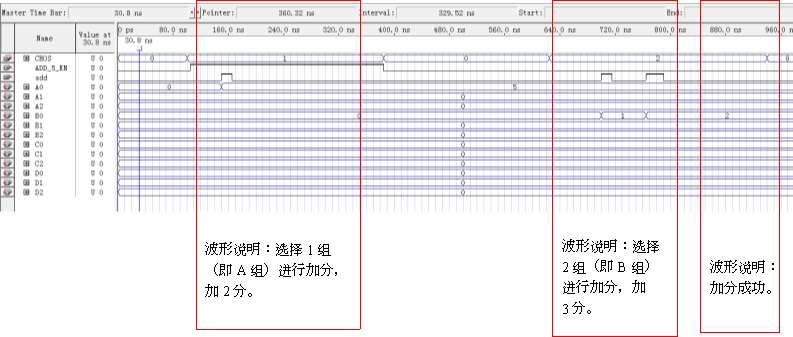

2.0 计分电路 其中加分信号ADD_1高电平有效,有效时对组别选择信号CHOS[3..0]选择的参数组进行加分;组别选择输入信号CHOS[3..0]即第一判断电路模块的输出信号Q [3.0]。输出信号分别对应4组竞赛者的得分,以百分制表示。每组分数在比赛开始时预设为100分,每答对1题(即加分选择信号对相应参赛组有效)加1分,答错不扣分。得分的各位、十位、百位表示为宽为4的逻辑矢量,使之方便与显示电路级联,从而输出比赛得分。

当使能信号EN为低电平时,如果有参赛者按下抢答按钮,则提前抢答报警信号FALSE[3.0]的对应位输出高电平,以示警告;当使能信号EN为高电平时,首先将提前抢答报警信号FALSE [3.0]复位清零,然后根据选手按下抢答按钮A、B、C、D的先后顺厅选择最先抢答的信号,其对应的抢答状态显示信号LEDA~LEDD输出高电平,抢答成功组别编号由信号Q[3..0]输出,并锁存抢答器此时的 状态,直到清零信号有效为止。在每一轮新的抢答之前,都要使用复位清零信号CLR,清除上一轮抢答对判断电路留下的使用痕迹,使电路恢复初始状态。

当使能信号EN为低电平时,如果有参赛者按下抢答按钮,则提前抢答报警信号FALSE[3.0]的对应位输出高电平,以示警告;当使能信号EN为高电平时,首先将提前抢答报警信号FALSE [3.0]复位清零,然后根据选手按下抢答按钮A、B、C、D的先后顺厅选择最先抢答的信号,其对应的抢答状态显示信号LEDA~LEDD输出高电平,抢答成功组别编号由信号Q[3..0]输出,并锁存抢答器此时的 状态,直到清零信号有效为止。在每一轮新的抢答之前,都要使用复位清零信号CLR,清除上一轮抢答对判断电路留下的使用痕迹,使电路恢复初始状态。

计分电路在参赛者抢答成功后,根据其比赛情况进行比较分数的调整,其电路框图如右图所示。该模块输入信号为加分信号ADD_1和组别选择信号CHOS[3.0]。

计分电路在参赛者抢答成功后,根据其比赛情况进行比较分数的调整,其电路框图如右图所示。该模块输入信号为加分信号ADD_1和组别选择信号CHOS[3.0]。

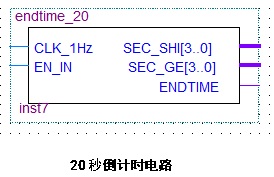

其中,CLK_1Hz是时钟信号,频率为1Hz,用来计时,间隔为1秒;EN_IN是使能信号,高电平有效开始倒计时,ENDTIME输出信号,用来提示时间到,连接LED灯,当时间为0时输出高电平,led灯点亮。SEC_SHI[3..0]、SEC_GE[3..0]分别是倒计时的十位和各位,连接带译码器的数码管,用来显示倒计时的时间。

其中,CLK_1Hz是时钟信号,频率为1Hz,用来计时,间隔为1秒;EN_IN是使能信号,高电平有效开始倒计时,ENDTIME输出信号,用来提示时间到,连接LED灯,当时间为0时输出高电平,led灯点亮。SEC_SHI[3..0]、SEC_GE[3..0]分别是倒计时的十位和各位,连接带译码器的数码管,用来显示倒计时的时间。

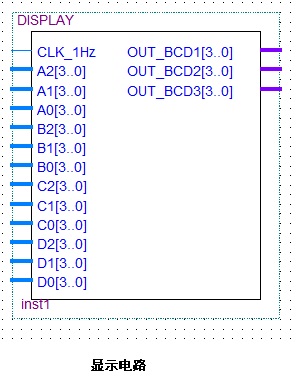

显示电路用来轮流显示各组的得分情况。由于实验箱数码管有限,所以采用了数码管分时复用的方法来显示各组的得分情况。其电路框图如右图:

显示电路用来轮流显示各组的得分情况。由于实验箱数码管有限,所以采用了数码管分时复用的方法来显示各组的得分情况。其电路框图如右图:

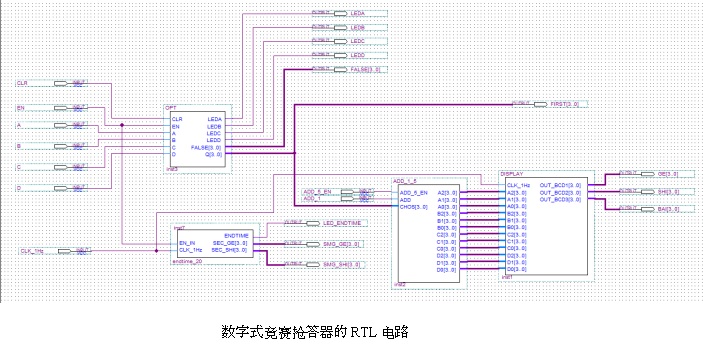

上述VHDL源程序构成了一个具有抢答、计分、倒计时警报功能的数字系统,通过仿真生成的RTL电路如图所示:

上述VHDL源程序构成了一个具有抢答、计分、倒计时警报功能的数字系统,通过仿真生成的RTL电路如图所示:

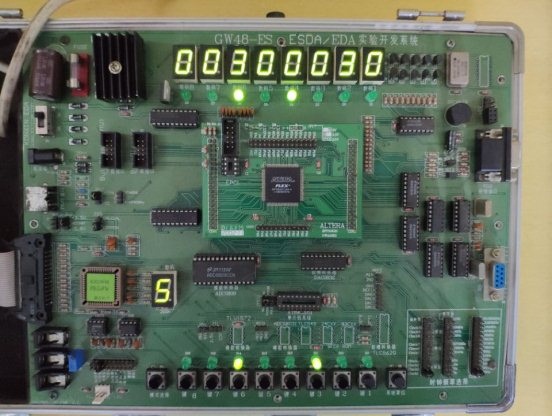

(八)引脚绑定

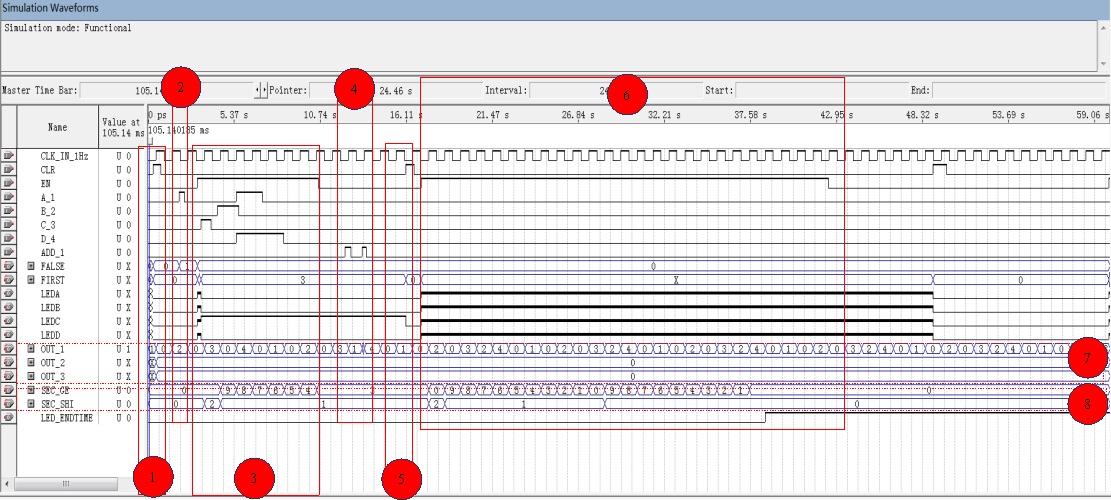

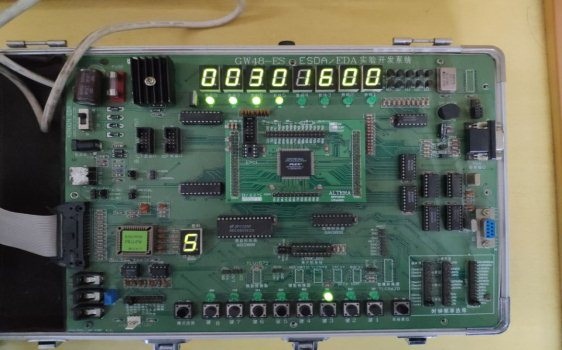

(八)引脚绑定 【1】开始抢答。

【1】开始抢答。

【2】3号组抢答成功。

【2】3号组抢答成功。

END_DESITN_SECOND.rar

(3.36 MB, 下载次数: 54)

END_DESITN_SECOND.rar

(3.36 MB, 下载次数: 54)