(1)熟悉QUARTUS II软件的VHDL使用及设计流程;

(2)掌握VHDL的基本编程方法;

(3)学习基本组合逻辑门电路的设计、仿真和硬件测试。

二、实验原理首先利用QUARTUS II建立工程项目,在工程项目中建立VHDL文件,完成4选1数据选择器的文本编辑输入和仿真测试等步骤,测试通过之后,在实验仪上进行硬件测试,以验证本实验项目设计的功能。

三、主要仪器及耗材本实验使用的主要仪器:PC机,实验仪。

本实验使用的软件:Quartus II9.0。

四、实验内容和步骤1、实验内容

(1)用Quartus II建立工程

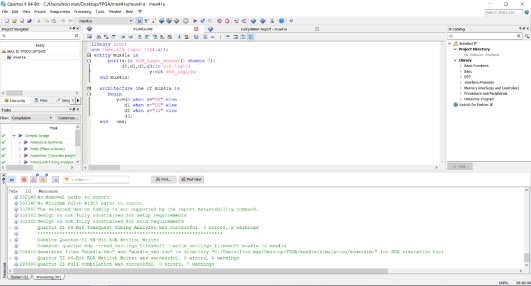

(2)用VHDL语言设计4选1数据选择器

(3)用文本输入法输入

(4)编译,改错,直至程序编译通过

(5)仿真,验证所设计电路的正确性

(6)下载到实验仪,进一步验证所设计电路在目标板上运行的正确性

2、实验步骤

(1)在所使用的计算机上建立自己的文件夹(注:请建立在非C盘中);如图1-1所示。

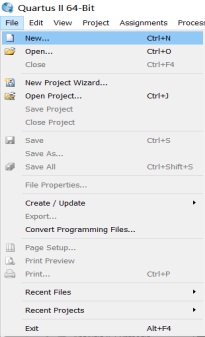

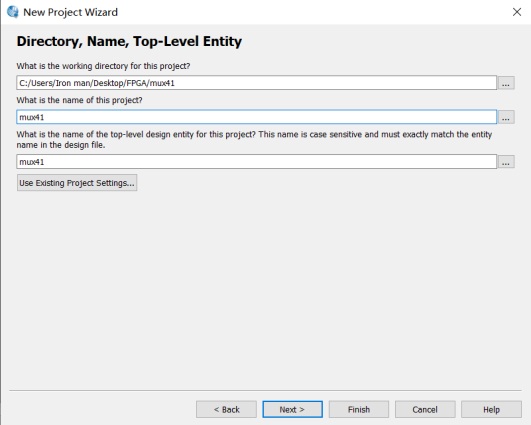

(2)打开Quartus II,选择file-----New Project Wizard...

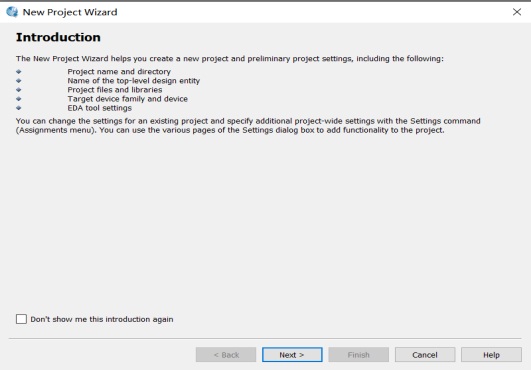

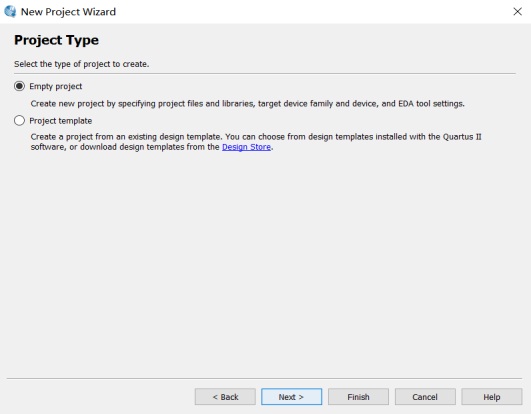

弹出如下窗口,本窗口介绍创建一个工程需要执行的设置,如图1-2、图1-3。点击next。建立完成工程项目,注意观察Quartus II界面变化。

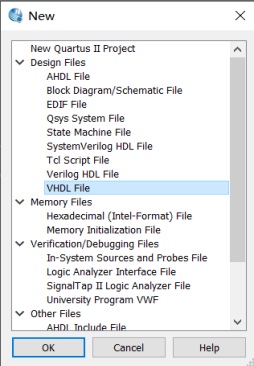

(3)单击工具栏中的new(或菜单命令:File?New),在出现的对话框中选择VHDL File,点击OK,如图1-7。

(6)时序仿真。

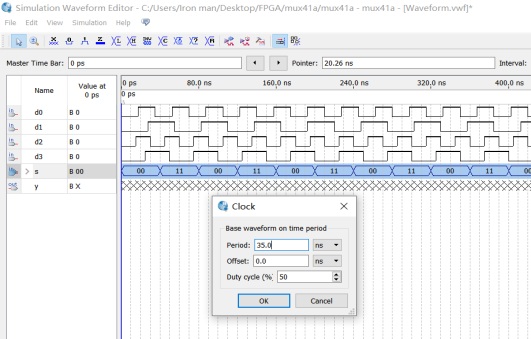

单击new,在出现的对话框中选择第二个标签“Other Files”,选择“Vector Waveform File”,点击OK。

选择菜单View下“Utility Windows”中的“Node Finder”,出现“Node Finder”对话框。在“Node Finder”对话框中,上面中间的“Filter”右边下拉列表框中选择“Pin:all”,点击“list”按钮,将出现的端口信息按需要拖入波形窗口中。

设置输入波形,保存波形文件。如需要修改仿真时间,点击Edit菜单下的End Time。保存波形文件。

时序仿真,仔细读仿真报告,判断电路的正确性;如不正确,修改程序,重新编译、仿真,直至设计的电路完全正确。如下图。

(7)时序仿真通过之后,根据实验仪上的芯片型号,在Quartus II工程项目中选择对应的芯片型号,进行适配(即将设计端口与芯片的管脚进行锁定),重新编译,通过之后,下载到实验仪,进行硬件仿真验证。

为端口选择相应的管脚。选择4号5号管脚,下载成功的话,测量这两管脚应该一个高电平,一个低电平。

下载:在mode中选择JTAG,如果没有出现下载文件,手动选择add file....选择CPLDtest.pof文件。

选择编程器:点击Hadware Setup..弹出对话框中选择,usb blaster,单击close,勾选相应配置选项,单击start开始下载程序。进度条都100%时说明下载完成。0%到100%,本次下载用了25秒钟,如果进度条很快几秒钟就到100%说明没成功下载。最后,万用表测量芯片管脚(4号高电平,5号低电平)。验证程序确实下载OK。

(8)关闭工程。点击菜单下的close project,关闭当前工程项目。

五、实验注意事项1、先在QUARTUS II中进行编辑、编译、仿真测试,直到验证结果正确为止。

2、实验仪使用:先给实验仪连接好电源线后,再上电,然后用数据线将实验仪上左边中部的电子设计下载口(JP4—ByteBlasterII)与FPGA目标板上的JTAG Port连接起来,用下载线将实验仪与PC的并口进行连接;再将其边上的“下载允许”按键拨到“DLOAD”,再通过芯片选择开关切换到“To_FPGA”。连接好后,即可下载进行硬件实测。

六、实验报告要求写出正确的程序,给出正确的仿真波形图,并简要说明实验中遇到的问题及解决方法。

实验一 基于VHDL组合逻辑电路设计.docx

(515.47 KB, 下载次数: 12)

实验一 基于VHDL组合逻辑电路设计.docx

(515.47 KB, 下载次数: 12)

| 欢迎光临 (http://www.51hei.com/bbs/) | Powered by Discuz! X3.1 |