标题: IC设计流程 [打印本页]

作者: 51黑黑黑 时间: 2016-2-21 17:13

标题: IC设计流程

今天彻底无语了,一个学弟问我,从Schematic到GDSⅡ的流程是什么,我竟然答之,仿真、综合、布局布线……事后,觉得不太对,查了一下资料,那里是不太对啊,简直是一点都不对,暴寒啊,也许是自己真是好久没做IC方面的东西了。

一般的IC设计流程可以分为两大类:全定制和半定制,这里我换一种方式来说明。

1.1 从RTL到GDSⅡ的设计流程:

这个可以理解成半定制的设计流程,一般用来设计数字电路。

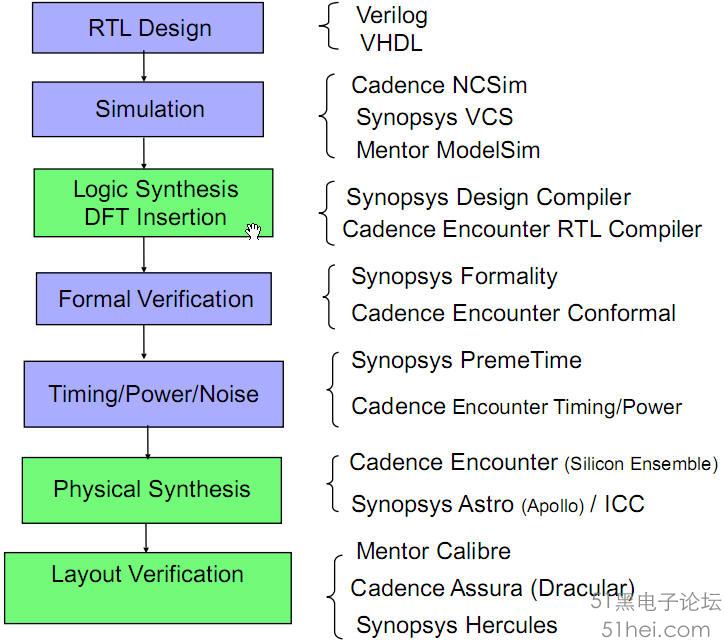

整个流程如下(左侧为流程,右侧为用到的相应EDA工具):

一个完整的半定制设计流程应该是:RTL代码输入、功能仿真、逻辑综合、形式验证、时序/功耗/噪声分析,布局布线(物理综合)、版图验证。

至于FPGA设计,开发起来更加简单,结合第三方软件(像Modelsim和Synplify Pro),两大FPGA厂商Altera和Xilinx自带的QuartusⅡ和ISE开发平台完全可以应付与之有关的开发。

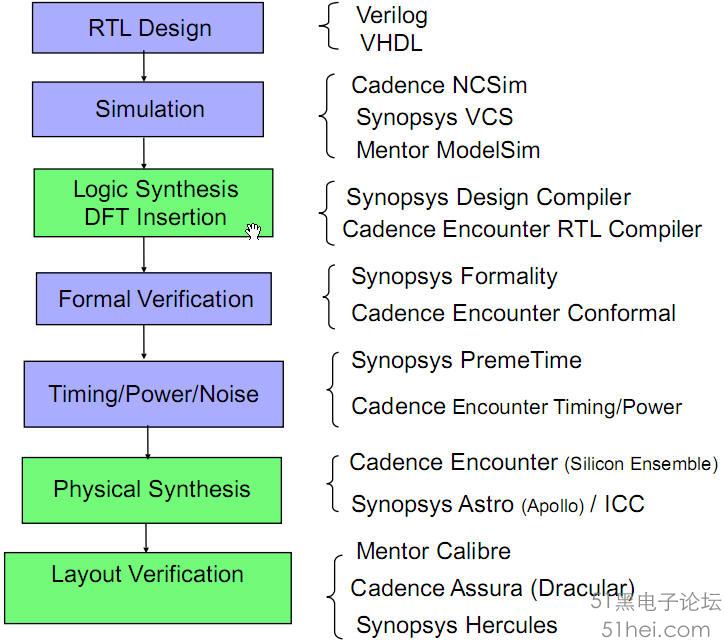

整个完整的流程可以分为前端和后端两部分,前端的流程图如下:

前端的主要任务是将HDL语言描述的电路进行仿真验证、综合和时序分析,最后转换成基于工艺库的门级网表。

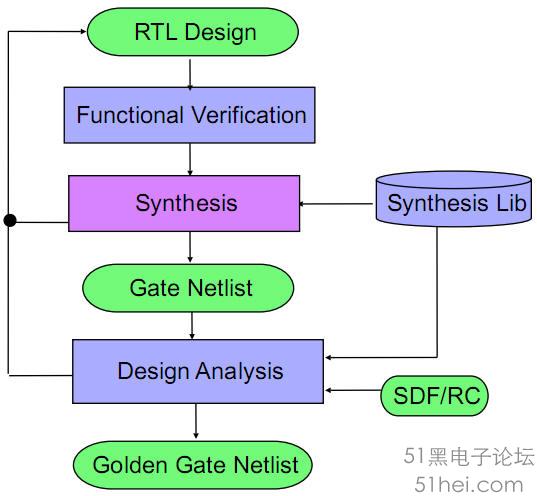

后端的流程图如下,这也就是从netlist到GDSⅡ的设计流程:

后端的主要任务是:

(1)将netlist实现成版图(自动布局布线APR)

(2)证明所实现的版图满足时序要求、符合设计规则(DRC)、layout与netlist一致(LVS)。

(3)提取版图的延时信息(RC Extract),供前端做post-layout 仿真。

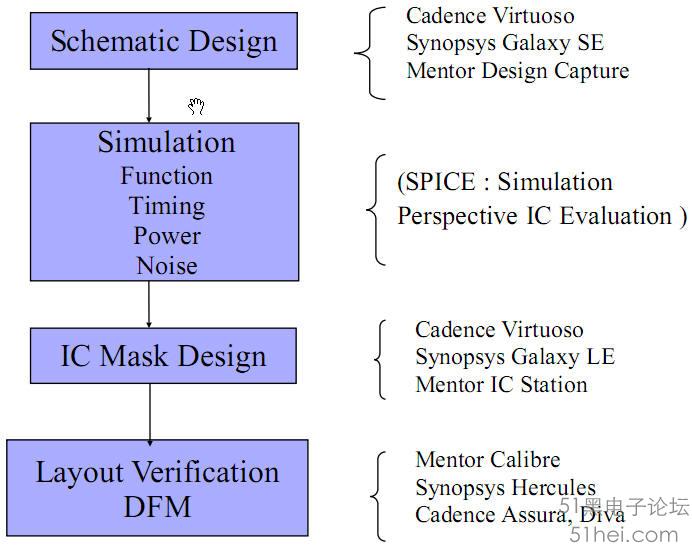

1.2从Schematic到GDSⅡ的设计流程:

这个可以理解成全定制的设计流程,一般用于设计模拟电路和数模混合电路。

整个流程如下(左侧为流程,右侧为用到的相应EDA工具):

一个完整的全定制设计流程应该是:电路图输入、电路仿真、版图设计、版图验证(DRC和LVS)、寄生参数提取、后仿真、流片。

作者: 51黑专家 时间: 2016-5-10 04:06

呵呵,插一个通知...

为让“电子精灵”起到更好的沟通交流效果,现在对五个电子精灵群进行调整。使大家的交流更具针对性,更有利于个人的提高。

调整主要参考目前群总人数及主要电子技术方向。下面列出各群的群号及简单描述,请大家按描述找到与自己比较贴近的群选择加入。因为群资源有限,加入新群后请退出原群,每个号只允许加入到一个群,这也是对大家的尊重,还希望大家配合。转群的话请在新群的加入申请中提出自己是从哪个群转出。

另外需要大家经常交流技术问题,因为一些群资源紧张,对三个月内未发言或总发一些无聊信息以示某人存在的朋友将删除出群。希望大家谅解,如因故长期未能发言被删除群的话,想再重新加入重新申请即可,如果群人数未满不影响加入。

对于电子精灵(庭堂)这个群,申请前需提供加入者本人编写的技术资料文档一份,并且需审查后才能通过(具体哪方面不限,电子相关技术文档即可)。这样是为了保证大家都有一定的水平,并且保证大家都是乐于交流、共享。提交文档以电子邮件方式发送到zjd01@eyou.com。

欢迎喜欢电子喜欢交流的朋友加入。

32973896--电子精灵(闲学):为初学者提供的交流空间,以电子技术交流为主,或者讨论电子相关的话题,让初学者增加对电子的认识。

37051981--电子精灵(单片机):以单片机、ARM技术交流为主。

54039727--电子精灵(DSP、FPGA):以DSP、FPGA、CPLD技术交流为主。

9818976--电子精灵(PCB、模数):以PCB、模电、数电、电磁等技术交流为主。

4521393--电子精灵(庭堂):需有较好电子理论及经验基础,并且乐于分享所掌握知识,进入需提供本人写的技术资料供大家分享(为保障大家的平等权益,共享文档必须是个人编写,且需有较高技术含量)。

| 欢迎光临 (http://www.51hei.com/bbs/) |

Powered by Discuz! X3.1 |