标题: Verilog实现时钟的奇数分频 [打印本页]

作者: 51黑黑黑 时间: 2016-2-23 01:20

标题: Verilog实现时钟的奇数分频

偶数倍分频通过计数器便可以实现,对于奇数倍分频,实现方法为:

产生N计数(N为奇数),在任意计数(>1 & <N)时翻转,实现占空比不为50%的N分频时钟。若是需要产生占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数到某一个值n时输出时钟进行翻转,然后再计数(N-1)/2次,再次进行翻转得到一个占空比非50%奇数n分频时钟。同理,同时进行下降沿触发的模N计数,等计数到n时,输出时钟进行翻转,同样再计数(N-1)/2次,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。两个占空比非50%的n分频时钟进行相或运算,即得到占空比为50%的奇数N分频时钟。

示例:

module odd_division(clk,rst,clk_out);

input clk,rst;

output clk_out;

reg[3:0] count1,count2;

reg clkA,clkB;

parameter N = 5;//the number you want to divid into

assign clk_out = clkA | clkB;

always @(posedge clk or negedge rst)

begin

if(! rst)

begin

count1 <= 1'b0;

clkA <= 1'b0;

end

else if(count1 < (N - 1))

begin

count1 <= count1 + 1'b1;

if(count1 < (N - 1)/2)

clkA <= 0;

else if (count1>=(N-1)/2)

clkA<= 1 ;

end

else

begin

clkA <= 0;

count1 <= 1'b0;

end

end

always @ (negedge clk or negedge rst)

begin

if(! rst)

begin

count2 <= 1'b0;

clkB <= 1'b0;

end

else if(count2 < (N - 1))

begin

count2 <= count2 + 1'b1;

if (count1<(N-1)/2)

clkB <= 0;

else if(count2 >= (N - 1)/2)

clkB <= 1;

end

else

begin

clkB <= 0;

count2 <= 1'b0;

end

end

endmodule

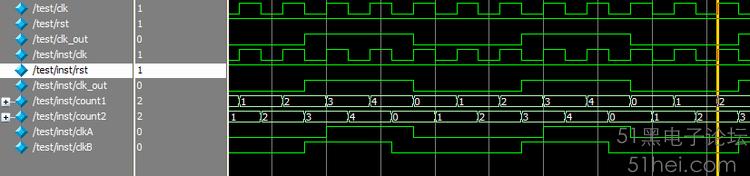

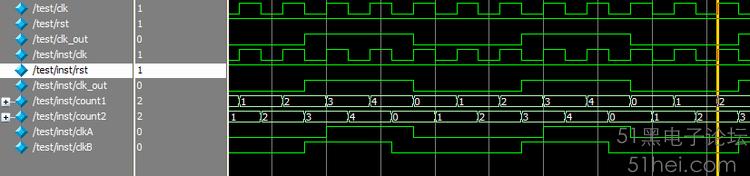

仿真结果:

| 欢迎光临 (http://www.51hei.com/bbs/) |

Powered by Discuz! X3.1 |