|

高速先生成员--姜杰 高速先生今年写了不少AC耦合电容相关的文章,本来已经有点“审美疲劳”了,但是看到这个案例,还是忍不住再写一篇—— 一方面,这个案例完美展示了反焊盘设计两个基本因素的影响;另一方面,似乎有不少Layout工程师都有类似的困惑…… 话说那天早上刚上班,就有人急匆匆的找到高速先生,定睛一看,是近期仿真过的某单板的设计负责人小刘。可是,板子不是刚投出去吗?看着小刘着急忙慌的样子,高速先生有种不太好的预感。 小刘说他设计总结的时候,发现单板上的同一种高速信号的AC耦合电容反焊盘不一样,心里有些没底,需要高速先生帮忙确认。 困惑小刘的两种反焊盘分别长这样:

右边是我们常见的AC耦合电容反焊盘,简简单单的矩形。 左边的反焊盘略复杂,但是稍有设计经验的Layout工程师也能看出来,这里是兼容设计,也就是常说的“叠焊盘”。兼容设计需要同时保证多个链路的阻抗连续性,所以反焊盘根据器件的布局进行挖空。 器件布局都不一样,反焊盘不一样不是很正常吗?

如果只是这个问题,高速先生当然不会写这篇文章啦。小刘的问题显然更有深度:除了大小,为啥这俩反焊盘的挖空层数也不一样呢?板上常规设计AC耦合电容的矩形反焊盘,会比兼容设计的异形反焊盘的挖空层面多了一层?是不是哪里搞错了? 高速先生松了口气,投出去的板子没有问题,小刘的问题是个好问题。 之前的文章介绍过,我们可以把信号路径上的AC耦合电容看作微带线,一段又宽又厚的走线,根据传输线的阻抗理论,线宽越大,铜厚越厚,阻抗就越小。

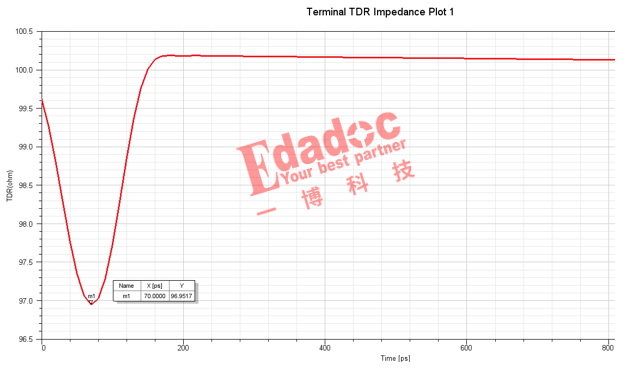

由于AC耦合电容处的阻抗通常比信号走线特征阻抗低,因此需要挖反焊盘来提高阻抗,反焊盘的大小,以及挖空层面的数量,是影响阻抗的两个主要因素。 在回答小刘的问题之前,我们可以看看当前设计走线阻抗控100欧姆时,几种布局方式AC耦合电容的阻抗情况。 常规布局的AC耦合电容(参考第四层GND平面)阻抗96.9欧姆:

兼容设计中的一字布局AC耦合电容阻抗97.6欧姆:

兼容设计中的常规布局AC耦合电容阻抗98欧姆:

各种情况下的阻抗都能比较好的优化到97欧姆左右。 为了更清楚的说明问题,高速先生做了个仿真对比:常规设计的AC耦合电容矩形反焊盘比之前少挖空一层,参考L3层GND平面(与兼容设计的电容反焊盘挖空层数保持一致),阻抗瞬间由96.9欧姆跌落至93.1欧姆!

看到常规布局AC耦合电容反焊盘不同挖空层面的阻抗对比,小刘恍然大悟…… 问题来了: 本案例中AC耦合电容常规设计与兼容设计的反焊盘挖空层数不一样的原因是什么?

|