|

STM32最小系统布线注意事项 本文总结自各种网络资料,版权归原作者所有,此总结仅供学习交流之用

- 1、 VSSA,VDDA

- VSSA,VDDA = 2.0~3.6V:为ADC、复位模块、RC振荡器和PLL的模拟部分提供供电。使用ADC时,VDD不得小于2.4V。VDDA和VSSA必须分别连接到VDD和VSS,VDDA管脚必须连接到2个外部的去藕电容器(10nF瓷介电容+1μF的钽电容或瓷介电容),VDDA管脚必须连接到2个外部的去藕电容器(10nF瓷介电容+1μF的钽电容或瓷介电容)。每一对VDD和VSS管脚都需要使用单独的去藕电容。每对VDD与VSS都必须在尽可能靠近芯片处分别放置一个10nF~100nF的高频瓷介电容。在靠近VDD3和VSS3的地方放置一个4.7μF~10μF的钽电容或瓷介电容。VDD与VDDA之间的电压差不能超过300mV。典型连接:

尽管所有VDD和所有VSS在内部相连,在芯片外部仍然需要连接上所有的VDD和VSS因为导线较细,内部连接负载能力较差,抗干扰的能力也较差,如果漏接VDD或VSS,容易造成内部线路损坏,同时抗干扰能力下降。 电源线和地线之间连接具有良好高频特性的电容,即在靠近电源一端应放置一个0.1μF(104电容)和一个1~10μF的电容。 采用LM1117-3.3V(AMS1117)供电 2、I/O引脚间的串扰:模拟信号线的周围布置地线产生屏蔽,能有效地减小串扰干扰噪声 - 复位信号低脉冲至少保持300ns

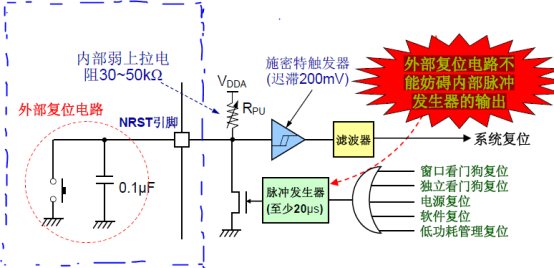

- 在产生内部复位信号时,NRST引脚会输出一个低电平

- 外部复位电路不能妨碍内部脉冲 发生器的输出

复位电路如下图所示: 3、BOOT0,BOOT1管脚 两个管脚在芯片复位时的电平状态决定了芯片复位后从哪个区域开始执行程序。

一般BOOT0和BOOT1跳线都跳到0(地)。只是在ISP下载的情况下,BOOT0=1,BOOT1=0 ,下载完成后,把BOOT0的跳线接回0,也即BOOT0=0,BOOT1=0 。 ISP下载电路: - nJTRST、JTDI、JTMS/SWDIO和JTDO引脚推荐使用10K电阻上拉至VDD,JTCK/SWCLK引脚推荐使用10K电阻下拉至VSS。

- 仿真工具(STLink,JLink)通过20个脚插座的1号脚判断目标板是否供电,通过19号脚可以向目标板供电(3.3V,<100mA)。

- 第1和第2管脚接VDD,其实是对应74HC244的芯片电压,如果74244采用的3.3V的低压芯片的话,这个JTAG-VDD就接3.3V。如果采用的是5V电压的74244的话,这个JTAG-VDD就是5V。

5、RTC时钟电路 RTC时钟要求使用的32.768振荡器的寄生电容是6pF,这个电容区别于振荡器外部接的负载电容;

6、FSMC

对应100pin或144pin,FSMC的功能与I2C是存在冲突的,如果FSMC时钟打开,I2C 1的硬件模式无法工作。这在STM32F10xxx的勘误表中是有描述的。

|