|

基于单片机的液位控制系统的设计 摘要 液位测量广泛应用于工业、经济、生活等领域。本设计以水箱供水为模型,用于对水箱液位信号进行测量监控记录。 基于单片机的液位测量装置具有测量准确、重复性好、功耗低、使用寿命长的特点,是广泛采用的技术。在深入学习科学发展观的同时,电子设备的设计也需融入可持续发展的设计理念。故此,在基于单片机的液位测量装置基础上,扩展实时监控、数据采集、计算机串行通信等功能,从而能够通过科学的方法将液位测量与统计科学结合,合理调度水资源,降低能源消耗。 本文从系统方案选择与论证,硬件电路设计,系统软件与上位机软件设计等几个方面介绍了基于单片机的液位测量监控系统的设计过程,最终实现了液位的实时测量与监控。最后,本文总结了设计过程中出现的问题及解决方法,简要叙述了所获数据的处理方法,引出了进一步设计开发的思路。

目录 引言 第1章 绪论 1.1 课题背景与研究意义 1.2 国内外研究现状及发展 1.3 本课题主要研究内容 第2章 系统总体方案 2.1 系统设计要求 2.2 系统框图 2.3 硬件设计方案 2.3.1 主控模块设计方案 2.3.2 键盘模块设计方案 2.3.3 显示模块设计方案 2.3.4 数据存储模块设计方案 2.3.5 时间模块设计方案 2.3.6 A/D转换模块设计方案 2.3.7 通信模块设计方案 2.3.8 电机控制模块设计方案 第3章 硬件电路设计 3.1 AT89S52硬件设计 3.2 按键设计 3.3 显示单元硬件设计 3.4 存储单元硬件设计 3.5 时间单元硬件设计 3.6 A/D转换单元硬件设计 3.7 通信单元硬件设计 3.8 其他外围电路的设计 第4章 系统软件设计 4.1 系统软件 4.1.1 系统软件编译开发环境 4.1.2 系统主程序流程图 4.1.3 系统初始化 4.1.4 显示与A/D转换的数据处理 4.1.5 按键部分软件设计 4.1.6 显示模块的软件设计 4.1.7 A/D转换模块软件设计 4.1.8 电机控制模块软件设计 4.1.9 通信协议及通信模块软件设计 4.1.10 时间模块软件设计 4.2 上位机软件设计 4.2.1 上位机软件开发编译环境 4.2.2 上位机软件的界面设计 4.2.3 上位机串口通信功能的实现 4.2.4 上位机软件中的数据处理 结论与展望 致谢 参考文献 附录A 系统电路原理图 附录B 外文文献及译文 附录C 主要参考文献的题录及摘要 附录D 系统软件源代码

插图清单

引言

上世纪40年代,电子计算机的诞生,标志着人类电子技术进入了一个新的阶段。1976年单片机的推出为电子电路设计提供了新的思路,也促进了模拟电路向数字电路发展的历程。它在一片芯片上集成了完整的计算机系统。从它的发展来看,低功耗CMOS化、微型单片化、主流与多品种共存的发展趋势更进一步促使了单片机在各个行业的应用。这些应用,很大一方面体现在工业控制中。在工业上,使用单片机可以构成形式多样的控制系统和数据采集系统。 单片机应用发展迅速而广泛。在过程控制中,单片机既可作为主计算机,又可作为分布式计算机控制系统中的前端机,完成模拟量的采集和开关量的输入、处理和控制计算,然后输出控制信号。单片机广泛用于仪器仪表中,与不同类型的传感器相结合,实现诸如电压、功率、频率、湿度、流量、速度、厚度、压力、温度等物理量的测量;在家用电器设备中,单片机已广泛用于电视机、录音机、电冰箱、电饭锅、微波炉、洗衣、高级电子玩具、家用防盗报警等各种家电设备中。在计算机网络和通信、医用设备、工商、金融、科研、教育、国防、航空航天等领域都有着十分广泛的应用。 工程应用中液位的测量常用方法主要有超声波、激光红外测距、机械浮子、压力传感器测距等几种。这些测量方式对一般液位的测量来说各有各的优点,可根据不同的应用场合和要求进行选择。比如,常见的液位控制系统多采用浮标、电极等,这种控制形式结构简单成本低廉,但是控制精度不高,不能进行数值显示;另外容易引起误操作,与上位机进行信息交互比较困难。 随着科技的发展,液位测量技术趋于智能化、微型化、可视化。本设计思想是用单片机做下位机,PC机做上位机,单片机和PC机相结合对水箱液位进行测量和监控。该设计要求具有一定的智能化,可操作性和稳定性好。

第1章 绪论

在工农业生产中,常常需要测量液体液位。随着国家工业的迅速发展,液位测量技术被广泛应用到石油、化工、医药、食品等各行各业中。低温液体(液氧、液氮、液氩、液化天然气及液体二氧化碳等)得到广泛的应用,作为贮存低温液体的容器要保证能承受其载荷;在发电厂、炼钢厂中,保持正常的锅炉汽包水位、除氧器水位、汽轮机凝气器水位、高、低压加热器水位等,是设备安全运行的保证;在教学与科学研究中,也经常碰到需要进行液位控制的实验装置。

液位测量的方法比较多,依据测量方式的不同可分为接触式与非接触式两种类型。 ●接触式测量法 接触式测量法是指测量用传感器直接与容器内存储液体相接触,从而获得测量参数的方法。 1.人工检尺法 人工检尺法可用于测量油罐液位,其历史十分悠久。它利用浸入式刻度钢皮尺测量液位,这种方法具有测量简单、可靠性高、直观、成本低的优点,但人为读数误差大、无法实现自动检测和操作。 2.电参数测量法 常见的有电阻法、光电法、测重法、电容法、浮标法及声光电的反射回波法等。无论怎样,这些方法的关键是利用液位传感器将液位的相对位移量转换成为电压、电流、阻抗等便于进行电处理的物理量。限于篇幅,下面仅简单介绍电容测量法的基本原理。 本方法所使用的电容通常由两块圆柱形极板或一个探极与罐壁构成。当液位不同时,电容器的介电常数就不同,故电容量也不同。在此基础上可以把电容量转化为电压、相移、频率、脉宽等物理量,再进行测量。 电容式液位测量装置通常结构简单、灵敏度高、稳定性好、动态响应快,适合于恶劣的工作环境,生产成本也不高;但电容液位测量器需要考虑温度补偿,且介质的成分、水分、温度、密度等不确定变化因素直接影响测量结果的准确性,另外检测电路比较复杂,尤其是检测微小电容量的变化。 ●非接触式测量法 非接触式测量法包括超声波法、调制型光学法、微波法等。其特点是测量手段并不采用浮子之类的固态物,而是利用声、光、射线、磁场等的能量。液位传感器不和被测介质接触,不受被测介质影响,也不影响被测介质,故适用范围广泛。特别是接触式测量装置不能适用的特殊场合,如高粘度、强腐蚀性、污染性强,易结晶的介质。下面简单介绍超声波法和微波法的测量原理。 超声波法:换能装置将电功率脉冲转换为超声波,射向液面,经液面反射后再由换能器将该超声波转换为电信号,超声波法可用于多液面的测量。 超声波是机械波,传播衰减小,界面反射信号强,且发射和接收电路简单,因而应用较为广泛;但超声波的传播速度受介质的密度、浓度、温度、压力等因素影响,其测量精度往往较低。 微波法:微波通过天线辐射出去,经液面反射后被天线接收,然后由二次电路计算发射信号与接收信号的时间差得出液位。 微波速度受传播介质、温度、压力、液体介电常数的影响很小,但液体界面的波动、液体表面的泡沫、液体介质的介电常数对微波反射信号强弱有很大影响。当压力超过规定数值时,压力对液位测量精度将产生显著影响。对波导管的锈蚀、弯曲和倾斜都会影响测量精度。 ●光纤测量法 光纤液位检测是近年来出现的一种新技术。根据光导纤维中光在不同介质中传输特性的改变对液位进行测量。 光纤液位测量有以下优点:精度高、灵敏度好、抗电磁干扰、耐腐蚀、电绝缘性好、检测现场无电、光路有抗扰性以及便于与计算机连接,便于与光纤传输系统组成网络等。 目前,市面上进行液位测量的仪表种类繁多,但是同时具有测量、监控、数据记录及处理的液位测量装置并不多。在某些工业控制系统中,数据的测量这一基本功能已不能满足现代工业的要求,往往需要对大批数据进行记录,对其进行后期处理分析,实现差错控制、工艺改善、资源优化等一系列工作。为了获得大批量的数据,得到可靠的分析资料,往往需要长期、多网点的监控记录。在液位测量这一领域中,如江河湖海、城市用水等方面,大量数据长时间,多网点的采集记录分析具有普遍的意义。液位的变化分析,有助于人们进一步对自然环境、天气变化甚至是灾害预警提供可靠的支持。

本设计以水箱供水为模型,鉴于单片机液位测量装置的测量准确、重复性能好、功耗低、使用寿命长等特点,设计以单片机为基础的液位测量监控记录系统。具有实时液位测量监控数据处理等功能。 设计具体内容分为以下几个方面: - 系统硬件电路设计以及单片机选型;

- 系统软件设计;

- 上位机软件设计以及上位机与下位机通信设计。

第2章 系统总体方案

2.1 系统设计要求

本设计以水箱供水为模型,鉴于单片机液位测量装置的测量准确、重复性能好、功耗低、使用寿命长等特点,设计以单片机为基础的液位测量监控记录系统。它具有实时测量监控水箱液位高度并显示的功能,并根据实时水量与设置的上、下液位参数的比较,启动电机供水或停止水泵。在启动电机与停止水泵时,实时记录时间点与电机状态。液位测量高度≤5米,测量精度10%,AC220V供电。 可通过上位机软件,可与监控记录系统进行通信,能够从PC机获取当前液位高度、电机状态、设备系统时间、上下液位高度等数据,并可根据需要改变系统默认的参数。同时可以获取设备运行时记录的数据,并能够对数据保存。能够根据一定的算法,计算分析单位时间水箱消耗水量,绘制图形,通过计算分析的结果,可以进行区域用水统筹,降低能源的消耗。

2.2 系统框图

根据系统的设计要求,采用单片机为主控芯片,通过单片机数据地址总线及I/O端口,扩展数据存储模块、A/D转换模块、显示模块、时间模块、串口通信模块以及A/D转换、电机控制等外围电路,从而实现系统所需的设计功能。系统总体方案框图如图2-1: 图2-1 系统总体框图 图中,信号流向仅指示了通过数据地址总线或I/O口上发生的数据信号,不包括控制信号。

2.3 硬件设计方案 2.3.1 主控模块设计方案

单片机作为主控模块,使得在对单片机选型上有了较大的空间。单片机在30多年的发展历程中,形成了多公司、多系列、多型号“百家争鸣”的局面。因而,选择一个合适的单片机有时真的不太容易,要考虑的方面太多。大致总结出以下几点: 1) 单片机的基本参数。例如速度、程序存储器容量、I/O引脚数量等。 2) 单片机的增强功能。例如看门狗、双指针、双串口、RTC(实时时钟)、EEPROM、扩展RAM、CAN接口、I2C接口、SPI接口、USB接口。 3) Flash和OTP(一次性可编程)。 4) 封装:DIP(双列直插),PLCC(PLCC有对应插座)还是贴片。 5) 工作温度范围,工业级还是商业机。 6) 功耗。 7) 工作电压范围。例如设计电视机遥控器,2节干电池供电,至少应该能在1.8~3.6V电压范围内工作。 8) 供货渠道畅通。 9) 价格。 10) 烧录器价格,能否ISP(在线系统编程)。 11) 仿真器。 12) 单片机汇编语言支持。 13) 资料尽量丰富。 14) 抗干扰性能好。 15) 和其他外设芯片放在一起的综合考虑。 根据以上因素:系统的实时性要求不高,因而运算速度无需很快,且系统规模不大,采用分时复用的方式使用总线,对I/O口的数量可以要求进一步降低。使用4路8位I/O接口即可满足设计要求;系统中需要扩展外部存储器对数据进行存储,数据存储量为32KB已满足要求,因此采用16位或准16位地址总线的单片机即可满足设计需要;由于是实验阶段,采用DIP(双列直插)封装的芯片便于实验,暂不考虑实际工业控制中的对外界环境的具体要求;系统采用AC220V供电,且对功耗没有具体要求,使用DC5V为芯片供电,便于系统外围电路的设计;芯片支持ISP可节省仿真器的投入。 综上所述,采用与MCS-51兼容的AT89S52单片机满足设计要求。 AT89S52是一种低功耗、高性能CMOS工艺的8位微控制器,具有8K在线系统可编程Flash存储器。使用Atmel公司高密度非易失性存储器技术制造,与工业80C51产品指令和引脚完全兼容。片上Flash允许程序存储器在系统可编程,亦适于常规编程器,使得AT89S52为众多嵌入式控制应用系统提供高灵活、超有效的解决方案。 AT89S52具有以下标准功能:8k字节Flash,256字节RAM,32位I/O口线,看门狗定时器,2个数据指针,三个16位定时器/计数器,一个6向量2级中断结构,全双工串行口,片内晶振及时钟电路。另外,AT89S52可降至0Hz静态逻辑操作,支持2种软件可选择节电模式。空闲模式下,CPU停止工作,允许RAM、定时器/计数器、串口、中断继续工作。掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一个中断或硬件复位为止。

2.3.2 键盘模块设计方案

键盘在单片机应用系统中是一个很关键的部件,它能实现向单片机输入数据、发送命令等功能,是人工干预单片机系统的主要手段。考虑到本设计实际需要的按键较少,故采用独立式键盘接口电路即可。

2.3.3 显示模块设计方案

显示器是计算机的主要输出设备,在简单的工业控制系统中,常用的显示器有数码管显示器(LED),液晶显示器(LCD)等,该系统仅需显示液位高度,即数字量,采用LED显示器已能满足系统要求。 系统中,要求测量范围≤5m,测量精度为10%,假设测量范围为5m,在10%精度的要求下,其测量的有效值为5*10%=0.5m。因而采用2位LED显示器便能满足设计要求。 在单片机应用系统中,LED显示器的现实方法有两种:静态显示法和动态显示法。静态显示法的优点是显示程序十分简单,显示亮度大,由于CPU不必经常扫描显示器,所以节约了CPU的工作时间。但静态显示也有其缺点,主要是占用I/O口资源较多,硬件成本较高。所以静态显示法常用在显示器数目较少的应用系统中。为了解决静态显示占用I/O口资源的缺点,在软件上采用压缩BCD码输出显示数据,硬件上使用一个8位锁存器74LS273与两个BCD数码显示译码驱动芯片74LS47连接,减少对系统资源的占用时间。由于74LS47译码为共阳极数码管的码表,因而选用8段(带小数点)共阳极LED用于数据显示。高位显示米单位,低位显示分米单位,且高位小数点常亮。单片机使用1位I/O口控制数据的锁存。

2.3.4 数据存储模块设计方案

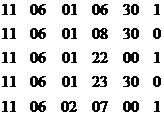

使用AT89S52内部256字节的数据存储器记录数据是远远不够的,因而需要扩展数据存储器进行数据存储。 数据存储器可选择的种类繁多,常用的有随机存取存储器(RAM)、只读存储器(ROM)与闪存(FLASH)。 RAM是存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。 ROM通常指固化存储器(一次写入,反复读取),它的特点与RAM相反。ROM又分一次性固化、光擦除和电擦除重写两种类型。 闪存则是一种不挥发性(Non-Volatile)内存,在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。 NOR和NAND是现在市场上两种主要的非易失闪存技术。 NAND闪存的存储单元则采用串行结构,存储单元的读写是以页和块为单位来进行(一页包含若干字节,若干页则组成储存块,NAND的存储块大小为8到32KB),这种结构最大的优点在于容量可以做得很大,超过512MB容量的NAND产品相当普遍, NAND闪存的成本较低,有利于大规模普及。 NAND闪存的缺点在于读速度较慢,它的I/O端口只有8个,比NOR要少多了。这区区8个I/O端口只能以信号轮流传送的方式完成数据的传送,速度要比NOR闪存的并行传输模式慢得多。再加上NAND闪存的逻辑为电子盘模块结构,内部不存在专门的存储控制器,一旦出现数据坏块将无法修,可靠性较NOR闪存要差。 NOR的特点是芯片内执行(XIP, eXecute In Place),这样应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。NOR的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。 NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。应用NAND的困难在于FLASH的管理和需要特殊的。 可以看出ROM的存储复杂,不适宜实时系统的数据存储。 FLASH是一个不错的解决方案。鉴于系统的复杂程度,暂时不考虑使用FLASH作为存储单元。 根据设计要求,记录某一记录点(电机状态改变时刻)的状态与时间需要6字节数据,即年(2000-2099年)、月(1-12月)、日(1-31日)、时(0-23时)、分(0-59分)、状态(0或1)这些数据,如果系统长时间的工作,将会有大批量的数据产生,假若数据存储空间不够大,将会产生数据的覆盖,从而降低了对数据分析的准确性。因此选用32K字节的数据存储器,可以记录大于5000项记录点数据,考虑到水箱上水与耗水的频繁程度不高,5000项数据已基本满足后期数据处理的需求。在实际应用中,系统设计在不掉电的工作环境下;软件上,上位机软件对数据提取后即可保存在PC机中,5000项数据进行时间上的缓冲是充足的。为节省CPU的工作时间,且由于RAM存储速度快、使用方便等特点,从而可以忽略了RAM掉电数据丢失的缺点。

2.3.5 时间模块设计方案

通过单片机的定时器,可以设计时间功能,然而单片机自身的产生时间数据大大占用了系统的资源,降低了工作效率,甚至影响了其他功能的实现,因此在本设计方案中,采用了外部芯片提供时间信号,用以系统记录时间信息。 目前市场上的时钟芯片很多,如DS1302/DS1307/HT1380/HT1381/PCF8563等。 DS1302是DALLAS公司推出的涓流充电时钟芯片,内含有一个实时时钟/日历和31字节静态RAM,通过简单的串行接口与单片机进行通信。实时时钟/日历电路提供秒、分、时、日期、日、月、年的信息,每月的天数和闰年的天数可自动调整,时钟操作可通过AM/PM指示决定采用24或12小时格式。DS1302与单片机之间能简单地采用同步串行的方式进行通信,仅需用到三个口线(1) RES(复位),(2) I/O(数据线),(3) SCLK(串行时钟)。时钟/RAM的读、写数据以一个字节或多达31个字节的字符组方式通信。DS1302工作时功耗很低,保持数据和时钟信息时功率小于1mW。 DS1302是由DS1202改进而来,增加了以下的特性双电源管脚用于主电源和备份电源供应,Vcc1为可编程涓流充电电源,附加七个字节存储器。它广泛应用于电话、传真、便携式仪器以及电池供电的仪器仪表等产品领域。下面将主要的性能指标作一综合: - 实时时钟具有能计算2100年之前的秒、分、时、日期、星期、月、年的能力,还有闰年调整的能力。

- 31*8位暂存数据存储RAM。

- 串行I/O口方式使得管脚数量最少。

- 宽范围工作电压2.0~5.5V。

- 工作电流2.0V时,小于300nA。

- 读/写时钟或RAM数据时有两种传送方式单字节传送和多字节传送字符组方式。

- 8脚DIP封装或可选的8脚SOIC封装。

- 简单3线接口。

- 与TTL兼容Vcc=5V。

- 可选工业级温度范围-40至+85摄氏度。

- 与DS1202兼容。

- 在DS1202基础上增加的特性:

对Vcc1有可选的涓流充电能力; 双电源管用于主电源和备份电源供应; 备份电源管脚可由电池或大容量电容输入; 附加的7字节暂存存储器。 综上所述,选用DS1302时间芯片完全满足设计的需求。

2.3.6 A/D转换模块设计方案

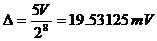

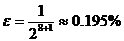

A/D器件和芯片是实现单片机数据采集的常用外围器件。A/D转换器的品种繁多、性能各异,在设计数据采集系统时,首先碰到的就是如何选择合适的A/D转换器以满足系统设计要求的问题。选择A/D转换器件需要考虑器件本身的品质和应用的场合要求。基本上,可以根据以下几个方面的指标选择一个A/D器件。 1) A/D转换器位数 A/D转换器位数的确定,应该从数据采集系统的静态精度和动态平滑性这两个方面进行考虑。从静态精度方面来说,要考虑输入信号的原始误差传递到输出所产生的误差,它是模拟信号数字化时产生误差的主要部分。量化误差与A/D转换器位数有关。一般把8位以下的A/D转换器归为低分辨率A/D转换器,9~12位的称为中分辨率转换器,13位以上的称为高分辨率转换器。10位以下的A/D芯片误差较大,11位以上对减小误差并无太大贡献,但对A/D转换器的要求却提得过高。因此,取10位或11位是合适的。由于模拟信号先经过测量装置,再经A/D转换器转换后才进行处理,因此,总的误差是由测量误差和量化误差共同构成的。A/D转换器的精度应与测量装置的精度相匹配。也就是说,一方面要求量化误差在总误差中所占的比重要小,使它不显著地扩大测量误差;另一方面必须根据目前测量装置的精度水平,对A/D转换器的位数提出恰当的要求。 目前,大多数测量装置的精度值不小于0.1%~0.5%,故A/D转换器的精度取0.05% ~ 0.1%即可,相应的二进制码为10~11位,加上符号位,即为11~12位。当有特殊的应用时,A/D转换器要求更多的位数,这时往往可采用双精度的转换方案。 2) A/D转换器的转换速率 A/D转换器从启动转换到转换结束,输出稳定的数字量,需要一定的转换时间。转换时间的倒数就是每秒钟能完成的转换次数,称为转换速率。 确定A/D转换器的转换速率时,应考虑系统的采样速率。例如,如果用转换时间为100us的A/D转换器,则其转换速率为10KHz。根据采样定理和实际需要,一个周期的波形需采10个样点,那么这样的A/D转换器最高也只有处理频率为1KHz的模拟信号。把转换时间减小,信号频率可提高。对一般的单片机而言,要在采样时间内完成A/D转换以外的工作,如读数据、再启动、存数据、循环计数等已经比较困难了。 3) 采样/保持器 采集直流和变化非常缓慢的模拟信号时可不用采样保持器。对于其他模拟信号一般都要加采样保持器。如果信号频率不高,A/D转换器的转换时间短,即采样高速A/D时,也可不用采样/保持器。 4) A/D转换器量程 A/D转换时需要的是双极性的,有时是单极性的。输入信号最小值有的从零开始,也有从非零开始的。有的转换器提供了不同量程的引脚,只有正确使用,才能保证转换精度。在使用中,影响A/D转换器量程的因素有:量程变换和双极性偏置;双基准电压;A/D转换器内部比较器输入端的正确使用。 5) 满刻度误差 满度输出时对应的输入信号与理想输入信号值之差。 6) 线性度 实际转换器的转移函数与理想直线的最大偏移。 ADC0804是单路8位逐次比较型双极性输入A/D转换器,转换时间小于  。量化间隔:  (2-1) 绝对量化误差:  (2-2) 相对量化误差:  (2-3) 在液位传感器误差与参考电压误差不大的情况下,ADC0804是完全满足设计误差要求的。

2.3.7 通信模块设计方案

AT89S52单片机内部有一个全双工异步串行I/O接口,占用P3.0和P3.1两个引脚。利用该接口,可实现系统与上位机的通信。 不同设备间串口通信的过程中,需要采用相同的的接口标准才能通信。 典型的串行通讯标准是RS232和RS485,它们定义了电压,阻抗等,但不对软件协议给予定义。 RS-232C标准(协议)的全称是EIA-RS-232C标准,其中EIA(Electronic Industry Association)代表美国电子工业协会,RS(EcommededStandard)代表推荐标准,232是标识号,C代表RS232的最新一次修改(1969),在这之前,有RS232B、RS232A。。它规定连接电缆和机械、电气特性、信号功能及传送过程。 区别于RS232,RS485的特性包括: 1) RS-485的电气特性:逻辑“1”以两线间的电压差为+(2~6)V表示;逻辑“0”以两线间的电压差为-(2~6)V表示。接口信号电平比RS-232-C降低了,就不易损坏接口电路的芯片,且该电平与TTL电平兼容,可方便与TTL电路连接。 2) RS-485的数据最高传输速率为10Mbps。 3) RS-485接口是采用平衡驱动器和差分接收器的组合,抗共模干扰能力增强,即抗噪声干扰性好。 4) RS-485接口的最大传输距离标准值为4000英尺,实际上可达3000米,另外RS-232-C接口在总线上只允许连接1个收发器,即单站能力。而RS-485接口在总线上是允许连接多达128个收发器。即具有多站能力,这样用户可以利用单一的RS-485接口方便地建立起设备网络。 因RS-485接口具有良好的抗噪声干扰性,长的传输距离和多站能力等上述优点就使其成为首选的串行接口。 PC机作为上位机,一般情况下带有RS-232C通信接口,鉴于RS-485接口的优点与系统实际工作环境的需要,系统采用RS-485接口标准,使用RS-232/RS-485转换器与PC机连接进行通信。 MAX485接口芯片是Maxim公司的一种RS-485芯片。采用单一电源+5V工作,额定电流为300μA,采用半双工通讯方式。它完成将TTL电平转换为RS-485电平的功能。

2.3.8 电机控制模块设计方案

由于设计中没有规定水泵电机的参数规格,而且不同型号的水泵参数不尽相同,电气参数的不同使得在电路上的设计差异较大,因此在此仅作理论演示。 选用继电器作为电机控制的元件。 继电器是一种电子控制器件,它具有控制系统(又称输入回路)和被控制系统(又称输出回路),通常应用于自动控制电路中,它实际上是用较小的电流去控制较大电流的一种“自动开关”。故在电路中起着自动调节、安全保护、转换电路等作用。 继电器主要产品技术参数: 1) 额定工作电压。是指继电器正常工作时线圈所需要的电压。根据继电器的型号不同,可以是交流电压,也可以是直流电压。 2) 直流电阻。是指继电器中线圈的直流电阻,可以通过万能表测量。 3) 吸合电流。是指继电器能够产生吸合动作的最小电流。在正常使用时,给定的电流必须略大于吸合电流,这样继电器才能稳定地工作。而对于线圈所加的工作电压,一般不要超过额定工作电压的1.5倍,否则会产生较大的电流而把线圈烧毁。 4) 释放电流。是指继电器产生释放动作的最大电流。当继电器吸合状态的电流减小到一定程度时,继电器就会恢复到未通电的释放状态。这时的电流远远小于吸合电流。 5) 触点切换电压和电流。是指继电器允许加载的电压和电流。它决定了继电器能控制电压和电流的大小,使用时不能超过此值,否则很容易损坏继电器的触点。 根据以上的参数,结合设计的演示性,选用额定工作电压120VAC/24VDC,工作电流3A,控制电压5VDC的小型继电器。

第3章 硬件电路设计

3.1 AT89S52硬件设计

AT89S52引脚定义及功能介绍如图3-1。

P0口:P0口是一个8位漏极开路的双向I/O口。作为输出口,每位能驱动8个TTL逻辑电平。对P0端口写“1”时,引脚用作高阻抗输入。当访问外部程序和数据存储器时,P0口也被作为低8位地址/数据复用。在这种模式下,P0具有内部上拉电阻。在FLASH编程时,P0口也用来接收指令字节;在程序校验时,输出指令字节。程序校验时,需要外部上拉电阻。 P1口:P1口是一个具有内部上拉电阻的8位双向I/O口,P1输出缓冲器能驱动4个TTL逻辑电平。对P1端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。此外,P1.0和P1.2分别作定时器/计数器2的外部计数输入(P1.0/T2)和定时器/计数器2的触发输入(P1.1/T2EX),具体如下所示: - 在FLASH编程和校验时,P1口接收低8位地址字节。

- 引脚号第二功能:

P1.0/T2 (定时器/计数器T2的外部计数输入),时钟输出 P1.1/T2EX (定时器/计数器T2的捕捉/重载触发信号和方向控制) P1.5 MOSI (在系统编程用) P1.6 MISO (在系统编程用) P1.7 SCK (在系统编程用) P2口:P2口是一个具有内部上拉电阻的8位双向I/O口,P2输出缓冲器能驱动4个TTL逻辑电平。对P2端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。在访问外部程序存储器或用16位地址读取外部数据存储器(例如执行MOVX @DPTR)时,P2口送出高八位地址。在这种应用中,P2口使用很强的内部上拉发送1。在使用8位地址(如MOVX @RI)访问外部数据存储器时,P2口输出P2锁存器的内容。在FLASH编程和校验时,P2口也接收高8位地址字节和一些控制信号。 P3口:P3口是一个具有内部上拉电阻的8位双向I/O口,P3输出缓冲器能驱动4个TTL逻辑电平。对P3端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。P3口亦作为AT89S52特殊功能(第二功能)使用,如下表所示。

表3-1 端口引脚第二功能

此外,P3口还接收一些用于FLASH闪存编程和程序校验的控制信号。 RST——复位输入。当振荡器工作时,RST引脚出现两个机器周期以上高电平将使单片机复位。 ALE/PROG——当访问外部程序存储器或数据存储器时,ALE(地址锁存允许)输出脉冲用于锁存地址的低8位字节。一般情况下,ALE仍以时钟振荡频率的1/6输出固定的脉冲信号,因此它可对外输出时钟或用于定时目的。要注意的是:每当访问外部数据存储器时将跳过一个ALE脉冲。对FLASH存储器编程期间,该引脚还用于输入编程脉冲(PROG)。如有必要,可通过对特殊功能寄存器(SFR)区中的8EH单元的D0位置位,可禁止ALE操作。该位置位后,只有一条MOVX和MOVC指令才能将ALE激活。此外,该引脚会被微弱拉高,单片机执行外部程序时,应设置ALE禁止位无效。 PSEN——程序储存允许(PSEN)输出是外部程序存储器的读选通信号,当AT89S52由外部程序存储器取指令(或数据)时,每个机器周期两次PSEN有效,即输出两个脉冲,在此期间,当访问外部数据存储器,将跳过两次PSEN信号。 EA/VPP——外部访问允许,欲使CPU仅访问外部程序存储器(地址为0000H~FFFFH),EA端必须保持低电平(接地)。需注意的是:如果加密位LB1被编程,复位时内部会锁存EA端状态。如EA端为高电平(接Vcc端),CPU则执行内部程序存储器的指令。FLASH存储器编程时,该引脚加上+12V的编程允许电源Vpp,当然这必须是该器件是使用12V编程电压Vpp。 XTAL1:振荡器反相放大器和内部时钟发生电路的输入端。 XTAL2:振荡器反相放大器的输出端。 为了便于接下来的说明,单片机各管脚网络标号定义如图3-1。 要使单片机按照设计要求正常工作,完整单片机最基本的工作要求,考虑到系统无需精确地定时功能,且为了方便串口通信波特率的计算,采用11.0592MHz的晶振提供系统时钟。并附加复位电路,组成单片机最小系统。根据电路设计规范和AT89S52芯片手册,设计时钟电路与复位电路如图3-2: 图3-2 复位电路及时钟电路 图中网络标号RST连接单片机RST引脚,具有上电复位与手动复位的功能;XTAL1与XTAL2连接单片机XTAL1和XTAL2引脚,且并联两个30pF匹配电容使晶振起振。 由于单片机P0口作普通I/O口时不能输出高电平,因此需接上拉电阻,实际电路中,使用8*10KΩ电阻作为上拉电阻。

3.2 按键设计

键盘在单片机应用系统中是一个很关键的部件,它能实现向单片机系统输入数据、发送命令等功能,是人工干预单片机的主要手段。考虑到本设计实际需要的按键较少,故采用独立式键盘接口电路。它是将每个独立按键按一对一的方式直接接到单片机的I/O口上,通过程序扫描查询方式实现与单片机系统交互的。在程序查询方式下,通过I/O端口读入按键状态,当有按键按下时,相应的I/O端口变为低电平,而未被按下的按键在上拉电阻作用下为高电平,这样通过读I/O口的状态判断是否有按键按下。系统按键电路如图3-3所示。 下图中,S2~S5便是控制显示用的按键。其作用就是通过按动它们实现对高低警戒液位的设置。具体来说,S3、S4分别实现数字的增一与减一,S2、S5则作为高低警戒液位的模式选择和确认键。 图3-3 系统按键电路

3.3 显示单元硬件设计

在显示单元上,使用了74LS273带公共时钟复位八位触发器与74LS47共阳极BCD显示译码驱动芯片。两个芯片的管脚图如图3-4:

74LS273与74LS47引脚功能说明: 74LS273:1脚是复位CLR,低电平有效,当1脚是低电平时,输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部输出0,即全部复位; 当1脚为高电平时,11(CLK)脚是锁存控制端,并且是上升沿触发锁存,当11脚有一个上升沿,立即锁存输入脚3、4、7、8、13、14、17、18的电平状态,并且立即呈现在在输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)上。 74LS47上BI/ROB,LI,RBI引脚为控制引脚,主要用于测试和脉冲控制,均为低电平有效,设计上不适用此项功能,因此均接高电平。A0~A3是BCD输入,分解74LS273输出的高、低四位。a~g用于共阳极数码管的相应管脚的连接。 为了保护LED数码管,在74LS47与LED之间添加限流电阻,以满足数码管的工作需要。 根据以上的设计思路,设计电路图如图3-5:

3.4 存储单元硬件设计

存储模块的硬件设计比较简单,由于AT89S52单片机为数据线与低8位地址线复用,需要使用地址锁存芯片74LS373。上文中已叙述,使用32KRAM作为存储芯片,因此选用与51系列兼容的62256随机数据存储器。 该模块中使用的两个芯片管脚功如图3-6: 在62256中,A0~A14管脚为地址总线,共15位,寻址范围可达到32kB;I/O0~I/O7为8位三态双向数据接口;Vcc,Vss为电源和地;CS是片选接口,低电平有效;OE/WE分别是读选通和写选通数据输入输入线,低电平有效。

图3-7 存储的单元电路

74LS373引脚位置和功能与74LS273差异不大,区别在于其1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态。74LS273也可以作为地址锁存器来用,作锁存器时,对273来说,1(CLR)脚必须接高电平,ALE信号经过反相后接11脚(因为单片机的ALE信号是以下降沿方式出现)对373来说,1脚接低电平,保证使能,11脚直接接单片机的ALE信号。 按照常规的连接方法设计电路图3-7如示。

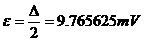

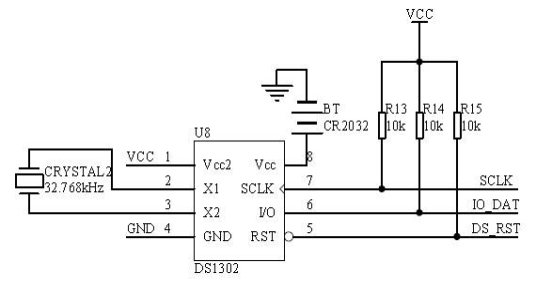

3.5 时间单元硬件设计

DS1302因其较小的体积,占用I/O口资源少等特点,是常用的时间芯片。此次设计采用DIP-8封装,管脚功能如图3-8: 图3-8 DS1302引脚图

其中Vcc1为后备电源,Vcc2为主电源。在主电源关闭的情况下,也能保持时钟的连续运行。DS1302由Vcc1或Vcc2两者中电压较大者供电。当Vcc2大于Vcc1+0.2V时,Vcc2供电,当Vcc2小于Vcc1时,DS1302由Vcc1供电。X1和X2是振荡源接口,外接32.768kHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传输。RST输入有两种功能:首先RST接通控制逻辑,允许地址/命令序列送入移位寄存存器;其次,RST提供终止单字节或多字节数据的传送手段。当RST为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果传送过程中RST置为低电平,则会终止此次传输,I/O引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,RST必须保持低电平。只有在SCLK为低电平时,才能将RST置为高电平。I/O为串行数据输入输出端。SCLK始终是输入端,用来输入串行时钟信号。根据DS1302的特点,设计电路如图3-9: 图3-9 时间单元电路

在实际应用中,起控制、输入输出的三个端口上拉较弱,容因产生信号串扰,因此加上了上拉电阻与单片机P1口相连,加强信号的稳定性;为了保证时钟的可靠性,在Vcc1上使用了CR2032纽扣电池作为备用电源,输出电压为3V,从而保证了系统掉电状态下,时钟能够继续保持运行。 3.6 A/D转换单元硬件设计

A/D转换模块是系统中较为重要的一部分,由于涉及到模拟部分,A/D转换器的结构较为复杂。

以下是ADC0804管脚及功能的介绍: /CS 芯片选择信号。 /RD 外部读取转换结果的控制输出信号。/RD为高电平时,DB0~DB7处于高阻抗:/RD为低电平时,数据才会输出。 /WR 用来启动转换的控制输入,相当于ADC的转换开始(/CS=0时),当/WR由高电平变为低电平时,转换器被清除;当/WR回到高电平时,转换正式开始。 CLK IN,CLK R 时钟输入或接振荡元件(R,C)频率约限制在100kHZ~1460kHZ,如果使用RC电路则其振荡频率为1/(1.1RC)。 /INTR 中断请求信号输出,低地平动作。 VIN(+) VIN(-) 差动模拟电压输入。输入单端正电压时,VIN(-)接地;而差动输入时,直接加入VIN(+) VIN(-)。 AGND,DGND 模拟信号以及数字信号的接地。 VREF 辅助参考电压。 DB0~DB7 8位的数字输出。 VCC 电源供应以及作为电路的参考电压。 设计满偏电压为5V,则VREF辅助参考电压为5V/2=2.5V,在10%的误差范围内,无需过分苛刻参考电压的电压源,由于系统中DC5V供电,采用两只相同阻值电阻分压,便能近似得到2.5V的参考电压。 系统中使用10K电阻与150pF电容组成RC振荡电路,根据技术手册计算公式:  (3-1) 其振荡频率约为606kHz,满足芯片要求。 另外,以阻抗型液位传感器为模型,液位传感器阻值变化与液位的高度是成正比的,因此需要将电阻值转换为电压值匹配A/D转换器。常用的阻抗-电压转换法如欧姆法。由于被测阻抗两端电压正比于被测电阻,可把被测阻抗转换为电压测量。即  (3-2) 式中,  是转化电压,  恒定电流,  为被测电阻,  为比例系数。因此,液位高度的变化同样正比于输入电压,故而A/D转换器输出的数据正比于液位高度。为了简化设计调试过程,使用系统内部5V电压作为模拟输入,VIN(-)直接接地,通过接入传感器分压将阻抗转换为电压信号,接入电位器可实现模拟输入。 根据以上参数分析,设计电路如图3-11:

图3-11 A/D转换单元电路图 3.7 通信单元硬件设计

MAX485仅有8个管脚,电路设计比较简单。

RO引脚接到单片机串口接收引脚RXD(P3.0),DI引脚接到单片机串口发送引脚TXD(P3.1)。由于MAX485为半双工通信方式,不能同时发送和接收数据,只能通过控制RE和DE引脚的状态来进行发送数据和接收数据的转换。为了节省单片机I/O口资源,将RE和DE引脚连在一起,输入低电平时,MAX485处于接收状态;输入高电平时,其处于发送数据状态。定义RE和DE连接在一起的网络标号为E,接入单片机P1口,用于发送与接收的转换。A,B端为发送接收差分信号端,一般需在A,B端之间加匹配电阻,匹配电阻为120Ω。 硬件电路如图3-13: 图3-13 串行通信模块电路图 3.8 其他外围电路的设计

继电器电路设计。由于使用单片机I/O口的驱动电流较弱,不满足继电器吸合电流参数的要求,所以需使用三极管驱动继电器吸合。设计电路如图3-14。 为了防止电源尖峰脉冲引发的噪声干扰以及高频信号线间的耦合干扰,在电源入口处及芯片顶端或底端,接入去耦电容,以增强系统的稳定性。 电源指示灯设计如图3-15。 图3-14 继电器部分电路图 图3-15 电源指示灯电路图

第4章系统软件设计

4.1 系统软件

4.1.1 系统软件编译开发环境

8051系类单片机共拥有111条系统指令,可实现51种基本操作。然而汇编语言指令却有程序的可读性低,程序开发人员的开发时间长与开发难度大,程序移植性差等缺点。 C语言是一种编译型程序设计语言。它兼顾了多种高级语言的特点,并具备汇编语言的功能。用C语言来编写目标系统软件,会大大缩短开发周期,增加软件的可读性,便于改进和扩充。用C语言进行51系列单片机程序设计是单片机开发与应用的必然趋势。 KEIL C51开发工具套件可用于汇编C语言程序、汇编源程序,链接和定位目标文件和库,创建HEX文件以及调试目标程序。 本设计使用KEIL C51 μVision3为开发编译环境,使用C语言编写程序,实现各模块功能设计。

4.1.2 系统主程序流程图

系统主程序的功能主要是完成对单片机的初始化,设置警戒液位的上下限,实时显示液位值以及键盘扫描等工作。主程序流程图如图4-1所示。

4.1.3 系统初始化

该模块在系统上电开机时将系统端口、数据存储区、标志位、指针、地址等赋予有含义的值。具体分为以下几个模块列表描述。

表4-1 初始化参数及含义 | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | 初始化系统时间为2011年1月1日 0时0分0秒星期六 其中sec,min,hr,date,mon,day,year 依次为秒、分、时、日、月、星期、年 | | | | | | | | | | | | | | | | | | | | | | | | | | 初始化过程中,调用A/D转换模块获得首次液位数据,同时将其显示,完成初始化工作 |

图4-1 主程序流程图 4.1.4 显示与A/D转换的数据处理

系统中,显示输出的要求为压缩BCD码,而A/D转换输入的数据是8位16进制码,因此在实现显示之前需要编码的转换。对8位A/D转换器而言,其十六进制、相对满偏电压比率、相对电压幅值的关系对应如表4-2:

表4-2 A/D转换幅值数据关系对照表

综上,电压幅值与液位高度在数值上是相等的。为了通过LED直观显示液位高度,进行转换的思路如下: 设输入8位二进制数据为  ,  的商即为以分米为单位的液位高度数据,余数为以厘米为单位的数据,由于显示位数仅为2位,最低位为分米,固使用“二舍三入”的办法保留分米单位的整数倍数据  。为了将这个数据转换为为压缩BCD码,再将  ,得到的商左移四位(相当于乘以16)为压缩BCD码高四位,余数为压缩BCD码低四位,二者相加,就是最终的结果。 显示转换部分程序简略如下: uchar dis_transform(uchar num) { uchar ac, quotient, play, mid ; ac = num%5; quotient = (num-ac)/5; if(ac>2) quotient++; ac=quotient%10; mid=(quotient-ac)/10; play=ac+mid*16; return play; }

4.1.5 按键部分软件设计

由于使用的按键较少,所以本文采用了独立式键盘,即每个按键单独占用一根口线。在程序查询方式下,通过I/O端口读入按键状态,当有按键按下时,相应的端口变为低电平,这样通过读入I/O口状态判断是否有按键按下。查询式键盘的程序流程图如下:

下面给出键盘扫描的主程序,其分支程序省略。 void judge_key(void) {uchar Key_value=0; Key_value=P3&0x3c; /*读取键值*/ switch(Key_value) { case 0x38:delay(30000); /*调用延时子程序*/ if(Key_value==(P3&0x3c)) /*进行判断按键是否为干扰*/ {manage_key2();break;} /*调用子函数*/ else break; ……

case 0x1c:delay(30000); if(Key_value==(P3&0x3c)) {manage_key5();break;} else break; default:break; } }

4.1.6 显示模块的软件设计

由于使用了静态锁存显示,需要对显示数据进行处理后进行锁存控制。硬件设计中使用了74LS273锁存数据。它的特点是在ALE输入信号的下降沿到来时锁存信号,因此首先置控制引脚高电平,延迟几个时钟周期待信号稳定,P0口输出处理后的数据,同样延迟几个时钟周期待信号稳定,控制引脚置低电平,数据锁存,显示输出。 液位显示部分程序简略如下: display() { DIS=0; _nop_(); _nop_(); _nop_(); P0=dis_transform(prelq); _nop_(); _nop_(); _nop_(); DIS=1; }

4.1.7 A/D转换模块软件设计

A/D转换的控制变量有两个,即adWR与adRD;上文中已说明了它的功能,故不再重复。该模块分为两个阶段,第一阶段是为A/D转换启动控制,通过adWR复位→延迟→置位完成。第二阶段是数据的提取过程,由于P0口做输入时的特性,首先软件上将P0口寄存器置为0xFF,延迟适当时间后adRD复位,输出A/D转换结果,随之通过P0口读入数据,还原adRD为高,该阶段结束。两个阶段中可加如适当的延迟,以满足ADC0804 100ns的转换时间。

4.1.8 电机控制模块软件设计

本设计采用单片机主控芯片控制继电器外围电路,用于驱动电机的启动与关停。其程序流程图如图4-3所示。以下是液位检测与电机控制部分源程序代码: check_lq() { ad_start(); _nop_(); _nop_(); _nop_(); ad_read(); if(prelq>=uplq && key==1) { RELAY=1; key=0; makemark(1); } else if(prelq<=downlq && key==0) { RELAY=0; key=1; makemark(0); } }

4.1.9 通信协议及通信模块软件设计

1) 通信协议 为了使PC上位机与设备实现有意义的通信,设计了简单的通信协议。 通信波特率设计为4800bps,过高的波特率在没有检纠错方式的情况下易发生数据的丢失,过低的波特率会使传输变慢;8位有效数据位;无奇偶校验位;1位停止位。传送以字节为单位,发送命令与数据。通信协议命令控制字如表4-3。 软件设计上,系统以查询的方式检测上位机的命令控制字,并及时进入各响应函数予以响应。通信检测流程如图4-4所示。

表4-3 通信协议 | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | 响应读当前液位及电机状态指令,发送2字节液位数据及电机状态 |

图4-4 通信检测流程图

2)通信模块的控制 该模块在控制上设计两个函数,一个是发送函数,另一个是接收函数。由于采用半双工的通信方式,需要控制变量E的置位与复位转换发送与接收的状态。 发送的过程:置E为1,使系统处于发送数据状态;将数据写入串行通信缓冲区SBUF; 等待,直到发送完毕,将E清0,返回接收状态。 接收过程:清零E,使系统处于接收状态;等待,直到接收完毕,读串行通信缓冲区SBUF;继续保持接收状态。 这两个子程序在其他函数需要进行串口通信时调用即可实现与上位机的串行通信。

4.1.10 时间模块软件设计

DS1302内部寄存器的定义直接影响着软件的设计,大概可分为时间控制寄存器和内部RAM寄存器。其中: - CH: 时钟停止位寄存器2的第7位12/24小时标志

CH=0 振荡器工作允许bit7=1,12小时模式 CH=1 振荡器停止bit7=0,24小时模式 WP=0 寄存器数据能够写入 AP=1 下午模式 WP=1 寄存器数据不能写入 AP=0 上午模式 TCS=1010 使能涓流充电 DS=01 选择一个二极管 TCS=其它 禁止涓流充电 DS=10 选择两个二极管 DS=00 或11, 即使TCS=1010, 充电功能也被禁止

表4-4 RS状态标志及含义

由于DS1302数据传输方式为串行移位输入输出。地址、数据的写操作流程是相同的。地址没有读操作。无论是读还是写,二者结构类似。读写的核心是产生SCLK移位信号与移位,读操作是将数据从DS1302的I/O口移入单片机,写操作是将数据从单片机移入DS1302时钟芯片。我们最终处理的对象是时间数据或状态数据,在获取数据时,首先写入地址,然后读取数据;写入数据时,先写入地址,再输出数据。完成时间的模块软件的设计。DS1302读写程序如下: ds_read() { uchar j; iodat=0x00; for(j=8;j>0;j--) { iodat=iodat>>1; odat7=IO_DATA; _nop_(); SCLK=1; _nop_(); SCLK=0; } }

ds_write(uchar ad) { uchar i; ddat=ad; for(i=8;i>0;i--) { IO_DATA=ddat0; _nop_(); SCLK=1; _nop_(); ddat=ddat>>1; SCLK=0; } }

51系列单片机中有片外存储器读写的指令MOVX,无需用户复杂的控制、输入出处操作,故不再陈述。

4.2 上位机软件设计

4.2.1 上位机软件开发编译环境

VC++是Microsoft(微软)开发的在Windows平台下构建32位应用程序的强大而又复杂的可视化开发平台,它是世界上使用最多的开发工具之一。VC++的应用非常广泛,从桌面应用程序到服务器端软件,从系统软件到应用软件,从单击程序到分布式应用程序,从图形图像处理到游戏的开发,VC++无处不在。 目前,在VC++发展历程下已有了产生了多个版本。版本的更新带来了更美观的操作界面,更人性化的操作方式,增强了某些模块的功能。同时,面向不同开发对象推出了多项产品。VC++6.0是Microsoft早期推出的产品,但是其以界面简洁、占用资源少、操作方便、相关资料丰富等优点,仍为广大程序开发人员使用。 本系统上位机软件使用VC++ 6.0开发Windows平台下的应用软件。 上位机软件设计要求: 上位机软件是操作人员与设计系统交互的一个平台。系统的大多数辅助功能通过上位机软件与系统设备通信控制完成。上位机软件在已有的系统软硬件基础上有较大的开发空间,强大功能的上位机软件是整个系统不可缺少的一部分。因此,此次设计的上位机软件具有如下功能: - 能够与系统设备进行建立通信连接。

- 能够实时监控系统设备获取的液位、电机状态等参数。

- 能够获取系统设备当前液位、系统时间、高低液位警戒线等参数。

- 能够设置系统设备液位、系统时间、高低液位警戒线等参数。

- 能够读取系统设备记录的数据。

- 能够对已经获取的数据进行显示、保存、数据处理(包括数值分析及绘图)。

4.2.2 上位机软件的界面设计

直观、人性的界面设计能够为软件使用者带来很多的方便,同时也能够为其留下深刻的印象。界面的设计与软件的功能息息相关,具有良好的层次结构,使软件使用者更容易上手。 在满足上文上位机软件的要求下,设计了一个主窗口,四页标签子窗口的设计。主窗口与各个标签页的子窗口的相关功能见表4-5:

表4-5 界面功能描述 | | | | | | | | | | | 启动实时监控,初始时不可用,待串口打开成功且联机成功后变为可用状态。 | | | | | 在串口号选择后,使用此按钮串口硬件建立连接;在串口打开时,该按钮显示为 关闭串口,用来断开串口的连接。 | | 该按钮初始时不可用,在打开串口后为可用状态,用来与系统设备进行连接,并显示联机状态。 | | | 该按钮初始时不可用,在打开串口且联机成功后变为可用。用来读取系统设备时间并显示。 | | 该按钮初始时不可用,在打开串口且联机成功后为可用状态。用来向系统设备写入PC机当前时间。 | | 该按钮初始时不可用,在打开串口且联机成功后为可用。用来向系统写入日期时间系列组合框选定时间。 | | 选定时间日期,用以设定指定时间按钮时间的写入。设定范围为2000年1月1日0时0分至2099年12月31日23时59分之间。 | | | 该按钮初始时不可用,在打开串口且联机成功后为可用状态。读取系统设备当前液位及显示。 | | 该按钮初始时不可用,在打开串口且联机成功后为可用状态。读取系统设备当前高低液位警戒线及显示。 | | 该按钮初始时不可用,在打开串口且联机成功后为可用状态。设置系统设备高低液位警戒线,设置数据由上下液位滑块提供。 | | 确定上液位参数,设置范围:大于当前下液位滑块参数值,小于5米。 | | 确定下液位参数,设置范围:小于当前上液位滑块参数,大于0米。 | | | 该按钮初始时不可用,在打开串口且联机成功后为可用状态。读取系统设备记录数据。完成后显示接收记录数据项目数。 | | 保存接收数据为文本文件,默认文件名为Rec**.txt。(**为数字,可自行增加) | | 变更文件保存路径,默认路径为C:\COMDATA\ | | | | | | |

界面设计效果如图4-5所示。 图4-5 上位机软件界面效果图

4.2.3 上位机串口通信功能的实现

在VC++中,最基本的串口操作是使用Windows API(Application Programming Interface)完成的。Windows 这个多作业系统除了协调应用程序的执行、分配内存、管理资源之外,它同时也是一个很大的服务中心,调用这个服务中心的各种服务(每一种服务就是一个函数),可以帮应用程式达到开启视窗、描绘图形、使用周边设备等目的,由于这些函数服务的对象是应用程序(Application),简称API。通过使用API函数控制实现串口通信要复杂一些,但是可以进行深层次的使用。 微软没有为串口操作提供相应直接的MFC(Microsoft Foundation Classes)类。然而微软提供了串口编程控件MSComm(Microsoft Communications Control)。MSComm是微软公司提供的简化Windows下串行通信编程的ActiveX控件,为应用程序提供了通过串行口收发数据的简便方法。MSComm控件在编程时比较方便,程序员不必去花时间了解较为复杂的API函数。它提供一系列标准通信命令的使用接口,利用它可以建立与串口的连接,并可以通过串口连接到其他通信设备,发送命令,交换数据以及监视和响应串行连接中发生的事件和错误。 在本设计中,便使用了MSComm控件进行串口编程。 下面就程序中使用的MSComm控件的主要属性作以说明。 功能:设置并返回端口号 说明:串口号设置返回范围从1到16。 功能:在MSComm控件设置CommEvent属性为ComEvRecevie并产生OnComm事件之前,设置并返回要接受的字符数。 说明:接收缓冲区接收到指定字符时差生OnComm事件。当指定字符设置为零,不产生OnComm事件。 功能:设置返回波特率、奇偶校验、数据位、停止位参数。 说明:设置时以字符串常量或字符串指针传递参数。格式为“BBB,P,D,S” BBBB为波特率,P为奇偶校验,D为数据位数,S为停止位数。 功能:从接受区内读取数据。 说明:返回数据类型为VARIANT型变量,该属性在串口没有打开时不能用,在运行时只读。 当InputMode属性为0时,变量中含有String型数据; 当InputMode属性为1时,变量中含有Byte型数据; 功能:想缓冲区写数据,发送缓冲区当前数据。 说明:写入缓冲区变量类型为VARIANT。发送二进制数据时,将Byte型数据放入VARIANT型变量中。 功能:打开或关闭串口,或者返回串口开、关状态 说明:传入参数为BOOL行,为TRUE时,打开串口;为FALSE时关闭串口。 串口的使用需要初始化,一般初始化需要以下几个步骤: - 选择串口号

- 选择输入方式

- 设置输入输出缓冲区大小

- 设置波特率、奇偶校验、数据位数、停止位数参数

- 打开串口

- 设置接收缓冲区接收多少数据响应OnComm事件

- 设置当前接受区长度

- 先预读缓冲区以清除残留数据

在串口初始化完成根据设置响应OnComm事件,在OnComm事件处理函数中对数据进行相应的处理。 在此次上位机软件中OnComm事件处理的思路是这样的:由于采用的是主从式通信方式,在某个功能按钮按下后,上位机使用SetOutPut函数发送指令,等待系统设备的响应,待接收到设备响应时,响应OnComm事件,根据返回的指令设置下一次响应OnComm事件的字符数或发送相应的数据。这样设计的优点是结合系统软件的设计,在没有奇偶校验等差错控制的情况下,尽量保证发送、接收数据的完整性。避免因系统在数据处理时的数据丢失。经实践证明,这样的办法是可行的。

4.2.4 上位机软件中的数据处理

由于MFC下的编程设计许多不同的类,不同类中的成员变量与成员函数参数的类型不尽相同,因此在实现某些参数传递的过程中不免需要参数类型的转换。这也是此次上位机软件设计的难点之一。 在软件的编写过程中设计了以下几个类或参数类型: CString类:CString是一种很有用的数据类型。它们很大程度上简化了MFC中的许多操作,使得MFC在做字符串操作的时候方便了很多。在软件中,CString主要用来可视化输出。 Byte类型:Byte是字节类型,由于通信过程中有大量的二进制数据传输,因此Byte类型是必不可少的。 VARIANT类型:使用MSComm控件,在发送和接收数据时,都要用到VARIANT数据类型,VARIANT实际上是一种共用体,它由各种类型的的数据成员构成。 Byte转CString:CString中保存的是字符的ASKII码,如果直接将Byte强制转换为CString是不行的,因为Byte保存的是二进制数据。强制转换的结果在显示时将出现乱码。因此需要自行构造转换函数。由于设备系统软件中处理传输的数据为压缩BCD码,因此,采用移位+48地方法将Byte转换为CString。 Byte转VARIANT:Byte不能直接转换为VARIANT以字符串形式发送数据。这里引入CbyteArray类与COleVariant类间接进行转换,首先使用CbyteArry的成员函数Add()将Byte依次连接成CbyteArray字符串,使用ColeVariant类将CbyteArray强制转换为VARIANT,进行串行发送。 VARIANT转Byte:同样,二者之间不能直接转换,需要引入COleSafeArray类间接进行转换。现将VARIANT强制转换为COleSafeArray,再使用COleSafeArray的GetElement成员函数将数据转换为Byte类型。这种转换在接收数据时出现。 解决了类型的转换问题,在发送、接收、数据显示、数据运算等方面便可根据需要使用相应的数据类型了。

结论与展望

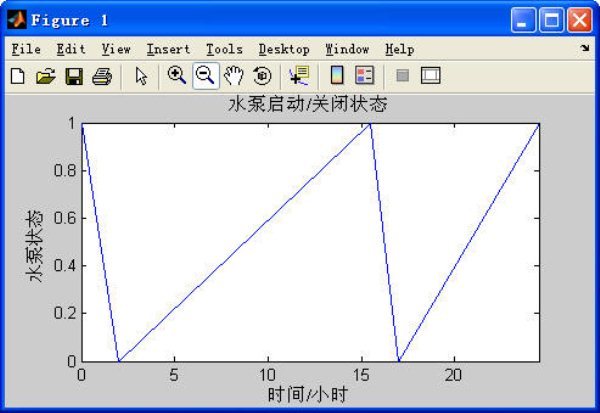

此次历时一学期的设计研究工作,我受益匪浅。查阅了大量的中英文资料,做了许多验证性试验,为最终设计的完成打下了坚实的基础。设计研究的过程也是一个学习的过程,其中使用的许多知识、技术是大学中未涉及的,这就需要在短时间内将这些知识、技术学以致用。在这里,我将此次设计中值得注意的地方加以总结。 以单片机为基础的应用系统的开发是一个有序的过程,同时也是一个经验积累的过程。一个有丰富开发经验的开发人员在硬件方案讨论,电路设计,软件设计及调试的过程中能够合理有效的开展各个阶段的工作,减少错误的发生,缩短研发周期。因此,多看、多做能够积累工程人员的经验,提高技能,在产品研发的过程中能够有所突破,有所创新。 电子技术应用广,设计领域多。在熟悉本职的技术工作外,开发设计人员还需对其他各个行业有所了解,这样才能使产品的功能更贴近实际,更合理,更行之有效。 技术的革新日新月异,为了保证开发产品成本更低、性能更强,开发更容易,周期更短,电子电路设计开发人员需要不断地学习掌握新技术,与时俱进。 液位测量监控系统的设计的基本功能的实现,说明设计思路的可行性。然而,在本次设计中仍有许多不足。 由于时间和精力有限,在上位机软件设计上,未对数据处理模块进行进一步的实现与讨论。由于专业知识有限,在此仅提出自己一些浅薄的看法。 先假设已有5项接收的数据,如:  设水箱上下液位间容积为V,水泵单位时间供水量恒定为m。设5项数据相邻两项间间隔时间为  ,  ,  ,  ,第一项至第五项总时间为T。m,V为已知量,t1~t4以及T可通过获得的数据计算得到。设某段时间内平均耗水量为  ,  水泵启动期间时平均耗水量为  ,  水泵停止期间平均耗水量为  。 通过记录的数据,经过计算,便可获得单位时间内平均耗水量。大量的数据,结合相应的理论算法,重中可以提取出有价值的分析与推测。 与此同时,根据以上举例数据使用Matlab绘制图形(这个工作使用VC++编程绘制亦可以完整)如图5-1:

图5-1 Matlab绘制图形 通过图形,我们可以观察直线的斜率,直观的观察出某一时间段耗水的快慢程度。 当然,这仅仅是一个十分简单的举例,计算、绘图方法不一定科学有效,仅起启发思维的作用。 在复杂的计算分析中,仅在水泵状态变化时记录数据往往是不够的,一项数据的内容也不够丰富。我们可在系统程序中,多增加若干个数据记录点记录数据。同时可增加实时高低液位间容积数据等内容,完善数据结构。 尽管系统设计在始终工作地情况下,没有考虑现实中万一掉电的数据保护问题,解决这个方法可以扩展大容量FLASH存储器,即使掉电,已经保存的数据也不会丢失。 本设计中没有加入系统冗余设计,结合实际情况,可增加看门狗电路,或使用单片机内部看门狗,防止程序跑飞。 人多水少,水资源时空分布不均,水土资源与经济社会发展布局不相匹配,是我国的基本水情。宏观上讲,通过对液位变化的分析,统计某一地区用水量,对水资源的统筹调配是有意义的。微观上说,根据统计出数据计算某一水箱在一定得统计规律中最佳的高低警戒线位置,从而减少水泵启动次数,降低能源消耗,延长水泵受用寿命。 在“十二五”期间,水利政策正在进一步完善,水利基础建设正在逐步走向现代化。在我党科学发展观的指导下,新型、环保、具有可持续发展设计思想的设备仪器正逐步被人们重视。

致 谢

本文档是在高文根老师的悉心指导下完成的。导师渊博的专业知识,严谨的治学态度,精益求精的工作作风,诲人不倦的高尚师德,严以律己、宽以待人的崇高风范,朴实无华、平易近人的人格魅力对我影响深远。本文档从选题到完成,每一步都是在导师的指导下完成的,倾注了导师大量的心血。在此,谨向导师表示崇高的敬意和衷心的感谢!本文档的顺利完成,离不开各位老师、同学和朋友的关心和帮助。在此表示深深的感谢!

作者: 2011 年 06 月 15 日

参考文献

[1]张毅刚,彭喜元,董继成.单片机原理及应用[M].北京:高等教育出版社,2003. [2]李书旗,沈金荣.液位测量传感器系统的设计与实现[J].计算机测量与控制,2009,17(11):2131-2133. [3]郑伟建,夏扬,夏晴.自抗扰控制器在液位控制中的研究[J].计算机仿真,2009,26(10):190-193. [4]钟晓强.基于单片机实现的液位控制器设计[J].现代电子技术,2009,32(2):51-53. [5]蔡黎.一种基于单片机的水位控制系统设计[J].仪器仪表用户,2007,14(4):44-45. [6]陈霞,白小军.基于单片机的液位监控系统[J].武汉理工大学学报,2007,29(3):3-5. [7]陈新昌,王万章,李祥付.单片机在水位控制中的应用[J].中国科技信息,2006,(24):89-90,94. [8]苏晓龙,王香婷.基于RS-485总线的数据采集系统[J].仪表技术与传感器,2007,(12). [9]张宝伟.基于Lab VIEW的液位监控系统[D].哈尔滨:哈尔滨工业大学,2007. [10]张凤兰.液位测量与监控系统设计[D].北京:北方工业大学,2010. [11]任开春,涂亚庆.20余种液位测量方法分析[J].工业仪表与自动化装置,2003,(5):12-16. [12]柳军,等.基于AVR单片机的液面测量监控系统的设计[J].中国医疗设备,2009,24(12):27-30. [13]丁希顺.单片微型计算机液位测量系统设计[J].安阳师范学院学报,2005(2):71-73. [14]老虎工作室编著.电路设计与制版:Protel 99SE入门与提高[M].北京:人民邮电出版社,2007. [15]彭军.传感器与检测技术[M].西安:西安电子科技大学出版社,2003. [16]余永权.单片机在控制系统中应用[M].北京:电子工业出版社,2003. [17]刘鲲,孙春亮.单片机C语言入门[M].北京:人民邮电出版社,2008. [18]姚振东,朱勇.电容传感器在液位测量中的应用[J].传感器世界,2000,(9):4-7. [19] Maurice Wilkes. Progress in Computers [J]. IEEE Trans on PE, Feb 2004,Vol.3(NO.6):470-472. [20] Jae Hyeong Seo, Cang Ho Choi. A new simplified Space-Vector PWM Method for Three-level-Inverters [J].IEEE Trans on PE, July 2001,Vol.16(NO.4):545-550.

附 录A系统电路原理图

附 录 B外文文献及译文

Progress in Computers Prestige Lecture delivered to IEE, Cambridge, on 5 February 2004 Maurice Wilkes Computer Laboratory University of Cambridge The first stored program computers began to work around 1950. The one we built in Cambridge, the EDSAC was first used in the summer of 1949. These early experimental computers were built by people like myself with varying backgrounds. We all had extensive experience in electronic engineering and were confident that that experience would stand us in good stead. This proved true, although we had some new things to learn. The most important of these was that transients must be treated correctly; what would cause a harmless flash on the screen of a television set could lead to a serious error in a computer. As far as computing circuits were concerned, we found ourselves with an embarass de richess. For example, we could use vacuum tube diodes for gates as we did in the EDSAC or pentodes with control signals on both grids, a system widely used elsewhere. This sort of choice persisted and the term families of logic came into use. Those who have worked in the computer field will remember TTL, ECL and CMOS. Of these, CMOS has now become dominant. In those early years, the IEE was still dominated by power engineering and we had to fight a number of major battles in order to get radio engineering along with the rapidly developing subject of electronics.dubbed in the IEE light current electrical engineering.properly recognised as an activity in its own right. I remember that we had some difficulty in organising a conference because the power engineers’ ways of doing things were not our ways. A minor source of irritation was that all IEE published papers were expected to start with a lengthy statement of earlier practice, something difficult to do when there was no earlier practice Consolidation in the 1960s By the late 50s or early 1960s, the heroic pioneering stage was over and the computer field was starting up in real earnest. The number of computers in the world had increased and they were much more reliable than the very early ones . To those years we can ascribe the first steps in high level languages and the first operating systems. Experimental time-sharing was beginning, and ultimately computer graphics was to come along. Above all, transistors began to replace vacuum tubes. This change presented a formidable challenge to the engineers of the day. They had to forget what they knew about circuits and start again. It can only be said that they measured up superbly well to the challenge and that the change could not have gone more smoothly. Soon it was found possible to put more than one transistor on the same bit of silicon, and this was the beginning of integrated circuits. As time went on, a sufficient level of integration was reached for one chip to accommodate enough transistors for a small number of gates or flip flops. This led to a range of chips known as the 7400 series. The gates and flip flops were independent of one another and each had its own pins. They could be connected by off-chip wiring to make a computer or anything else. These chips made a new kind of computer possible. It was called a minicomputer. It was something less that a mainframe, but still very powerful, and much more affordable. Instead of having one expensive mainframe for the whole organisation, a business or a university was able to have a minicomputer for each major department. Before long minicomputers began to spread and become more powerful. The world was hungry for computing power and it had been very frustrating for industry not to be able to supply it on the scale required and at a reasonable cost. Minicomputers transformed the situation. The single-chip computer At each shrinkage the number of chips was reduced and there were fewer wires going from one chip to another. This led to an additional increment in overall speed, since the transmission of signals from one chip to another takes a long time. Eventually, shrinkage proceeded to the point at which the whole processor except for the caches could be put on one chip. This enabled a workstation to be built that out-performed the fastest minicomputer of the day, and the result was to kill the minicomputer stone dead. As we all know, this had severe consequences for the computer industry and for the people working in it. From the above time the high density CMOS silicon chip was Cock of the Roost. Shrinkage went on until millions of transistors could be put on a single chip and the speed went up in proportion. Processor designers began to experiment with new architectural features designed to give extra speed. One very successful experiment concerned methods for predicting the way program branches would go. It was a surprise to me how successful this was. It led to a significant speeding up of program execution and other forms of prediction followed Equally surprising is what it has been found possible to put on a single chip computer by way of advanced features. For example, features that had been developed for the IBM Model 91.the giant computer at the top of the System 360 range.are now to be found on microcomputers Murphy’s Law remained in a state of suspension. No longer did it make sense to build experimental computers out of chips with a small scale of integration, such as that provided by the 7400 series. People who wanted to do hardware research at the circuit level had no option but to design chips and seek for ways to get them made. For a time, this was possible, if not easy Unfortunately, there has since been a dramatic increase in the cost of making chips, mainly because of the increased cost of making masks for lithography, a photographic process used in the manufacture of chips. It has, in consequence, again become very difficult to finance the making of research chips, and this is a currently cause for some concern. The Semiconductor Road Map The extensive research and development work underlying the above advances has been made possible by a remarkable cooperative effort on the part of the international semiconductor industry. At one time US monopoly laws would probably have made it illegal for US companies to participate in such an effort. However about 1980 significant and far reaching changes took place in the laws. The concept of pre-competitive research was introduced. Companies can now collaborate at the pre-competitive stage and later go on to develop products of their own in the regular competitive manner. The agent by which the pre-competitive research in the semi-conductor industry is managed is known as the Semiconductor Industry Association (SIA). This has been active as a US organisation since 1992 and it became international in 1998. Membership is open to any organisation that can contribute to the research effort. Every two years SIA produces a new version of a document known as the International Technological Roadmap for Semiconductors (ITRS), with an update in the intermediate years. The first volume bearing the title ‘Roadmap’ was issued in 1994 but two reports, written in 1992 and distributed in 1993, are regarded as the true beginning of the series. Successive roadmaps aim at providing the best available industrial consensus on the way that the industry should move forward. They set out in great detail.over a 15 year horizon. the targets that must be achieved if the number of components on a chip is to be doubled every eighteen months.that is, if Moore’s law is to be maintained.-and if the cost per chip is to fall. In the case of some items, the way ahead is clear. In others, manufacturing problems are foreseen and solutions to them are known, although not yet fully worked out; these areas are coloured yellow in the tables. Areas for which problems are foreseen, but for which no manufacturable solutions are known, are coloured red. Red areas are referred to as Red Brick Walls. The targets set out in the Roadmaps have proved realistic as well as challenging, and the progress of the industry as a whole has followed the Roadmaps closely. This is a remarkable achievement and it may be said that the merits of cooperation and competition have been combined in an admirable manner. It is to be noted that the major strategic decisions affecting the progress of the industry have been taken at the pre-competitive level in relative openness, rather than behind closed doors. These include the progression to larger wafers. By 1995, I had begun to wonder exactly what would happen when the inevitable point was reached at which it became impossible to make transistors any smaller. My enquiries led me to visit ARPA headquarters in Washington DC, where I was given a copy of the recently produced Roadmap for 1994. This made it plain that serious problems would arise when a feature size of 100 nm was reached, an event projected to happen in 2007, with 70 nm following in 2010. The year for which the coming of 100 nm (or rather 90 nm) was projected was in later Roadmaps moved forward to 2004 and in the event the industry got there a little sooner. I presented the above information from the 1994 Roadmap, along with such other information that I could obtain, in a lecture to the IEE in London, entitled The CMOS end-point and related topics in Computing and delivered on 8 February 1996. The idea that I then had was that the end would be a direct consequence of the number of electrons available to represent a one being reduced from thousands to a few hundred. At this point statistical fluctuations would become troublesome, and thereafter the circuits would either fail to work, or if they did work would not be any faster. In fact the physical limitations that are now beginning to make themselves felt do not arise through shortage of electrons, but because the insulating layers on the chip have become so thin that leakage due to quantum mechanical tunnelling has become troublesome. There are many problems facing the chip manufacturer other than those that arise from fundamental physics, especially problems with lithography. In an update to the 2001 Roadmap published in 2002, it was stated that the continuation of progress at present rate will be at risk as we approach 2005 when the roadmap projects that progress will stall without research break-throughs in most technical areas “. This was the most specific statement about the Red Brick Wall, that had so far come from the SIA and it was a strong one. The 2003 Roadmap reinforces this statement by showing many areas marked red, indicating the existence of problems for which no manufacturable solutions are known. It is satisfactory to report that, so far, timely solutions have been found to all the problems encountered. The Roadmap is a remarkable document and, for all its frankness about the problems looming above, it radiates immense confidence. Prevailing opinion reflects that confidence and there is a general expectation that, by one means or another, shrinkage will continue, perhaps down to 45 nm or even less. However, costs will rise steeply and at an increasing rate. It is cost that will ultimately be seen as the reason for calling a halt. The exact point at which an industrial consensus is reached that the escalating costs can no longer be met will depend on the general economic climate as well as on the financial strength of the semiconductor industry itself.。 Insulating layers in the most advanced chips are now approaching a thickness equal to that of 5 atoms. Beyond finding better insulating materials, and that cannot take us very far, there is nothing we can do about this. We may also expect to face problems with on-chip wiring as wire cross sections get smaller. These will concern heat dissipation and atom migration. The above problems are very fundamental. If we cannot make wires and insulators, we cannot make a computer, whatever improvements there may be in the CMOS process or improvements in semiconductor materials. It is no good hoping that some new process or material might restart the merry-go-round of the density of transistors doubling every eighteen months. I said above that there is a general expectation that shrinkage would continue by one means or another to 45 nm or even less. What I had in mind was that at some point further scaling of CMOS as we know it will become impracticable, and the industry will need to look beyond it. Since 2001 the Roadmap has had a section entitled emerging research devices on non-conventional forms of CMOS and the like. Vigorous and opportunist exploitation of these possibilities will undoubtedly take us a useful way further along the road, but the Roadmap rightly distinguishes such progress from the traditional scaling of conventional CMOS that we have been used to. Advances in Memory Technology Unconventional CMOS could revolutionalize memory technology. Up to now, we have relied on DRAMs for main memory. Unfortunately, these are only increasing in speed marginally as shrinkage continues, whereas processor chips and their associated cache memory continue to double in speed every two years. The result is a growing gap in speed between the processor and the main memory. This is the memory gap and is a current source of anxiety. A breakthrough in memory technology, possibly using some form of unconventional CMOS, could lead to a major advance in overall performance on problems with large memory requirements, that is, problems which fail to fit into the cache. Perhaps this, rather than attaining marginally higher basis processor speed will be the ultimate role for non-conventional CMOS. Shortage of Electrons Although shortage of electrons has not so far appeared as an obvious limitation, in the long term it may become so. Perhaps this is where the exploitation of non-conventional CMOS will lead us. However, some interesting work has been done.notably by Haroon Amed and his team working in the Cavendish Laboratory.on the direct development of structures in which a single electron more or less makes the difference between a zero and a one. However very little progress has been made towards practical devices that could lead to the construction of a computer. Even with exceptionally good luck, many tens of years must inevitably elapse before a working computer based on single electron effects can be contemplated.

微机发展简史 IEEE的文档 剑桥大学,2004/2/5 莫里斯 威尔克斯 计算机实验室 剑桥大学

第一台存储程序的计算开始出现于1950前后,它就是1949年夏天在剑桥大学,我们创造的延迟存储自动电子计算机(EDSAC)。 最初实验用的计算机是由象我一样有着广博知识的人构造的。我们在电子工程方面都有着丰富的经验,并且我们深信这些经验对我们大有裨益。后来,被证明是正确的,尽管我们也要学习很多新东西。最重要的是瞬态一定要小心应付,虽然它只会在电视机的荧幕上一起一个无害的闪光,但是在计算机上这将导致一系列的错误。 在电路的设计过程中,我们经常陷入两难的境地。举例来说,我可以使用真空二级管做为门电路,就象在EDSAC中一样,或者在两个栅格之间用带控制信号的五级管,这被广泛用于其他系统设计,这类的选择一直在持续着直到逻辑门电路开始应用。在计算机领域工作的人都应该记得TTL,ECL和CMOS,到目前为止,CMOS已经占据了主导地位。 在最初的几年,IEE(电子工程师协会)仍然由动力工程占据主导地位。为了让IEE 认识到无线工程和快速发展的电子工程并行发展是它自己的一项权利,我们不得不面对一些障碍。由于动力工程师们做事的方式与我们不同,我们也遇到了许多困难。让人有些愤怒的是,所有的IEE出版的文档都被期望以冗长的早期研究的陈述开头,无非是些在早期阶段由于没有太多经验而遇到的困难之类的陈述。 60年代的巩固阶段 60年代初,个人英雄时代结束了,计算机真正引起了重视。世界上的计算机数量已经增加了许多,并且性能比以前更加可靠。这些我认为归因与高级语言的起步和第一个操作系统的诞生。分时系统开始起步,并且计算机图形学随之而来。 综上所述,晶体管开始代替正空管。这个变化对当时的工程师们是个不可回避的挑战。他们必须忘记他们熟悉的电路重新开始。只能说他们鼓起勇气接受了挑战,尽管这个转变并不会一帆风顺。 小规模集成电路和小型机 很快,在一个硅片上可以放不止一个晶体管,由此集成电路诞生了。随着时间的推移,一个片子能够容纳的最大数量的晶体管或稍微少些的逻辑门和翻转门集成度达到了一个最大限度。由此出现了我们所知道7400系列微机。每个门电路或翻转电路是相互独立的并且有自己的引脚。他们可通过导线连接在一起,作成一个计算机或其他的东西。 这些芯片为制造一种新的计算机提供了可能。它被称为小型机。他比大型机稍逊,但功能强大,并且更能让人负担的起。一个商业部门或大学有能力拥有一台小型机而不是得到一台大型组织所需昂贵的大型机。 随着微机的开始流行并且功能的完善,世界急切获得它的计算能力但总是由于工业上不能规模供应和它可观的价格而受到挫折。微机的出现解决了这个局面。 单片机 芯片每次的缩小,芯片数量将减少;并且芯片间的导线也随之减少。这导致了整体速度的下降,因为信号在各个芯片间的传输时间变长了。 渐渐地,芯片的收缩到只剩下处理器部分,缓存都被放在了一个单独的片子上。这使得工作站被建成拥有当代小型机一样的性能,结果搬倒了小型机绝对的基石。正如我们所知道的,这对于计算机工业和从事计算机事业的人产生了深远的影响 自从上述时代的开始,高密度CMOS硅芯片成为主导。随着芯片的缩小技术的发展,数百万的晶体管可以放在一个单独的片子上,相应的速度也成比例的增加。 为了得到额外的速度。处理器设计者开始对新的体系构架进行实验。一次成功的实验都预言了一种新的编程方式的分支的诞生。我对此取得的成功感到非常惊奇。它导致了程序执行速度的增加并且其相应的框架。 同样令人惊奇的是,通过更高级的特性建立一种单片机是有可能的。例如,为IBM Model 91开发的新特性,现在在单片机上也出现了。 Murphy定律仍然在中止的状态。它不再适用于使用小规模集成芯片设计实验用的计算机,例如7400系列。想在电路级上做硬件研究的人们没有别的选择除了设计芯片并且找到实现它的办法。一段时间内,这样是可能的,但是并不容易。 不幸的是,制造芯片的花费有了戏剧性的增长,主要原因是制造芯片过程中电路印刷版制作成本的增加。因此,为制作芯片技术追加资金变的十分困难,这是当前引起人们关注的原因。 半导体前景规划 对于以上提到的各个方面,在部分国际半导体工业部门的精诚合作下,广泛的研究与开发工作是可行的。 在以前美国反垄断法禁止这种行为。但是在1980年,该法律发生了很大变化。预竞争概念被引进了该法律。各个公司现在可以在预言竞争阶段展开合作,然后在规则允许的情况下继续开发各自的产品。 在半导体工业中,预竞争研究的管理机构是半导体工业协会。1972年作为美国国内的组织,1998年成为一个世界性的组织。任何一个研究组织都可加入该协会。 每两年,SIA修订一次ITRS(国际半导体科学规划),并且逐年更新。1994年在第一卷中引入了“前景规划”一词,该卷由两个文档组成,先于1992年,在1993年提交。它被认为是该规划的真正开始。 为了推动半导体工业的向前发展,后续的规划提供最好的可利用的工业标准。它们对于15年内的发展做出了详细的规划。要达到的目标是每18个月晶体管的集成度增加一倍,同时每块芯片的价格下降一半,即Moore定律。 对于某些方面,前面的道路是清楚的。在另一方面,制造业的问题是可以预见的并且解决的办法也是可以知道的,尽管不是所有的问题都能够解决。这样的领域在表格中由蓝色表示,同时没有解决办法的,加以红色。红色区域往往称为红色砖墙。 规划建立的目标是现实的,同时也是充满挑战的。半导体工业整体上的进步于该规划密不可分。这是个令人惊讶的成就,它可以说是合作和竞争共同的价值。 值得注意的是,促进半导体工业向前发展的主要的战略决策是相对开放的预竞争机制,而不是闭关锁国。这也包括大规模圆晶片取得进展的原因。 1995年前,我开始感觉到,如果达到了不可能使得晶体管体积更小的临界点时,将发生什么。怀着这样的疑惑,我访问了位于华盛顿的ARPA(美国国防部)指挥总部,在那,我看到1994年规划的复本。我恍然大悟,当圆晶片尺寸在2007年达到100纳米时,将出现严重的问题,在2010年达到70纳米时也如此。在随后的2004年的规划中,当圆晶片尺寸达到100纳米时,也做了相应的规划。不久半导体工业将发展到那一步。 从1994年的规划中我引用了以上的信息,还有就是一篇提交到IEE的项目为CMOS终结点的文档和在1996年2月8号的Computing上讨论的一些项目。 我现在的想法是,最终的结果是表示一个存在可用的电子数目从数千减少到数百。在这样的情况下,统计波动将成为问题。最后,电路或者不再工作,或者达到了速度的极限。事实上,物理限制将开始让他们感觉到不能突破电子最终的不足,原因是芯片上绝缘层越来越薄,以致量子理论中隧道效应引起了麻烦,导致了渗漏。 相对基础物理学,芯片制造者面对的问题要多出许多,尤其是电路印刷术遇到的困难。2001年更新2002年出版的规划中,陈述了这样一种情况,照目前的发展速度,如果在2005年前在关键技术领域没有取得大的突破的话,半导体业将停止不前。这是对“红色砖墙”最准确的描述。到目前为止是SIA遇到的最麻烦的问题。2003年的规划书强调了这一点,通过在许多地方加上了红色,指示在这些领域仍存在人们没有解决的制造方法问题。 到目前为止,可以很满意的报道,所遇到的问题到及时找到了解决之道。规划书是个非凡的文档,并且它坦白了以上提到的问题,并表示出了无限的信心。主要的见解反映出了这种信心并且有一个大致的期望,通过某种方式,圆晶体将变的更小,也许到45纳米或更小。 然而,花费将以很大的速率增长。也许将成为半导体停滞不前的最终原因。对于逐步增加的花费直到不能满足,这个精确的工业上达到一致意见的平衡点,依赖于经济的整体形势和半导体工业自身的财政状况。 最高级芯片的绝缘层厚度仅有5个原子的大小。除了找到更好的绝缘材料外,我们将寸步难行。对于此,我们没有任何办法。我们也不得不面对芯片的布线问题,线越来越细小了。还有散热问题和原子迁移问题。这些问题是相当基础性的。如果我们不能制作导线和绝缘层,我们就不能制造一台计算机。不论在CMOS加工工艺上和半导体材料上取得多么大的进步。更别指望有什么新的工艺或材料可以使得半导体集成度每18个月翻一番的美好时光了。 我在上文中说到,圆晶体继续缩小直到45纳米或更小是个大致的期望。在我的头脑中,从某点上来说,我们所知道的继续缩小CMOS是不可行的,但工业上需要超越它。 2001年以来,规划书中有一部分陈述了非传统形式CMOS的新兴研究设备。一些精力旺盛的人和一些投机者的探索无疑给了我们一些有益的途径,并且规划书明确分辨出了这些进步,在那些我们曾经使用的传统CMOS方面。 内存技术的进步 非传统的CMOS变革了存储器技术。直到现在,我们仍然依靠DRAM作为主要的存储体。不幸的是,随着芯片的缩小,只有芯片外围速度上的增长——处理器芯片和它相关的缓存速度每两年增加一倍。这就是存储器代沟并且是人们焦虑的根源。存储技术的一个可能突破是,使用一种非传统的CMOS管,在计算机整体性能上将导致一个很大的进步,将解决大存储器的需求,即缓存不能解决的问题。 也许这个,而不是外围电路达到基本处理器的速度将成为非传统CMOS.的最终角色。 电子的不足 尽管目前为止,电子每表现出明显的不足,然而从长远看来,它最终会不能满足要求。也许这是我们开发非传统CMOS管的原因。在Cavendish实验室里,Haroon Amed已经作了很多有意义的工作,他们想通过一个单独电子或多或少的表现出0和1的区别。然而对于构造实用的计算机设备只取得了一点点进展。也许由于偶然的好运气,数十年后一台基于一个单独电子的计算机也许是可以实现的。

以上图文的Word格式文档下载(内容和本网页上的一模一样,方便大家保存):

基于单片机的液位控制系统设计-精品.doc

(1.02 MB, 下载次数: 56)

基于单片机的液位控制系统设计-精品.doc

(1.02 MB, 下载次数: 56)

|