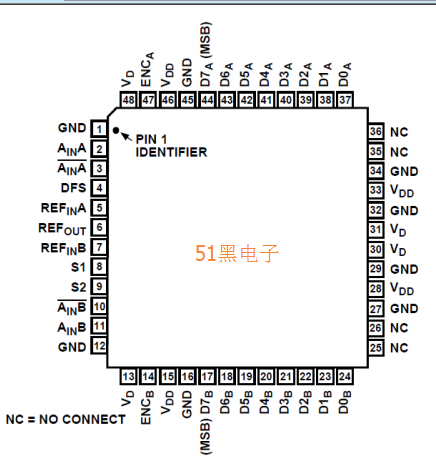

NTD8288引脚图:

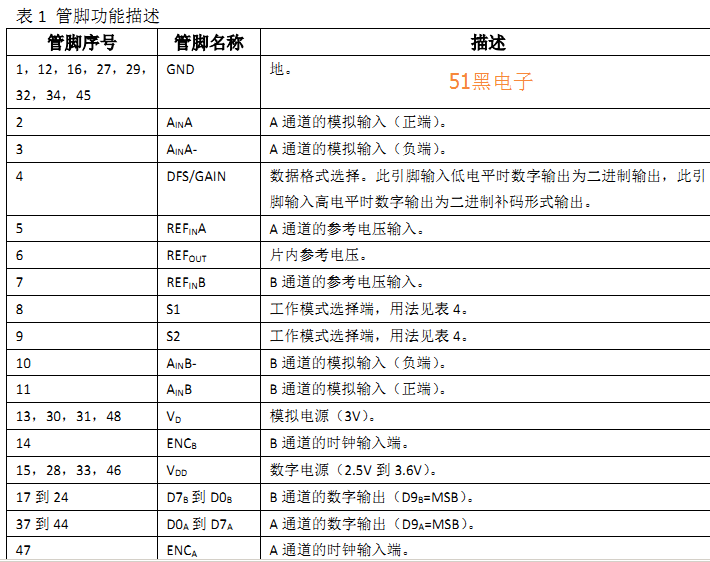

NTD8288管脚功能描述:

产品描述

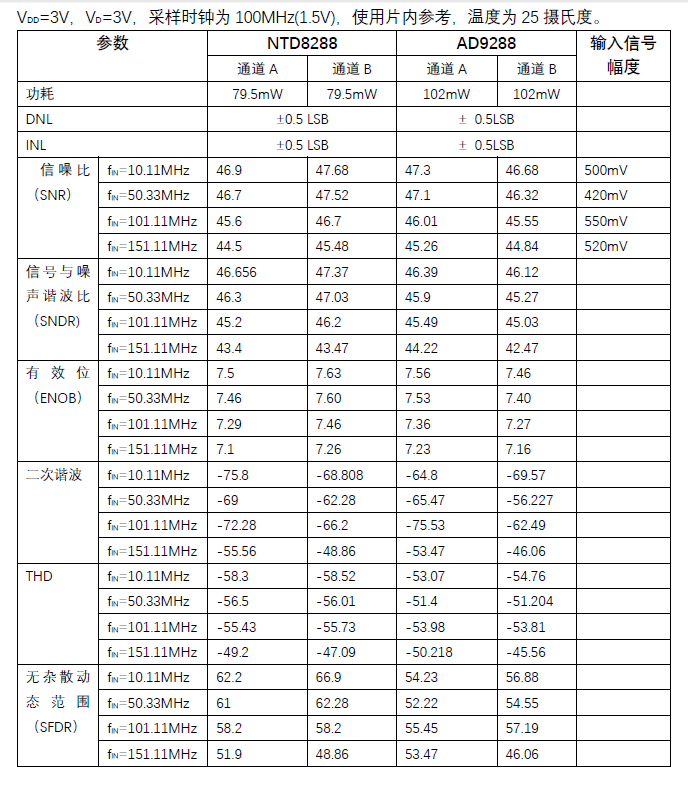

NTD8288是一款双核8位单芯片采样模数转换器(ADC),内置片内采样保持电路,具有低成本、低功耗、小尺寸和易于使用等特性。它采用100 MSPS转换速率工作,在整个工作范围内都具有出色的动态性能。每个通道均可以独立工作。

该ADC 只需一个3.0 V(2.7 V 至3.6 V)单电源和一个时钟就能发挥全部效能。对于大多数应用来说,无需外部基准电压源或驱动器件。数字输出为TTL/CMOS兼容,单独的输出电源引脚支持3.3 V或2.5 V逻辑接口。

1. 低功耗:每通道功耗仅 70mW (100 MSPS);在保持高交流性能的同时,其它速度等级的功耗按比例降低。

2. 引脚兼容升级:8 位器件可轻松升级至10位器件,与8 位AD9288双核 ADC引脚兼容。

3. 易于使用:片内基准电压和用户控制选项使系统设计更灵活。

4. 高性能:在Nyquist输入频率时,信噪比保持在 47dB(100 MSPS)。

5. 采用先进的CMOS工艺制造,提供48 引脚薄型四方扁平封装(7 mm × 7 mm LQFP),额定温度范围为-200°C 至+125°C军用温度范围。

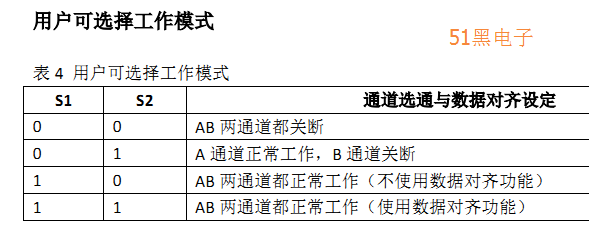

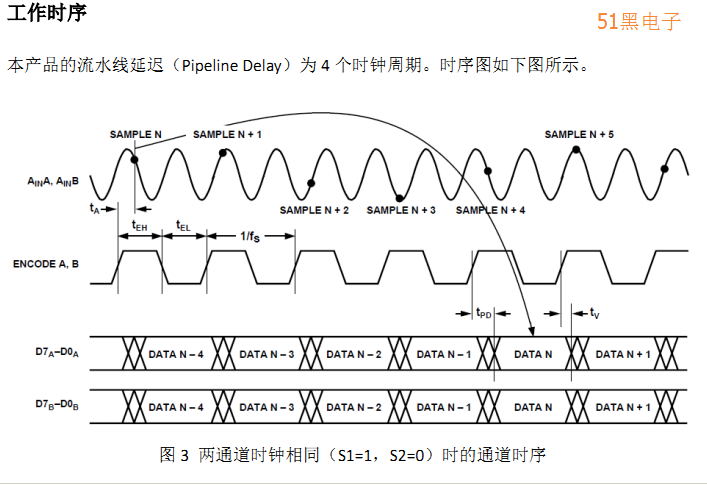

当S1设置为1,S2设置为0 时,AB两通道都正常工作,如果两通道输入相同的时钟,那么两通道的数字输出都在时钟上升沿,数据是对齐的。但是当两个通道的时钟不同的时候,那么两个通道的数字输出都在各自时钟的上升沿,此时数据是不对齐的。

当S1设置为1, S2设置为1 时, AB两通道都正常工作,如果两通道输入相同的时钟,此时,A 通道的数据输出仍在时钟的上升沿,而B通道的数字输出被延后了半个时钟周期,B通道的数字输出在B 通道时钟的下降沿,数据是不对齐的。但是当两个通道的时钟不同的时候,而且两个时钟相位相差180°时,B通道的数字输出被延后了半个时钟周期,那么两个通道的数字输出都在A通道时钟的上升沿,此时数据是对齐的。

电源

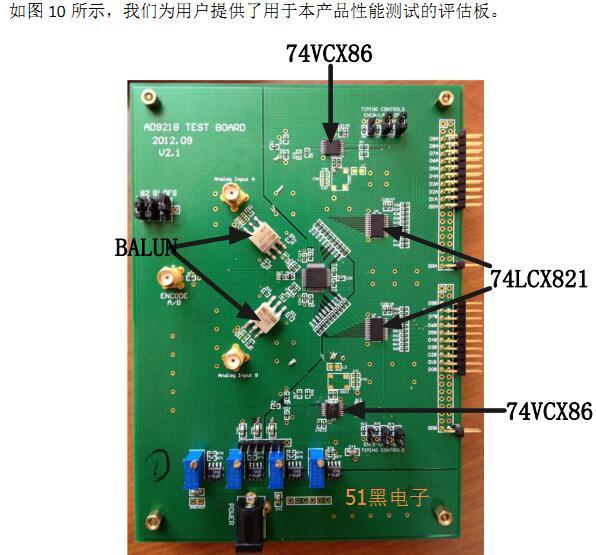

电路板下端的黑色插头“POWER”即为电源输入,输入 5V 直流电源。电源输入后用四路 LDO产生电路板所需的四路电源电压,四路电源电压都可以通过蓝色的可调电阻来调节电压大小。

四路电源从左到右依次为 VD、VDD、VDL、VDO。

VD为NTD8288的模拟电源输入,设定为3V。

VDD为 NTD8288的数字电源输入,设定为 3V。

VDL为数字芯片“74VCX86”和“74LCX86”的电源输入,设定为 3V。

VDO为晶振的电源输入,目前没有用到。

时钟

时钟输入通过SMA头“ENCODE A/B”输入,需要输入一个精准的正弦信号,正弦信号的频率即为时钟频率。正弦信号通过异或门芯片 74VCX86 后就成了方波时钟。每个 74VCX86 芯片有三路输出,一路给 ADC 时钟,一路给到后面的数字buffer芯片“74LCX821”作为buffer芯片的时钟,第三路给到插针“DRA”作为后续数字信号采集的时钟。

因为高速 ADC 对时钟抖动非常敏感,所以要求提供的时钟抖动很小,所以,要把输入正弦信号的振幅加大以便 ADC得到的时钟抖动很小。(请注意正弦信号的振幅不能过大,以防止异或门芯片 74VCX86 烧毁,一般正弦信号的振幅不能超过 3.2V,也就是正弦的峰峰值不能超过6.4伏。 )

模拟输入

ADC芯片的模拟输入通过 SMA头“Analog Input A”和“Analog Input B”输入,分别为两个通道的模拟输入。信号经过 SMA 头输入后经过 Balun 芯片(T1-1T-KK81)转换成差分信号,差分信号输入ADC的模拟输入端。 SMA头和Balun芯片之间通过一个0.1uF电容连接, Balun的两个输出端通过0.1uF的电容后接入ADC芯片。 Balun的两个输出端各接一个 25欧姆的电阻连接到GND。

请注意,模拟输入端需要接入一个高质量的正弦信号,而且要加滤波器。

数字输出

每路数字输出都经过一个 50 欧姆电阻接到数字 buffer 芯片 74LCX821(D 触发器),数字信号buffer芯片输出后经过一个50 欧姆电阻接到插针输出。

请注意,插针的信号排布,如上图所示,左边一竖列全部为 GND,右边一列如图中所示为数字输出和时钟输出信号。A 通道的数字输出和B通道输出的排布相同。

时序调整

对于两个通道,每个通道都设有时序控制“TIMING CONTROLS”三个跳线端口,分别控制三路时钟(ADC 时钟,数字 buffer 时钟,输出时钟)的相位。如前所述,三路时钟都是异或门产生,而TIMING CONTROLS 的三个跳线端就分别控制着三个异或门的一端。不连接跳线时,产生该路时钟的异或门一端接低电平,连接跳线器时接高电平。

所以每个跳线器都能改变响应的时钟的相位。当数据采集板无法正确的采集数据时,应该尝试改变一下这三路时序。

当测试出现了异常

(1)检查各路电源电压是否正确。

(2)检查S1、S2、DFS是否连接正确。

(3)尝试先把时钟调整到 20MHz,输入信号调整到 1MHz,看看功能是否正确。

(4)如果性能偏低,试着提高正弦时钟信号振幅,但是注意振幅不能过大而使得后面的74VCX86 异或门芯片被破坏。

(5)尝试通过调整TIMING CONTROLS 的跳线来调整时序。

整的pdf格式文档51黑下载地址:

NTD8288(兼容AD9288)n.pdf

(1.05 MB, 下载次数: 27)

NTD8288(兼容AD9288)n.pdf

(1.05 MB, 下载次数: 27)

|