|

1、 建库完成后进行导网表,将器件导入 PCB 中: Ⅰ、若为 pads 网表(logic)

1)、在 LAYOUT 里新建一个板,画好板框,在 LAYOUT 和 LOGIC 里将库文件路径指定好:

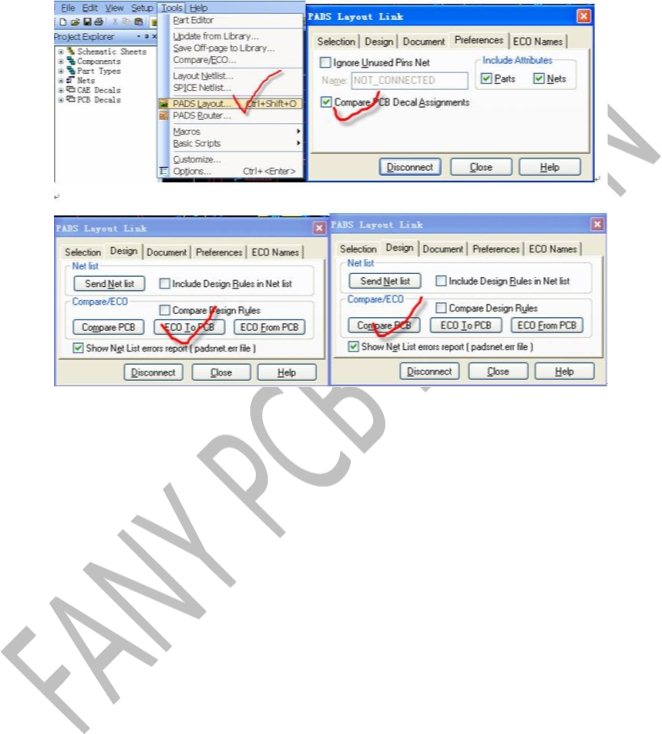

2)、在 LOGIC 里进行网络对比,将网络导入 PCB:

进行完这两项显示 NO DIFFERENT 则说明网表导入 PCB 成功,如若有错,则根据错误报告进行修改。

Ⅱ、如若是其它格式的原理图网表文件,先指定好库路径,再通过 IMPORT,将网表导入新建的 PCB 中:

2、其它非 LOGIC 原理图的导网表过程: Ⅰ、99SE 导出网表:

1)、首先,打开 protel 的原理图。

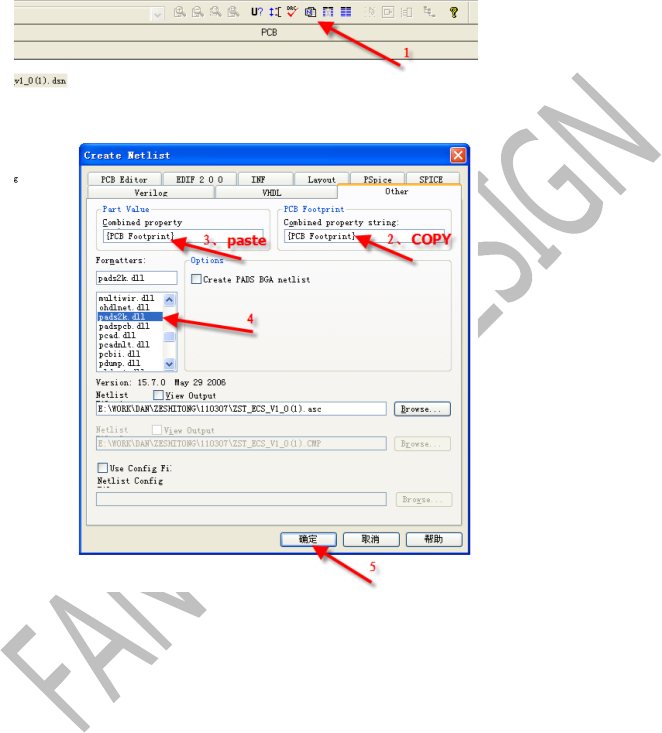

2)、然后,点击 Design->Creat Netlist,弹出如下的对话框,如下设置,点击 OK。

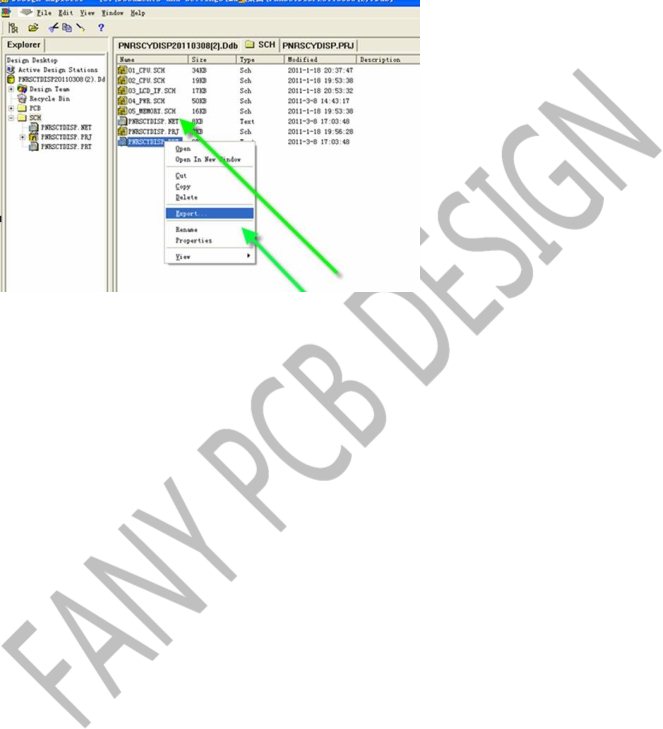

3)、然后会生成.NET 和.PRT 两个文件,关掉。到如下界面(sch). 4)、将.NET 和.PRT 两个文件导出,保存。

5)、将.PRT 文件的后缀改为.asc,保存。

6)、用记事本打开.NET 文件,删除第一行,然后全选,复制。

7)、用记事本打开.asc 文件,删除文件最后的*END* ,将.NET 文件中复制的拷到其后,保存,然后 将.asc 的文件的前两行删掉,改为:

!PADS-POWERPCB-V3.0-MILS! DESIGN DATABASE ASCII FILE 2.0

*PART* ITEMS

这样,PADS 的 .asc 文件就好了。 Ⅱ、CANDENCE 原理图导出 ASC:

1)、以 OTHER 方式导出

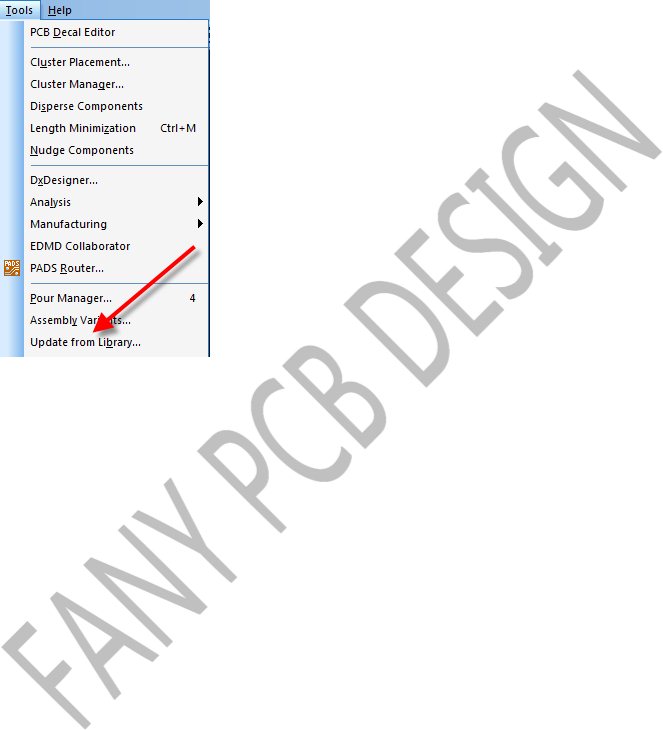

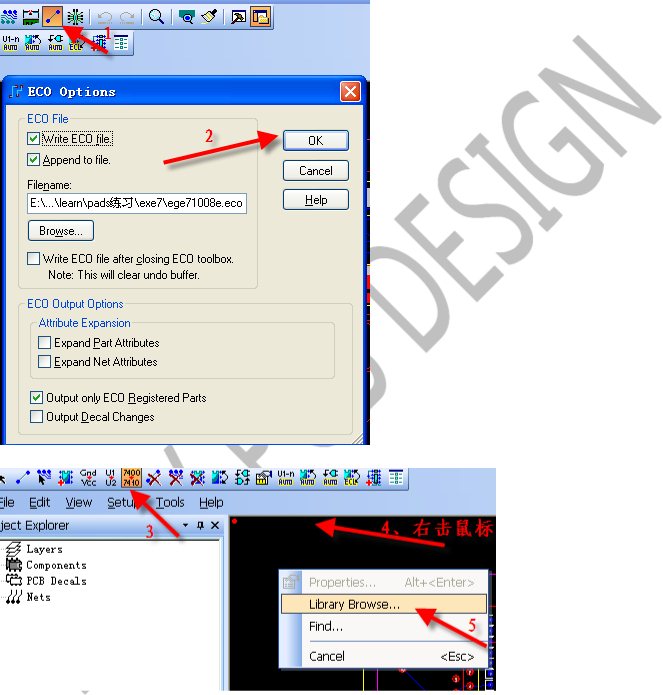

3、更新原理图 Ⅰ、对于 PADS9.3 软件,先指定好库路径,然后将板上的器件、网络、Reuse、Unions 全部解开,再执行 以下操作即可更新器件:

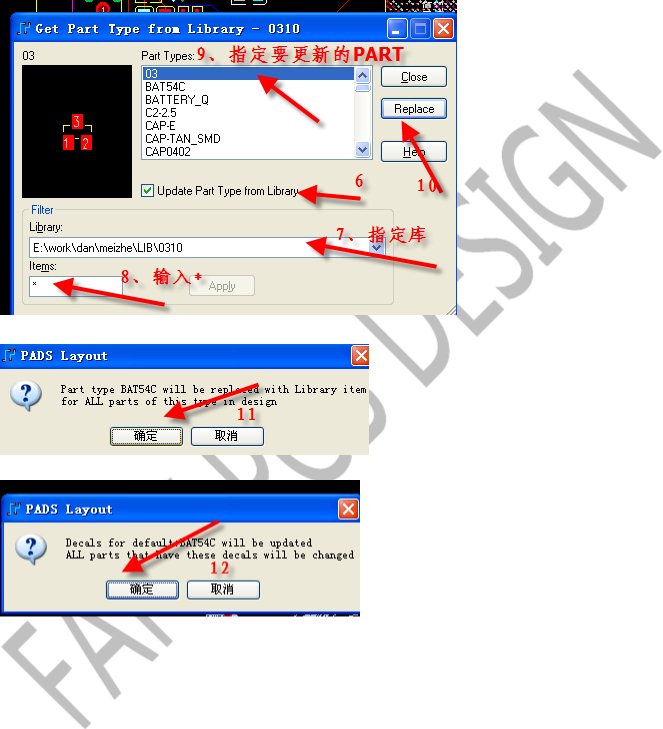

Ⅱ、在板上一个封装一个封装更新:

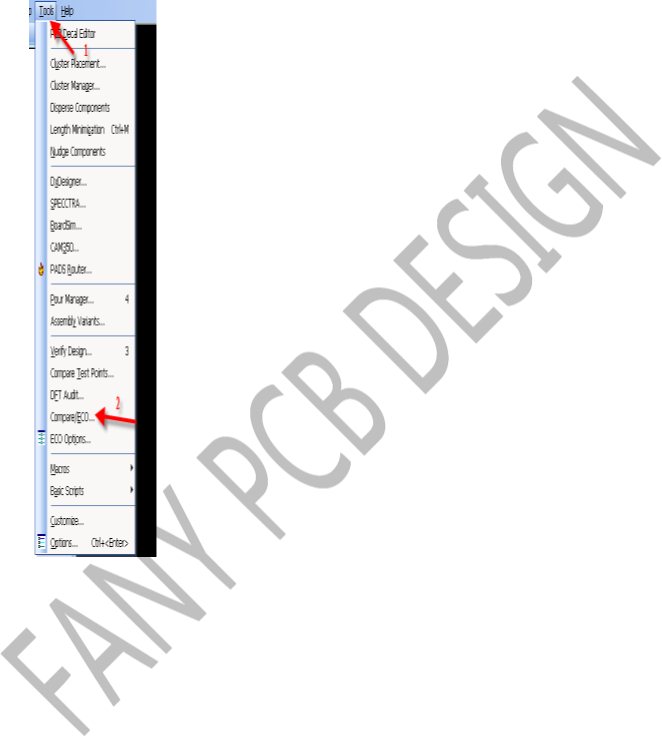

III、直接用 ECO 方式进行对比更新原理图,然后在 PCB 上进行库的更新(若有封装修改,原理图中 Parts 名不变(Decals 名无要求)。更新封装时注意 Decals 与 Parts 的对应,一般此方法只适用于 Decals 与 Parts

一一对应,若不对应,用此方法导入后请与原理图进行 ECO,不然会导致错误)

Ⅱ、其它格式原理图:

(1)、导成 ASC 文件,若同位号对应的 Decals 和 Parts 名都无改变,直接将网表导入要更新的 PCB; 若有改变,则按(2)

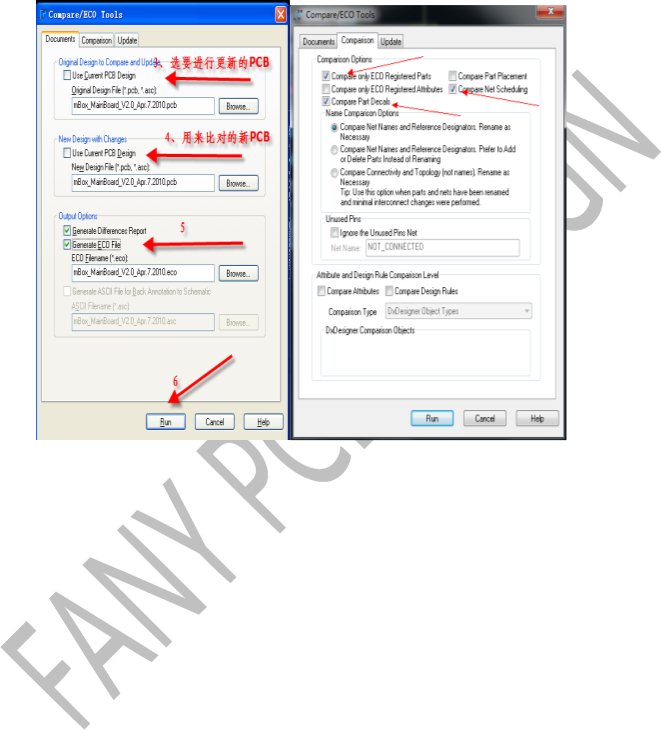

(2)、用新的网表导出一块最新的 PCB,用新的 PCB 与要进行更新的已做的 PCB 进行比对,再进行 ECO(IMPORT 产生的 ECO 文件) 比对如下示:

将产生的 ECO 文件导入 PCB 中,更新即完成。(完成后可以再执行一下比对过程,看结果是否显示 无差别,检验更新是否完成)

6.封装检查

完整的pdf格式文档51黑下载地址:

pads网表导入方法详细解析.pdf

(1.1 MB, 下载次数: 63)

pads网表导入方法详细解析.pdf

(1.1 MB, 下载次数: 63)

|