Dr. Archàbeau˿t为IBM之资深EMI工程师,在EMI之分析上有非常深入之研究。我曾于 2002 年初参加过其于马里兰大学开办之一短期课程,受益良多。同年 8 月间于 IEEE 研讨会寻得并购买本书,特将之整理编译以与大家分享。

Bruce上课之费用极为高昂,但确有其价值。我参加过其课程后曾与其联繫希望能促成其至台北开课,惜因时间、费用等因素未能实现,殊为可惜。但花些时间研读其着作,相信也可让大家获益不少。 本书内容阐述许多 EMI 之基本观念,对于 EMI 工程师是很好的教科书。同时对于相关之产品设计工程师,如电子、Layout、机构工程师,也是建立正确 EMI 观念之教材。毕竟,好的 EMI 产品设计是要各部分配合的。阅读本书可以知道要如何做好 EMI 设计,更重要的是知道其原理为何,让你不仅可以知其然,更知其所以然。

对不同的人而言,EMI/EMC控制代表着不同的涵义。对商业应用言,如录影机、个人电脑、电视机等,其管制规范较之军规/TEMPEST标准要鬆一些,但是。其还是有一定之困难度。商用产品较鬆标准的结果是,设计人员常被要求要降低干扰及耐受特性,以因应降低生产成本之目的。在EMI/EMC设计上之取捨很清楚,但对于是否绝对需要某些 EMI/EMC元件就没有那麽清楚了。传统上,EMI/EMC工程师使用以往之经验、公式、材料手册上之图表,来从事产品设计之各个阶段。在大学或是任何机构裡,很少有高品质之EMI/EMC工程师等级之训练,许多在此领域工作之工程师,会发现到这种传统之方法会越来越不适用了。 ,太空,以及其他因安全原因必须控制辐射之应用,武器系统,通讯等,对 EMI/EMC之要求都是远在商业要求之上。这些更高等级之考量,需要更多之EMI/EMC设计,及更高之花费,同时还面对要降低成本之压力。 EMI/EMC 的问题是肇因于器材内之导体上之时变电流,称之为『di/dt 杂讯』 。电流之变化产生了电磁场辐射。相反地,外来的电磁场能量也会导致电路上的

『di/dt 杂讯』 ,造成错误的逻辑运算及器材之误动作。大多数的高速及快速上升时间之信号会造成EMI/EMC问题。这些问题会被连接到该器材之导线电缆所放大,在较低频率变成有效率之天线。典型之解决方桉是使用屏蔽之外壳,对输出入信号及电源线滤波,并且对机板上之信号线及电源平面提供滤波电路。而真正的问题是: 『加多少才是足够?』以及『会不会加太多?』

许多 EMC 工程师都会强调在产品研发之初期就要密切注意到 EMC 设计,此一『密切注意』 通常只是在 EMC设计准则中一长串的 『要如何..』 及 『不要如何..』 。这些准则通常是根基于以往的产品经验,而且很多准则会互相牴触。我们缺少的准则是,在根本原因分析中我们不真正的知道为什麽我们需要这一项准则,或者,更重要的,当某一项准则因有些设计限制而无法实施时应使用哪些替代方法。设计者只是简单的被告知『这样做或是那样做..』 。

典型的设计程序之结果如下:

EMC 工程师提供给产品设计工程师一个 EMC 准则的表列。 产品设计者无法、或是不愿意遵循所有的 EMC 设计准则。 产品设计只使用了方便导入之 EMC 设计准则。 样品在 EMC 实验室中测试,无法通过。

EMC 工程师及设计工程师花费 2 週至 2 月的时间增加电容、ferrite bead滤波、导电衬垫、金属弹片直到问题解决。 以修正过之 EMC 更新产品设计,开始量产准备。 这一设计流程的结果是延迟第一批货交货的时间以及增加产品成本,因为这些EMC 零件并不是原始设计。显然的,这不是我们所希望的流程,但它是最常见的流程。

本书之目的在于移除这些 EMC 设计流程之谜思。许多人将 EMC 设计看成是一种黑箱魔术,大胆猜测,或是更差状况。EMC 设计是极端複杂的。有许多内部连接之现象发生,许多是难以预测的,特别是在其同时发生时。如果每一个潜在之干扰源都个别考虑到,那麽可以一个个的对每个干扰源进行适当的设计对策,这样,设计者就不会在看整个产品时感到疑惑了。 适当的 EMC设计并不仅仅是一串的准则。其需要有完整的程序,考虑到每一潜在源头以及依序一个个的解决。自然的,主要的目标还是要确保产品之功能不被影响。如果,在设计阶段,EMC 的考虑与功能性之考量都被包括且协调,则设计者才能在两方面都获致成功。

第二节 EMI干扰源

降低 EMI 最有效之方式是控制信号之分布以及它们的源头。所以,这些信号是从哪裡来的?这些信号的起源可能有很多种,但是最主要的干扰是来自于 IC 中的高速切换电流。

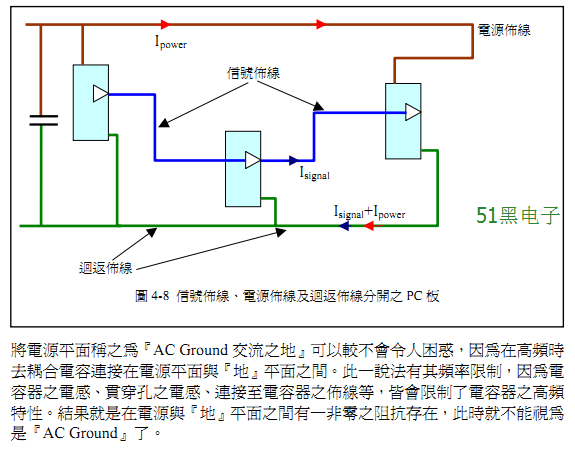

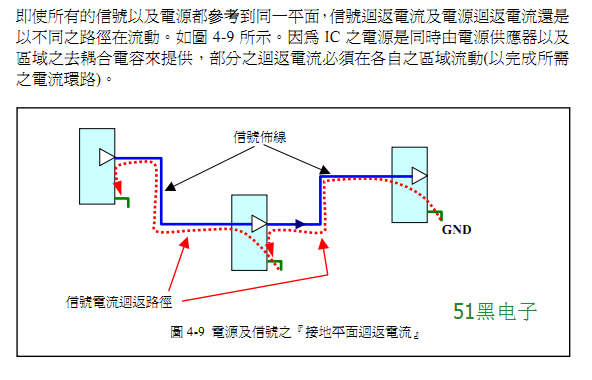

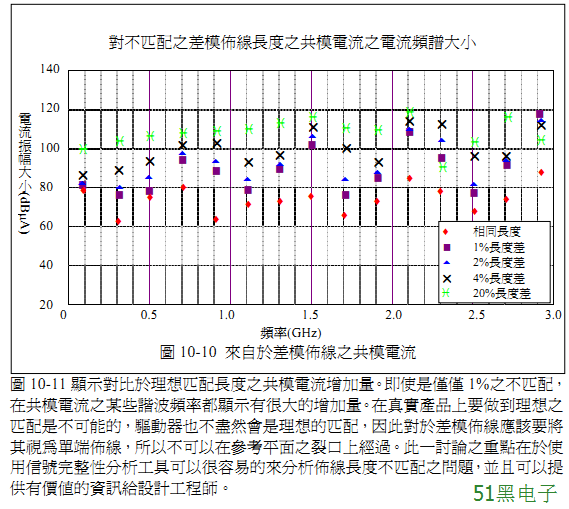

几乎所有的 EMI 干扰来自于产品某处存在之共模电流。所有的这些共模电流都来自于某些功能上之工作电流。如果这些工作电流能够好好控制,让它只含有工作上所需之谐波,来自于高频谐波造成之不必要干扰就可以降低。 此一共模电流的来源最有可能是工作信号之迴返电流路径。当电路佈局工程师花很多精神在连接电路间之路径时,很少会注意到迴返电流路径。当时脉信号在10MHz 以下时,迴返电流不会是个问题。现今,机板上之时脉速度多至 200 至400MHz,且资料汇流排之速度高达 1GHz 是很普通的,因此,信号之佈线路径应该视为是微波传输线(Transmission line)。不论是对EMC特性或是功能特性而言,信号线之高频迴返电流路径都是非常重要的。

第三节 电感 Inductance

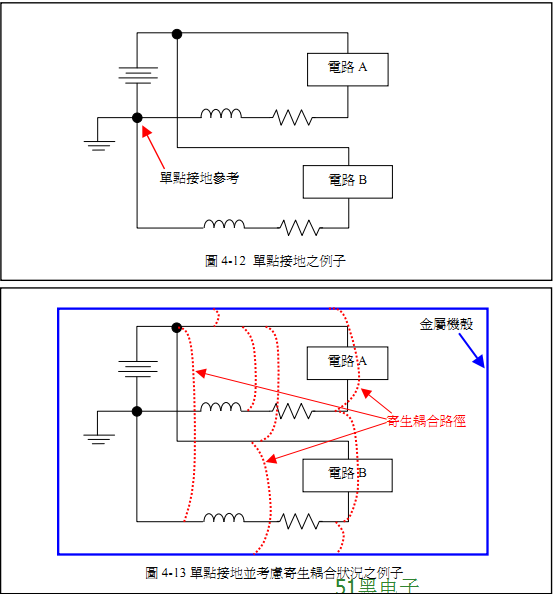

一个通常被误解的观念是对于电感的认知。初级工程师把电感认为是一个特定之零件,如在电感器(Inductor)及变压器元件中,而很少考虑到在接地参考平面、信号佈线等等电流路径上之电感。有电流流经一个环路,就会有电感的存在。有时候我们并不知道整个的路径,并且整个路径中也可能只有部分区域会造成辐射,所以区域电感的观念也很重要。将区域电感组合起来,就可构成完整的环路电感了。也就是说,若是路径一部份之区域电感被考虑到且将其降低了,则整个路径的总电感也就降低了。

现今产品所使用的高速信号使得环路电感及区域电感变的比以往都要重要。即使是一个完美的超导体都会有电感。当电流流过电感阻抗时,会产生一个电位差。此一电位差会导致接地参考平面的杂讯、信号位准降低、造成 EMI 辐射的产生。

第四节 接地 Ground

如果说电感是一个经常被误解的观念,那麽『接地』就是『最常』被误解。当使用『接地 Ground』这个词彙时,设计者通常是指许多种不同的事。它可能是指相对于 50/60Hz 之交流电源之安全接地(Safety earth reference)。它可能是指对高速佈线之信号参考点(Signal reference)。它可能是指在PCB上之电源迴返(Power return),或者,它可能是指金属机壳之机壳接地点(Chassis reference)。它甚至也可能指的是真正的大地接地点(Earth ground),像是在EMI 开放测试场地(OATS)。 很清楚的,在所有的这些场合中『接地 Ground』这个字不可能都是同样的电位位准,但这却是最原始『接地 Ground』的定义。 『接地 Ground』是一个零电位的点。实际上, 『接地 Ground』或是『零电位』只存在于无限值(infinite),因之,除非我们使用了非常长的导线,否则真正的零接地电位是不可能存在我们的产品之中。

较清楚且明确的表示法是将在不同之场合将『接地』描述成说: 『大地接地Earth-Ground』 、 『接地参考点 Ground-reference』 、 『电源参考点 Power-reference』 、『机壳参考点 Chassis-reference』 ,等等。则说的人与听的人就都可以明白了。

第五节 屏蔽 Shielding

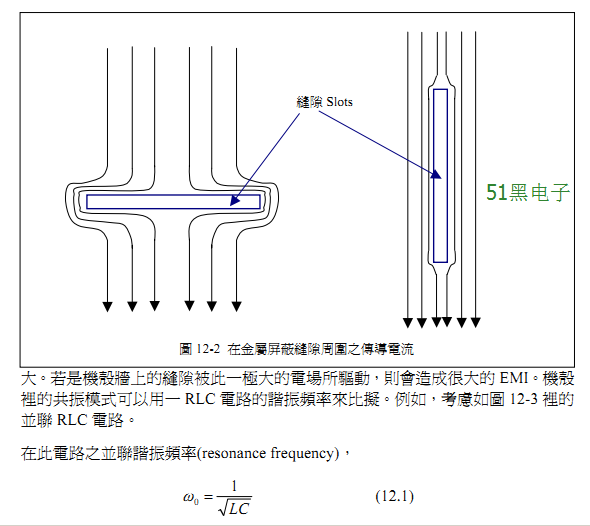

另外一个在 EMC中容易误解的是屏蔽的观念。古典的屏蔽理论讲的是一个平面波撞击到一个有开孔的屏蔽物。以我们现在所接触的产品的构造言之,设计者所要面对的撞击有开孔的屏蔽物的并不会是平面波,所以使用古典之趋近法可能会误导结论。

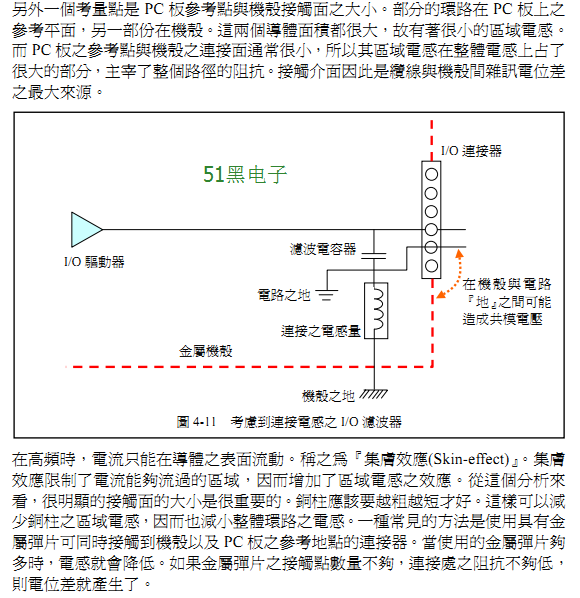

在典型的产品中,能量的来源很靠近外壳之屏蔽及开孔。此一密切靠近之结构,使得在与屏蔽间存在电容、电感、或是电磁耦合感应电流。能量来源与屏蔽体间之距离是非常重要的,会造成耦合现象之巨大差异。在屏蔽上生成之感应电流找到适当之开孔,就会将能量转移到屏蔽体之外,变成辐射干扰了。 第六节 结论 对 PCB洽当的 EMC设计,最有效果的方法是考虑到每个不同的信号源头,并且在信号源头将其控制住。后面之几章将会详细的说明不同之信号源头,以及如何来控制每一个个别的来源。在设计阶段的早期就必须要考虑 EMC,并且持续到全部的设计阶段。

很重要的是不要把EMC设计看成是一个简单流程的步骤。在设计进行中,有许多工程上的折衷方桉(trade-offs)要考虑。如果设计者了解到我们的目标,并且了解到发生 EMI 辐射的源头在哪裡及如何去控制它,那这个设计者就能够很成功的掌握并做出正确的折衷判断。如果EMC的设计流程只是遵循一连串的准则,哪麽当这个准则变得很困难或是无法实现时,此准则就会被忽略掉,此产品就会失败,那麽整个流程就要再来过一次。

为了要完整的了解跟干扰源头有关的完整程序,一些基本观念必须要了解的很清楚,譬如说『接地』 、 『电感』及『屏蔽』 。在这些方面有很多的错误观念,本书的目的就是要协助来了解并降低对它们的误解。

(Coupling Mechanism) 本章已经谈过了解信号的出处以及其如何溢出系统是很重要的,但是还未提到在源头与最后的洩漏点之间的耦合机制。通常,一旦说产品在EMC测试实验室中测试不通过,再想要改善其耦合机制就太晚了,但是在某些情况之下,还是有一些方法可以改善以解决此问题。

第一项 桉例一,时脉信号由接缝洩漏

假设在 PC 板某处有一个时脉信号源,而由一个机壳之缝隙洩漏出去。如果辐射之频率为时脉基频之第七次谐波或更高的谐波,通常最好的解决方式是在意图信号上加滤波器。如果系统之运作确实需要快速的上升时间注,或是说此一有问题的频率的确是必要的较低阶谐波,则在源头加滤波器就不太适宜了。 时脉信号传递到洩漏缝隙的方式有很多种。最可能的方式是信号在机壳内辐射,然后再由开孔洩漏出去。经过缝隙附近的一条内部缆线或电线也可能会造成缝隙之洩漏。有时候移动内部缆线的位置就可以降低辐射的强度(如果这是部分原因的话)。时脉信号可能会耦合到其他的信号导体而进入到内部缆线然后辐射出

注:通常,时脉以及资料驱动器的上升时间并不需要到 IC所能驱动的那麽快。但是,设计者通常会以较快的上升时间当成预设值,以使信号 timing 分析容易些。这样通常会让 EMC 设计上增加成本,因为要多来控制许多不必要的高频。在整个设计裡,会有许多的妥协要做,一旦知道了所造成的额外成本,通常较低的上升时间就可以被接受。 去。一旦找到了耦合的机制,就可以加以控制。有许多可能的耦合路径,无法在这裡一一的描述。

第二项 桉例二,时脉信号由未屏蔽之缆线洩漏 如前所述之源头端加滤波方式还是可以使用。然而,在此桉例,时脉信号是藉由一个非屏蔽缆线传递到机壳之外。时脉信号适一个非意图信号,因为我们根本就不希望它在那条导线上出现。能量可能由时脉佈线直接耦合到I/O之佈线,或经由另一个导体。能量可能在机壳内辐射然后耦合到 I/O 连接器以及/或是佈线。同时,如前面之例子,内部缆线可能作为将非意图信号由其源头传递到 I/O连接器之一条路径。

第五节 结论

在实验室中并没有按部就班的指导准则可让我们用来解决 EMC问题。不过,有一些一般性的原则可以协助来减少花费的时间。随机的应用铜箔胶带、ferrite beads、以及滤波器并不是最容易或最快的解决问题方法。 了解信号从哪裡来是很重要的。通常,信号可以在其源头就控制住,那就不会造成系统信号洩漏的问题,因为杂讯信号的来源已经没有了。如果无法在于源头处控制,那就要来了解信号是如何由机壳中洩漏出去的。简单的电压探针在此方面是最有效的分析工具,因为它消除了近场探针可能的误导。此种接触式之电压探针可以用来确认造成洩漏之机壳缝隙、缆线上的非意图信号、以及屏蔽缆线之不当连接方式。最后,了解在信号源头以及洩漏点间耦合之机制可以减少解决问题的时间。

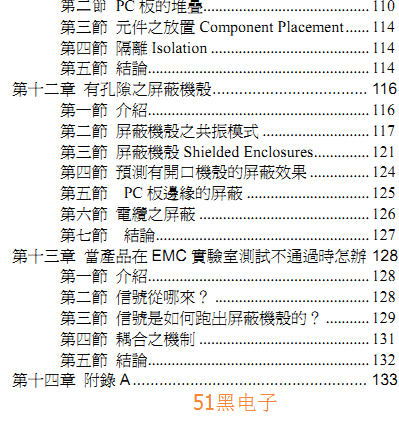

完整的pdf格式文档51黑下载地址(共137页):

印刷电路板设计-在真实设计里的EMI控制.pdf

(4.59 MB, 下载次数: 90)

印刷电路板设计-在真实设计里的EMI控制.pdf

(4.59 MB, 下载次数: 90)

|