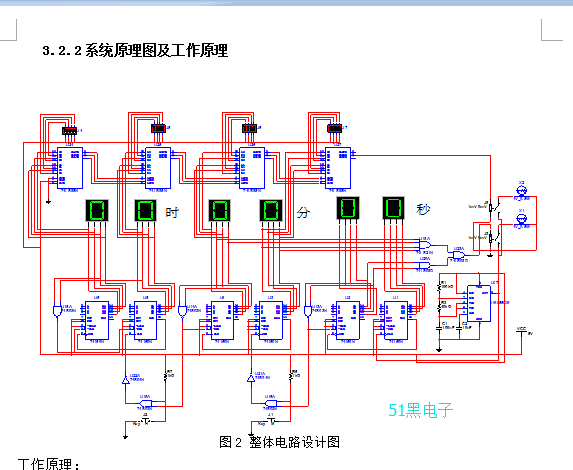

工作原理:

1.首先,由555定时器组成一个多谐振荡器得到1HZ的秒脉冲,秒脉冲发生器的输出端接到每个计数器的时钟输入端。

2.数字钟的分、秒计数部分均为六十进制计数器(显示00~59),采用两片74LS160来实现。个位为十进制,十位为六进制,当个位计数到9时,再来一个脉冲变成0,同时产生一个进位信号,给十位提供一个脉冲,使十位计数加1。而数字钟的时计数部分为二十四进制计数器(显示00~23),也是采用两片74LS160实现。当开始计数时,个位按十进制计数,当计到23时,这时再来一个脉冲,回到“零”。所以,这里必须使个位既能完成十进制计数,又能在高低位满足“23”这一数字后,十计数器清0,图中采用了十位的2和个位的3相“与非”后再清0。当秒计数器计到59时,再来一个脉冲变成00,同时产生一个进位信号给分计数器的CP输入端;当分计数器计到59时,再来一个脉冲变成00,同时产生一个进位信号给时计数器的CP输入端;当时计数器计到23时,再来一个脉冲变成00。

3.数字钟的校正部分主要是通过开关实现的。当需要进行校正时,将开关J1打开,J2打到+5V时为分校正,J4打到+5V,J4打到上面时为时校正。

4.当计数器在每次计到整点时,需要提前十秒报时,这可采用译码电路来解决,即当分为59时,且秒计数到50时,输出一高电平,经过一系列门电路驱动灯泡发光,完成整点报时。

5.数字钟采用4片74LS85和4个拨码开关构成闹钟电路。将时钟电路显示十进制数对应的二进制数A与拨码开关所设置的闹钟时刻B做比较。从时十位到分个位,逐级比较,若均分别相等,从最低位(分个位)对应的比较器74LS85(U27)的OAEQB输出高电平,完成闹钟功能。

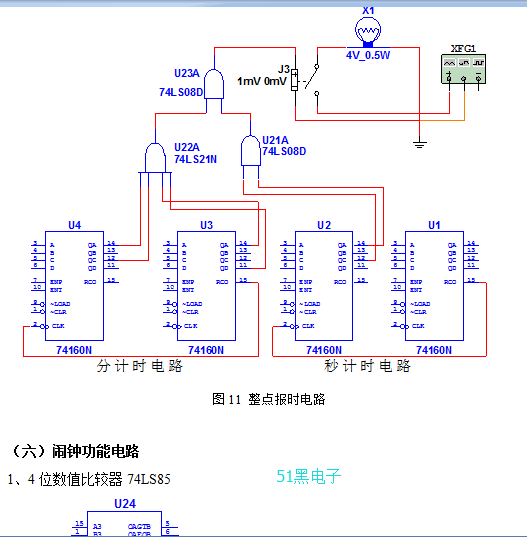

(五)整点报时电路

电路应在整点前10秒开始报时,即在59分50秒到59分59秒期间时,报时电路控制信号。

当时间59分50秒到59分59秒期间时,分十位、分个位和秒十位保持不变,分别为5、9和5,因此可将计数器十位的Qc和Qa,个位的Qd和Qa及秒计数器十位的Qc和Qa相与,从而产生报时控制信号。

完整的Word格式文档51黑下载地址:

数字时钟设计.docx

(202.29 KB, 下载次数: 87)

数字时钟设计.docx

(202.29 KB, 下载次数: 87)

|