|

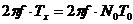

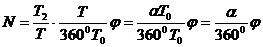

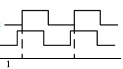

一.设计任务 (1)两个工频电压信号可以通过RC网络实现,调节电阻R的值可以改变两信号的相位差 (2)两输入正弦信号的输入幅值的变化范围10~100mV。 (3)两个信号的相位差采用数码管进行数字显示。 (4)相位差的数字显示分辨率要求0.1℃。 (5)具有量输入信号的“超前”和“滞后”判别功能。 二.设计方案分析 相位差是工业测控领域经常需要测量的参数,如电力系统中功率因数的测量、铁路系统中相敏轨道电路相位差的测量以及科氏质量流量计中的相位差测量等等。而相位差的测量又不同于传统的电压、电流信号或物位、温度量的测量。首先,相位差信号依附于电压、电流信号中,如何剔除电压、电流、频率变化对相位差测量的影响是相位差测量中很重要的一个方面;其次,相位差是一个比较量,测量两路信号之间的相位差不仅需要保证两路信号的频率相同,而且要排除由于两路信号的幅值等其它因素不一致而对测量造成的影响。因此,如何准确可靠地测量相位差是值得研究的课题。 通过查阅资料发现,一些常用的方法如下图所示 由于本设计是测量工频信号(50Hz)的相位差,考虑到设计电路的经济性等,故选择基于过零检测方法中的基于异或门的测量方法中的电压测量法来测量电路即可。其常用两种方法原理如下: 1.相位瞬时测量原理 首先将两同频率的正弦信号经过放大、整形变换成同频率的方波信号;两方波信号经鉴相电路,输出脉冲的宽度正比于信号的相位差;鉴相器的输出控制一闸门,在两信号相位差时间内,闸门打开,频率为f0的标准脉冲进入到计数器,则计数器的输出正比于两信号的相位差。各点的工作波形图如下图所示。设两信号的过零时刻之间的时间差为Tx,在Tx时间内通过的脉冲个数为N0,所以 ,式中T0为计数脉冲的周期。设被测信号的频率为f,两信号的相位差为 ,式中T0为计数脉冲的周期。设被测信号的频率为f,两信号的相位差为 ,则 ,则 ,显然等式左边就是两信号的相位差: ,显然等式左边就是两信号的相位差: ,可见信号的相位差正比于计数脉冲的个数。但是该表达式信号的相位差还和被测信号的频率有关,所以不能直接测量出信号的相位差。故该方法适合于测量固定频率信号的相位差,不适合于测量两信号频率变化的情况。 ,可见信号的相位差正比于计数脉冲的个数。但是该表达式信号的相位差还和被测信号的频率有关,所以不能直接测量出信号的相位差。故该方法适合于测量固定频率信号的相位差,不适合于测量两信号频率变化的情况。 相位瞬时测量原理框图 瞬时相位测量工作波形 2.相位平均值测量原理 为了消除被测信号频率对测量结果的影响,可以采用测量信号相位差平均值的方法实现,其工作原理如下图所示。该原理图只是增加了第二个闸门和分频器两部分,分频器的作用是产生一个控制第二个闸门开通的时间T2,T2=αT0,其中α是分频系数,另外要求T2远大于被测信号的周期T。可见在T2开启第二个闸门开通的时间里,有许多组脉冲通过第二个闸门进入计数器,每组脉冲的个数为N0。因此进入计数器总的脉冲个数为: 。又因为 。又因为 ,所以 ,所以 。 。 其中α是常数。可见,无论测量什么频率的信号,两信号的相位差总是与计数器所计的脉冲个数成正比,与信号的频率无关。 相位平均测量原理框图 本题目明确了是两个频率为50hz的工频信号,因此选用相位瞬时测量。为了能够正确显示两信号相位差的大小,实际电路中还应有控制逻辑电路,其目的是顺序产生“测量→锁存→清零”工作时序信号,保证系统的正常工作。 三.测试方案分析 受限于软件模拟及计算机性能,本设计采用分模块调试验证,然后用示波器测出每一分模块的输出,用函数发生器加到下一模块的输入 四.单元电路设计、逻辑控制电路设计 1.放大整流及鉴相电路 这里设定可调R2为50kΩ×0.2=10 kΩ,通过理论计算可得 相位差?φ=arctan(2π×50× × × )=72.3° )=72.3°   分别是信号源和电容两端电压,由示波器波形可知 分别是信号源和电容两端电压,由示波器波形可知  均通过比较器lm393获得良好整形,ch3是通过74ls86鉴相所得波形,由示波器可知其频率为100hz,占空比为40%,且经1n4148反向限幅使得送入74ls86的反向电压近似为0,能正常工作 均通过比较器lm393获得良好整形,ch3是通过74ls86鉴相所得波形,由示波器可知其频率为100hz,占空比为40%,且经1n4148反向限幅使得送入74ls86的反向电压近似为0,能正常工作2. 相位超前/滞后判别电路 Part1: CLK端接 ,D端接 ,D端接 ,所得理论曲线如下图。 ,所得理论曲线如下图。   实验与理论吻合 实验与理论吻合Part2: D端接 ,clk端接 ,clk端接 ,所得理论曲线如下图。 ,所得理论曲线如下图。   实验与理论吻合 实验与理论吻合3.逻辑控制电路 在鉴相脉冲信号作用下,如果要完成计时,就要产生一个控制脉冲计数器电路的计数信号K1和控制脉冲计数器清零信号K2。为了能够清晰的显示信号相位差的值,要求控制计数器计数时间为1个鉴相脉冲的周期,保持(锁存)计数器的时间为8个信号的周期,对计数器清零的时间为1个信号周期,实现上述功能需要一个至少模为10的计数器,本实验采用74LS160完成,计数器在“0000”状态时输出给“相位差计数器”输出一个清零信号,该信号可以采用74LS160的进位信号Co;当计数器在“0001”状态时,使“相位差计数器”开始计数;在计数器从“0010~1001”状态时,“相位差计数器”处于保持状态。电路原理图如下图所示。 4. 时基脉冲信号产生电路 鉴相电路为频率为100hz,周期为10ms,精度为0.1°所以要求时基脉冲能在10ms内产生最大180°相移角测量,即1800个周期。所以时基脉冲的周期为1/180 ms,频率为180khz 利用74ls14如图连接成多谐振荡器,调节可变电阻R2的阻值,得到180khz的时基脉冲。 5. 脉冲计数及相位差显示电路 本实验要求精度为0.1°,两信号最大相位差是180°(本实验移相电路仅能达90°),故最大显示数应为1800,本实验采用由四片74LS160级联构成的模10000的计数器。当K1信号为高电平时计数器计数,K1为低电平(在K2为1时),计数器保持不变;只要K2输出低电平,计数器立即被清零。计数器的数值通过显示译码器直接在LED显示,其显示的值即为被测两信号的相位差大小。其原理图如下所示。 其中xfg2模拟的为第一步鉴相电路输出的鉴相脉冲,xfg1模拟的是第四步时基脉冲产生的时基脉冲,其测量结果如晶体管所示,为72.0°在误差允许范围内。 五.实验结果及分析 实验另多组数据如下表所示

因信号经放大10倍后才进行整流鉴相,所以100mv与10mv仅有占空比小数位数差距,可以看出100mv比10mv更为精确一些,因波形发生器模拟鉴相电路时占空比小数位数不可调,便未记录。从表中可以看出理论和实际误差相当小,所以测量结果近似是正确的。

以上的的Word格式文档51黑下载地址:

|