压缩包保护各模块的原文件,原理手绘图。可实现全部功能。

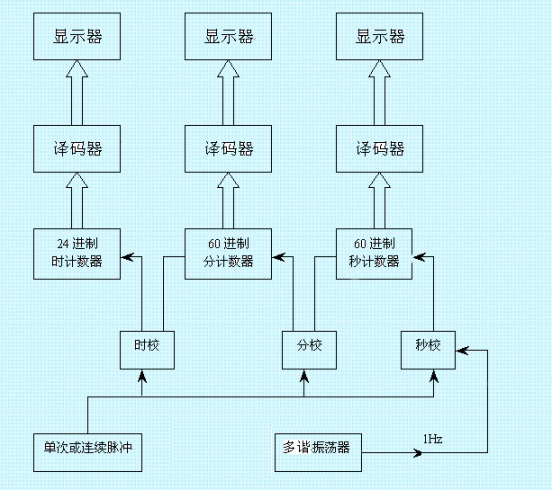

总体设计 数字电子钟一般由振荡器、分频器、计数器、译码器、显示器等几部分组成。采用的555定时器构成的多谐振荡器来产生秒信号。“秒”、“分”计数器为六十进制计数器,小时为二十四进制计数器。仿真软件中选择合适的显示器件,由于走时不准确而造成显示的时间快或慢,就要对表进行校准。这一功能利用手动单脉冲或连续脉冲对其进行校准。由电源电路提供稳定的+5V电压。 (2)数字电子钟设计框图

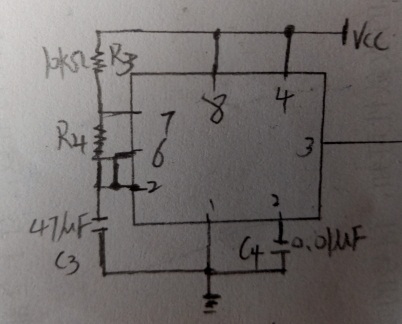

三、详细设计 (1)1Hz标准脉冲发生器: 1Hz标准脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量。采用的555定时器构成的多谐振荡器来产生秒信号。取参数R 3 =10K,R4 =10K,C3=47μF 。f=1/[ln2(R3+2R4)C3]≈1Hz,即产生1Hz的脉冲信号。而单个周期为T=(R3+2*R4)*C3*ln2=1s。

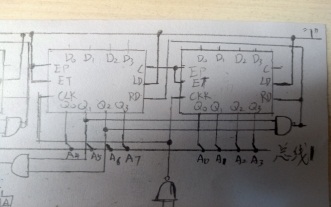

1Hz标准脉冲发生器 (2)计数器 计数器由时分秒组成,分秒为60进制计数器,计数范围为00~59。时为24进制计数器,计数范围为00~23。 设计的60和24进制加法计数器都大于一个74LS160的计数范围,所以需要级联。当且仅当秒的个位计数到10的瞬间,即输出为1010时,向本位发送一个清零信号,并同时向十位发送一个进位脉冲。但是74LS160的清零方式为异步清零,所以必须要把脉冲调整到一个较低的周期,才会产生有效地清零和进位信号。为了使清零和进位同步进行,在清零的输出端需要引出一根线,加上与门引入下一级计数器的输入端。这种可以实现多重清零的方式。 分、秒都是60进制(00~59),所以它们的电路都是一样的,采用2片74LS160和与非门实现,该芯片为十进制加法器,D四个引脚全部接地,表示从0开始计数。逻辑门组是实现的关键,当记满59时,再来一个脉冲就清零变为00,接着再重新开始计数。 秒计数器:

分计数器:

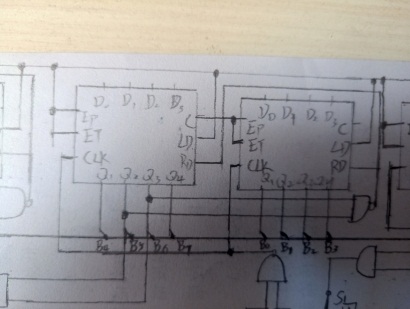

用的2片74LS160芯片以及与非门实现24进制(00~23)。时计数器的十位是二进制,个位是十进制,同时和与非门相连,实现满24时清零。 时计数器:

(3)译码显示

DCD-HEX数码管4条引脚从左到右对应BCD码位的左高右低。在Multisim仿真当中其内部自带译码功能,无需设计译码电路,可直接连接计数器显示时间。 (4)校时电路 由于走时不准确而造成显示的时间快或慢,就要对表进行校准。由于CLK连续脉冲(1H Z )只能送给秒计数器个位芯片的CLK端,且在校准时,仅需校准脉冲,而秒脉冲无效。因此设计门电路满足此功能。 当A为0正常计数,当A为1时采用校对脉冲输入。但为了满足校对时不产生进位的需求,在进位端同样设计一开关,由A控制。当A为0时,开关闭合。计数器正常计数和进位,而A为1时,校对脉冲输入,开关断开,不再产生进位。 四、组装电路并调试 按照原理框图对数字时钟各部件进行组装连接,调试。图见尾页 五、元件明细表 六、心得体会 这学期一开学就待在家里线上教学,虽然不能走出去,但通过线上老师辛苦的教学,让我在家也不会耽误学习进度。这次设计自己感觉最大的收获是更好的认识了这门学科以及自己所学的专业。之前一直有疑惑,自己学这个能干什么?感觉自己所学的跟日常所见是不一样的。但是这次设计的成功完成,让我看到了另一番不同的天地。极大提升了自己的学习兴趣。这次设计也加强了我对multisim仿真软件的运用,相信对我以后的学习有很大帮助,这次课设也进一步巩固了课上学习的各种知识。 当然突然拿到这个项目还是比较迷茫的,无从下手。所以我花了些时间去分析题目,设计原理图,了解基本运行原理来论证和改进。基本方案确定后,再去查资料,通过Multisim仿真、请教同学来重新改进。虽然实际运行中出现了很多问题,换了不少设计,有时无法找出错误就换元器件重新接线。有些在理论上可行的电路在调试中未必正确,这就需要耐心、仔细分析和解决问题,不断尝试才能得出正确的答案。最后完成了项目并验证,把理论和实际紧密的联系在了一起。

附录:总体电路连接图

全部资料51hei下载地址:

仿真源文件.zip

(1.63 MB, 下载次数: 140)

仿真源文件.zip

(1.63 MB, 下载次数: 140)

手绘电路图清晰.7z

(126.09 KB, 下载次数: 39)

手绘电路图清晰.7z

(126.09 KB, 下载次数: 39)

|