设计简易钟表逻辑电路,功能内容包括(基本计时、显示功能、具有分、秒的数字显示),能实现停表和设置时间功能。

设计电路3.1.1元器件型号

设计电路3.1.1元器件型号计数器74LS160D、与非门74ALS00M、与门74AS08M、非门 74ALS05AM、数码管DCD_HEX。

3.1.2 秒钟电路

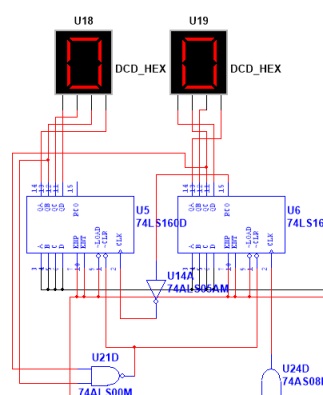

图3-1 秒钟电路

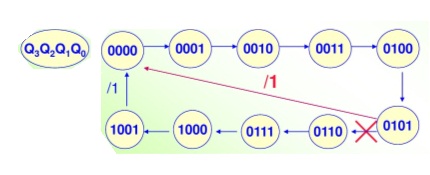

秒钟电路搭建如图3-1,由两片74LS160构成60进制计数器,十位由十进制计数器加与非门构成六进制计数器,状态图如图3-2,中间采用串行级联连接(由十位计数器的ENP和ENT端连接到个位计数器的RCO进位端),来构成60进制计数器。

图3-2 74LS160十进制构成六进制状态图

3.1.3分钟电路

3.1.3分钟电路

图3-3 分钟电路

分钟电路如图3-3与秒钟电路搭建并无太大区别,这里的秒到分进位时钟信号,直接选取的预置数置一的低电平信号。

3.1.4 小时电路

3.1.4 小时电路

图3-4 小时电路

3.1.5 特殊功能键电路

图3-5 特殊功能键电路

时钟调节和分钟调节功能键电路如图3-5,由VCC提供高电平信号,当按下按钮时,经过非门,刷新与门的电平信号,从而为CLK提供时钟信号,实现调节时钟的功能。

图3-6 暂停功能键

暂停时钟功能,由开关A实现如图3-6,当打开开关时,时钟信号关闭,秒钟的时钟信号源关断,暂停计时。

3.1.6 简易钟表逻辑电路

图3-7 简易钟表逻辑电路

3.2相关计算74LS160进制计算方法有,当使用同步预置数法连接时,进制数为

,当使用异步清零时,进制数为

。

60进制计算,本设计60进制计数器构成由两片74LS160通过同步预置数的方法连接而成,同步预置数连接方法进制计算公式为

,因此Q为0101,为5。D为0000,为0。并采用串行级联方法得60进制计数器。

24进制计数,本设计24进制计数器构成由两片74LS160通过异步清零的方法连接而成,异步清零连接方法的进制计算公式为

,因此十位的Q为0010,为2。个位Q为0100,为4。D为0000,为0。构成24进制计数器。

四、测试方案

4.1仿真测试的步骤

仿真测试步骤:

(1)秒计时进行仿真测试

先将时钟信号源频率加快,打开仿真开关,观看秒数码管时钟信号是否给入,观看个位进位信号是否给入十位,74LS160计数器是否构成60进制计数器。

先将分计时的CLK接入时钟信号源,同样加快频率,打开仿真,同样观看个位进位信号是否给入十位,74LS160计数器是否构成60进制计数器。断开仿真,将秒进位的信号接入分计时的CLK端(这里进位捕捉信号为L端的预置数低电平信号),启动仿真,是否成功由秒进位到分。

同前面秒、分测试方法相同

打开仿真,按动时、分调节按钮,是否有脉冲信号给入对应的计时数码管。打开暂停开关,计时是否暂停。

4.2实验数据

4.2实验结果分析和结论

4.2实验结果分析和结论本设计成功的完成了简易钟表逻辑电路的设计,实现了24小时制计时,以及小时和分钟的调节机制。采用了普通方波信号发生器,频率设置为1HZ,来提供1秒的时钟信号。通过6片74LS160分别构成了一片24进制和两片60进制计数器,实现了时、分、秒的计时功能,并通过七段数码管显示,相应的数字。

进行仿真实验成功不代表着现实实验成功,或许仿真中有恰当的地方,到了实验室就不一定恰当。

五、安装、调试中的问题、解决方法及效果5.1仿真调试电路过程中的遇到的问题

仿真问题1

秒钟进位信号给上去,是在8变9时进位,而不是9变为0时进位。

解决方法:

对74LS160的知识内容有些淡忘,在网上找到了74LS160构成进制的正确连接方法,当M>N时,进制连接采用串行连接或是并行连接方法。

仿真问题2

采用74LS160构成60进制时,采用的异步清零的连接方法,导致60秒进位信号给不到分,以为清零的信号太短暂,而没有捕捉到这个信号。

解决方法:

加入信号锁存器,在Multisim中使用俩个与非门构成RS信号锁存器,讲清零信号置位低电平信号接入RS锁存器,低电平S端,成功的捕捉到了清零信号,并成功进位。

仿真问题3

24进制计数器,制作错误

解决方法

将个位和十位的置数端连到一个与非门,连到复位端,构成异步清零的24进制计数器。

仿真问题4

成功的构成了24小时钟表,在加特殊功能键时,将开关的电平信号和秒分进位信号、分时进位信号进行相或时,可以调试,但无秒分进位信号和分时进位信号。

解决方法

将74LS160的异步清零接法,换成了同步预置数法,将相或换成了与开关低电平相与,实现调试功能。

全部资料51hei下载地址(仿真+文档):

简易钟表逻辑电路设计.rar

(616.74 KB, 下载次数: 35)

简易钟表逻辑电路设计.rar

(616.74 KB, 下载次数: 35)