摘要

一排整齐的高电平竟然被活生生的砸下一个缺口,是软件Bug,硬件故障,信号干扰,还是另有主谋?一个扑朔迷离的案件正在拉开序幕……

案发现场

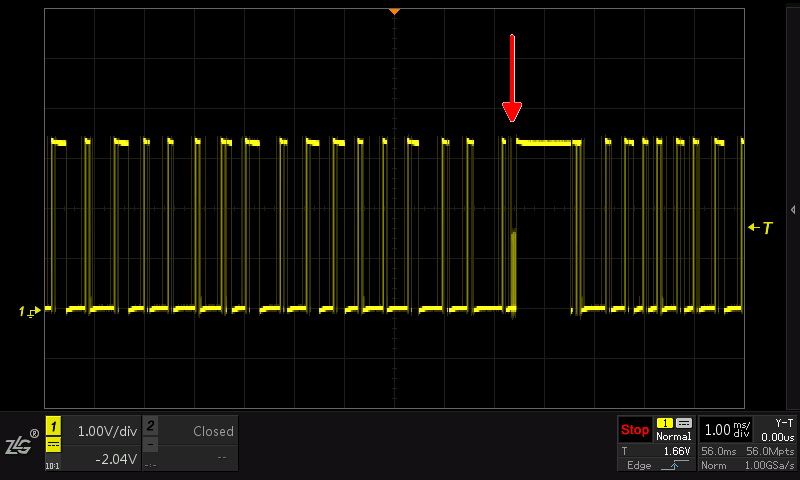

一日,在测试DATA线的信号时发现,一排整齐的3.3V高电平被活生生的砸下一个缺口,是谁如此胆大!当日的案发现场如下,随后又发现旁边的15根DATA线亦是如此,案情严重,刻不容缓!

图1 异常波形

现场侦查

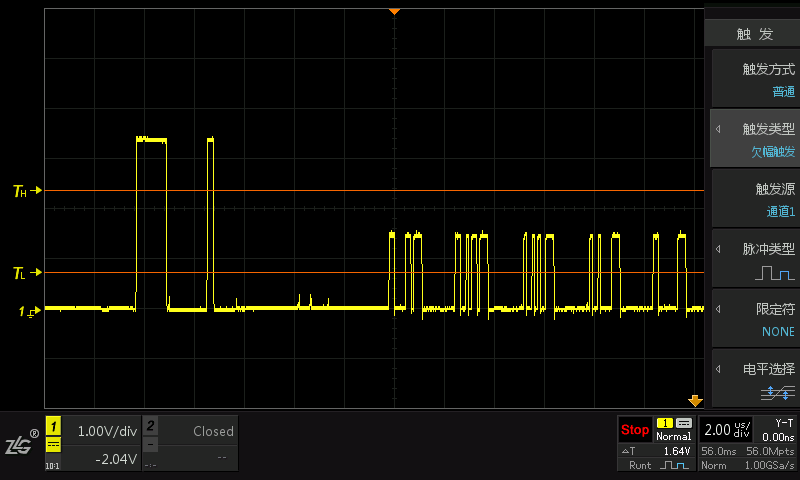

狄大人说:你要寻找蛛丝马迹,得有专业的家伙,ZDS2000系列示波器有个欠幅触发的功能,可以秒抓那个缺口,一试果不其然,如下:

图2 异常波形展开

案情背景

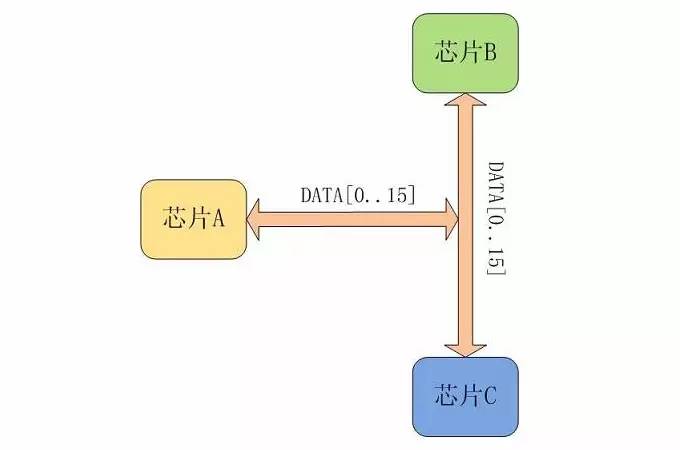

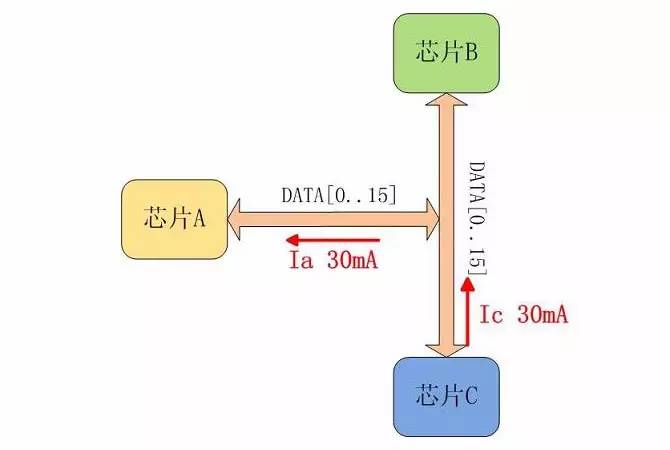

3.3V信号夹杂着1.5V的成分,这确实很棘手。经明察暗访发现,案件背景如下,三个芯片A,B,C共享同一数据总线DATA[0..15],而且测试三个芯片的管脚都是以上波形。

图3 芯片拓扑图

推理论断

这到底是何方妖孽所为?于是邀请各路高手一同探讨,一番激辩之后,出现以下猜测:

芯片A,B,C的电源域有问题 通信过程中受到干扰 芯片内部模块损坏

……

经查明,电源域没问题,第2、3点暂时无法排除。至此,案件依旧毫无头绪,毫无进展……

线索追踪

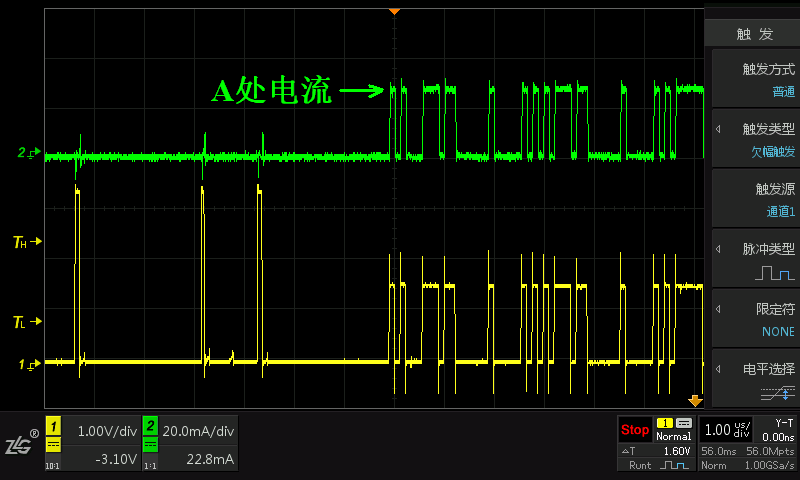

以上波形包含了AB,BC,AC间的通信数据,而且1.5V的占比比较小,或许是发生在某两个芯片之间。经过进一步测试,有了重大发现!

1.5V的出现竟然对应着BC间传输使能信号(绿色波形)

图4 BC使能信号

现在来看有两种可能: A在干扰总线 A没有干扰总线,是芯片B、C内部的问题

马上断开A的DATA0脚,上电却无法启动,看来还需另找线索了

柳暗花明 查找了一些资料,基本都是一些“一端拉高一端拉低”的说法,难道是B输出高的同时C拉低总线了?要怎样证明呢?

经过讨论,要找出拉低总线的元凶,最好的办法是看电流是否增大,依此思路,分别割断ABC的DATA0脚,串线连通,结合CP8030A电流探头和ZP1025S探头,测试结果如下:

1、芯片A处DATA脚电压、电流波形如下,电流约为30mA

图5 A处电流

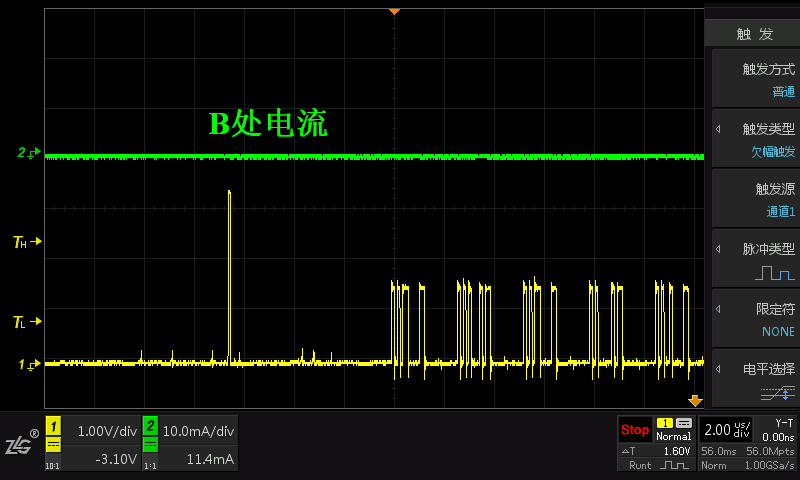

2、芯片B处DATA脚电压、电流波形如下,电流几乎为0

图6 B处电流

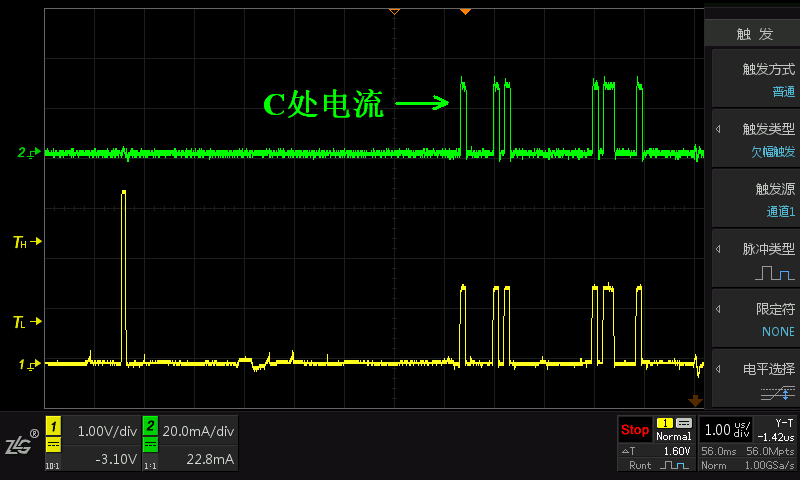

3、芯片C处DATA脚电压、电流波形如下,电流约为30mA

图7 C处电流

结果表明,1.5V对应的位置其电流竟然达到30mA(远远超出正常IO口的电流值),且宽度与1.5V的宽度一致。

真相大白

结合电流钳的箭头标识,可进一步确定电流方向,如下:

图8 电流方向

我们可以判定,30mA的电流方向是由C到A,BC间传输数据,A本不该插手,如今它却给总线制造了30mA的异常电流,因此怀疑是A把总线拉低了。

后查看A芯片的固件,发现BC传输数据时,A竟然处于低电平状态!

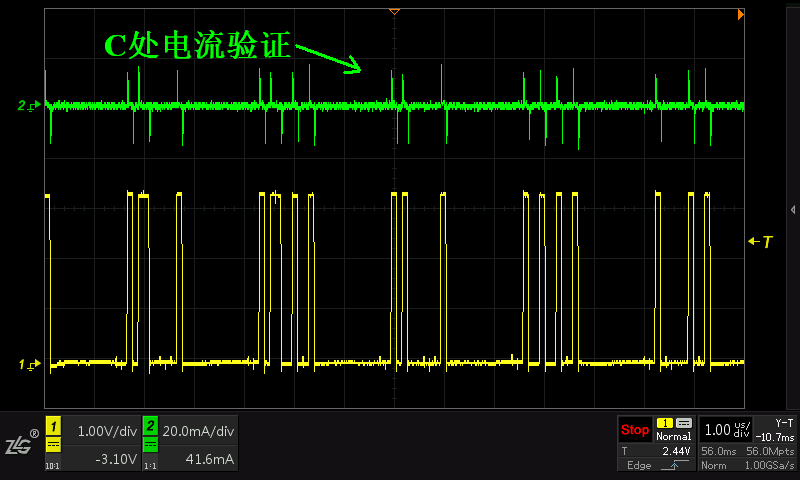

修改为高阻后,1.5V电平恢复到3.3V了,30mA的电流也消失不见,如下图

图9 电流验证

至此,元凶已归案,此案成功告破。

于是,三个芯片又能够愉快的传输数据了

案后语

当初遇到这个问题时,硬件开发说芯片之间采用直连方式,不可能有问题,软件开发查看代码也没有发现什么问题。看似一个无解的问题,显然用常规方式难以解决,电压波形不是万能的,有时候结合电流来看,问题却能迎刃而解,你觉得呢?

|