|

|

ЙПәЈ »Ә¶«КҰ·¶ҙуС§ НЁРЕ№ӨіМПө ma-chao

Т»Ўў»щұҫёЕДо

1Ј®ARM cortex_m3 ДЪәЛЦ§іЦ 256 ёцЦР¶ПЈЁ16 ёцДЪәЛ+240 НвІҝЈ©әНҝЙұаіМ 256 ј¶ЦР¶ПУЕПИј¶өДЙиЦГЈ¬УлЖдПа№ШөДЦР¶ПҝШЦЖәНЦР¶ПУЕПИј¶ҝШЦЖјДҙжЖчЈЁNVICЎўSYSTICK өИЈ©ТІ¶јКфУЪcortex_m3 ДЪәЛөДІҝ·ЦЎЈSTM32 ІЙУГБЛcortex_m3 ДЪәЛЈ¬ЛщТФХвІҝ·ЦИФҫЙұЈБфК№УГЈ¬ө« STM32ІўГ»УРК№УГ cortex_m3 ДЪәЛИ«ІҝөД¶«ОчЈЁИзДЪҙжұЈ»ӨөҘФӘ MPU өИЈ©Ј¬ТтҙЛЛьөД NVIC КЗcortex_m3 ДЪәЛөД NVIC өДЧУјҜЎЈ

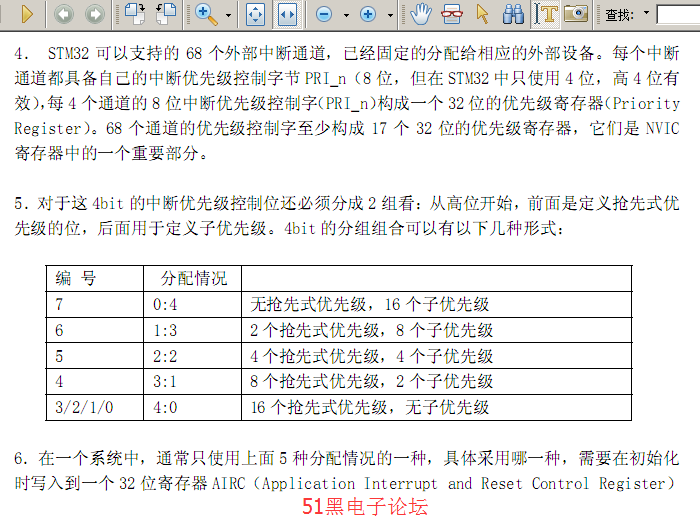

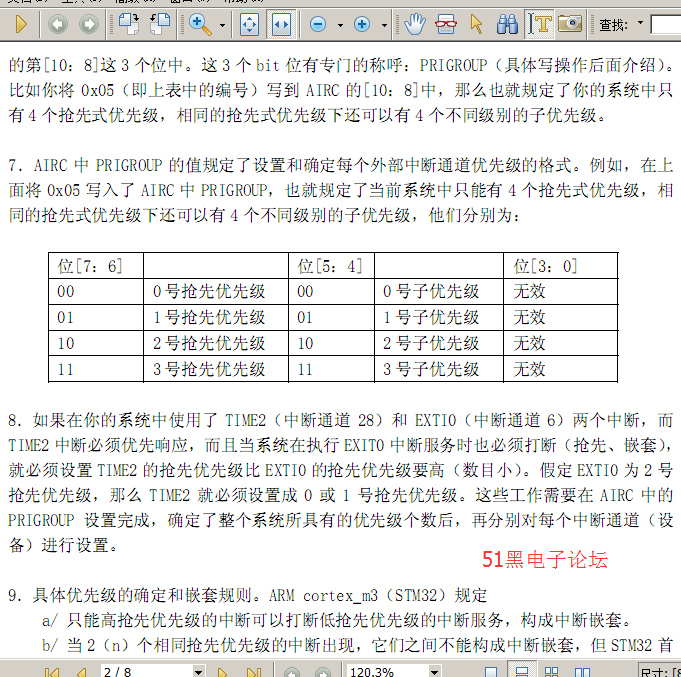

2Ј®STM32 ДҝЗ°Ц§іЦөДЦР¶П№ІОӘ 84 ёцЈЁ16 ёцДЪәЛ+68 ёцНвІҝЈ© Ј¬әН 16 ј¶ҝЙұаіМЦР¶ПУЕПИј¶өДЙиЦГЈЁҪцК№УГЦР¶ПУЕПИј¶ЙиЦГ 8bit ЦРөДёЯ 4 О»Ј¬јыәуГжҪвКНЈ©ЎЈЎ¶ІОҝјЧоРВ 101xx-107xx STM32 Reference manual, RM0008Ў·ЎЈ

3Ј®ТФПВЦчТӘ¶ФЎ°НвІҝЦР¶ПНЁөАЎұҪшРРЛөГчЎЈ

¶ФУЪ cortex_m3 ДЪәЛЛщЦ§іЦөД 240 ёцНвІҝЦР¶ПЈ¬ОТФЪХвАпК№УГБЛЎ°ЦР¶ПНЁөАЎұХвёцёЕДоЈ¬ТтОӘҫЎ№ЬГҝёцЦР¶П¶ФУҰТ»ёцНвО§ЙиұёЈ¬ө«ёГНвО§ЙиұёНЁіЈҫЯұёИфёЙёцҝЙТФТэЖрЦР¶ПөДЦР¶ПФҙ»тЦР¶ПКВјюЎЈ¶шёГЙиұёөДЛщУРөДЦР¶П¶јЦ»ДЬНЁ№эёГЦё¶ЁөДЎ°ЦР¶ПНЁөАЎұПтДЪәЛЙкЗлЦР¶ПЎЈТтҙЛЈ¬ПВГж№ШУЪЦР¶ПУЕПИј¶өДёЕДо¶јКЗХл¶ФЎ°ЦР¶ПНЁөАЎұөДЎЈөұёГЦР¶ПНЁөАөДУЕПИј¶И·¶ЁәуЈ¬ТІҫНИ·¶ЁБЛёГНвО§ЙиұёөДЦР¶ПУЕПИј¶Ј¬ІўЗТёГЙиұёЛщДЬІъЙъөДЛщУРАаРНөДЦР¶ПЈ¬¶јПнУРПаН¬өДНЁөАЦР¶ПУЕПИј¶ЎЈЦБУЪёГЙиұёұҫЙнІъЙъөД¶аёцЦР¶ПөДЦҙРРЛіРтЈ¬ФтИЎҫцУЪУГ»§өДЦР¶П·юОсіМРтЎЈ

НкХыөДpdfёсКҪОДөө51әЪПВФШөШЦ·ЈЁ№І8ТіЈ©Јә

STM32ЦР¶ПУЕПИј¶УлПа№ШК№УГёЕДо.pdf

(139.04 KB, ПВФШҙОКэ: 41)

STM32ЦР¶ПУЕПИј¶УлПа№ШК№УГёЕДо.pdf

(139.04 KB, ПВФШҙОКэ: 41)

|

ЖА·Ц

-

ІйҝҙИ«ІҝЖА·Ц

|

№ЬАнФұQQ:125739409;јјКхҪ»БчQQИә281945664

№ЬАнФұQQ:125739409;јјКхҪ»БчQQИә281945664