应用笔记的内容截图:

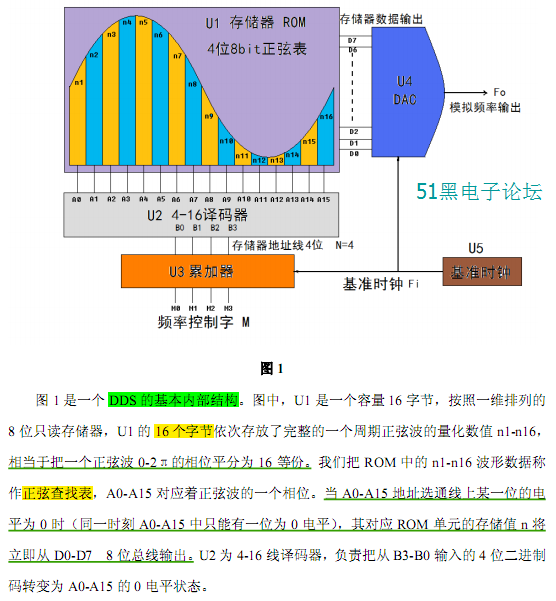

U4 是一个高速数模转换器(DAC) ,他负责把 D0-D7 输入的数字信号变成对应的模拟信号,在基准时钟的驱动下,每个基准时钟周期转换一次。例如最大值 n4 对应模拟输出5V,中间值n8输出2.5V,最小值n12 对应输出0V。

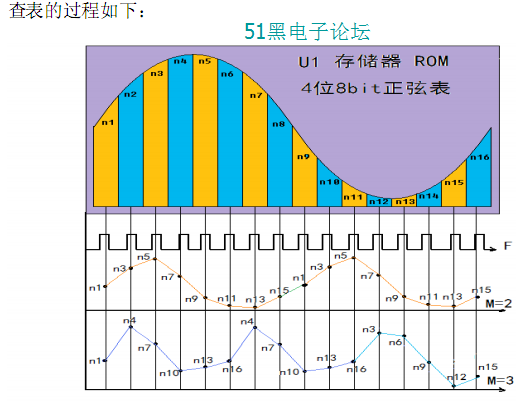

ROM地址总线B0-B3, ROM地址选通线A0-A15 以及ROM数据输出总线D0-D7 的电平状态(逻辑关系)如下表:

U3 为相位累加器,它是DDS的结构中最关键的算法单元。相位累加器有一个时钟输入端,一组频率控制字输入总线M3-M0,一组相位地址输出总线B3-B0。

相位累加器U3 由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲F0,加法器将频率控制字 M 与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。此过程的伪代码表述如下:

If(clock)

B=B+M;

这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看

出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的

数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累

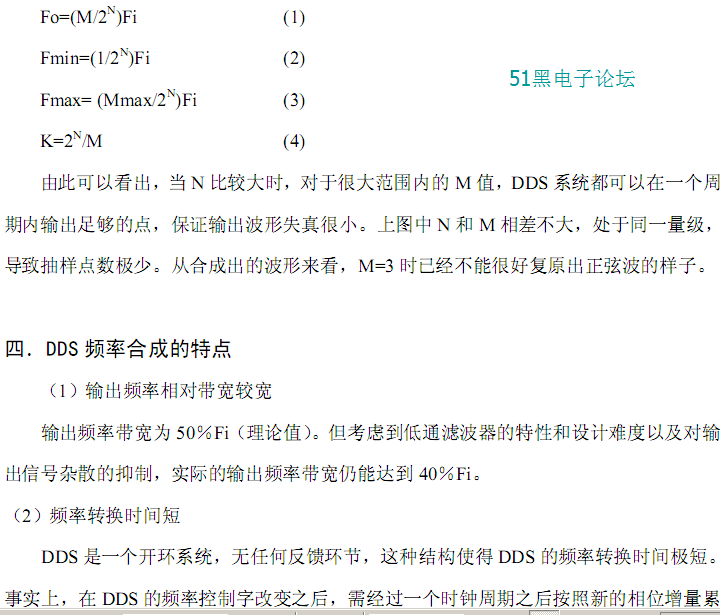

三.DDS 相关计算

由上面的计算规律,我们可以总结出以下几个公式,各符号的定义为:Fi:基准频率;Fo:DDS输出频率;M:频率控制字;N:相位累加器位数;K:DDS每个输出周期的抽样点数;Fmin:DDS最小输出频率(频率分辨率);Fmax:DDS最大输出频率。

完整的pdf格式文档51黑下载地址(共18页):

AD9851_应用笔记.pdf

(3.16 MB, 下载次数: 46)

AD9851_应用笔记.pdf

(3.16 MB, 下载次数: 46)

|