|

|

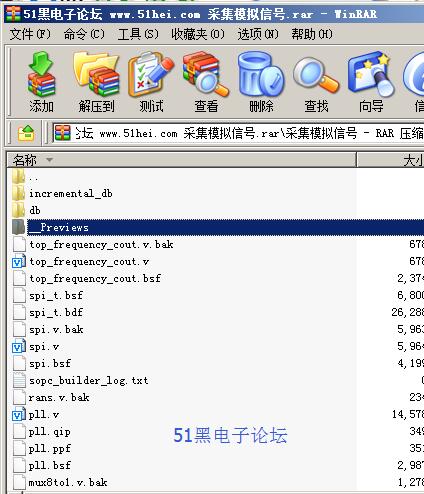

fpgaВЩМЏЪ§ОнВЈаЮЃЌ51ЕЅЦЌЛњЯдЪОВЈаЮЃЌЪОВЈЦї

ЕЅЦЌЛњдДГЬађШчЯТЃЈfrqent_count.vЃЉ:

- /*==============================================

- * Уш Ъі:ЦЕТЪМЦПижЦФЃПщМЦЪ§ВтЪдГЬађ

- //==============================================*/

- module frqent_count(clk_b,clk_d,vavle,rst,cnt_h_out,cnt_b_out,cnt_d_out);

- input rst;

- input clk_b;

- input clk_d;

-

- input vavle;

-

- output reg[31:0] cnt_h_out; //гУгкВтСПИпТіПэ

- output reg[31:0] cnt_b_out; //БъзМЦЕТЪМЦЪ§

- output reg[31:0] cnt_d_out; //Д§ВтЦЕТЪМЦЪ§

-

- reg [31:0] cnt_h; //гУгкВтСПИпТіПэ

- reg [31:0] cnt_b; //БъзМЦЕТЪМЦЪ§

- reg [31:0] cnt_d; //Д§ВтЦЕТЪМЦЪ§

-

- reg start_reg; //ПЊЪМаХКХЛКДц

- reg clk_d_reg; //Д§ВтЪБжгЛКДц

-

- wire start;

-

- /*------------------------------------------------

- * ФЃПщЫЕУї:МЦЪ§дЪаэФЃПщ

- * БИ зЂ:Start_lЖдгкЦЕТЪУЛгазїгУ,жЛЖдгкЕЭЕчЦН

- ТіПэМЦЪ§газїгУ,ЦЕТЪжївЊзїгУдкStart

- *-------------------------------------------------*/

-

- assign start = vavle;

-

-

- //ПЊЪМаХКХЛКДц

- always@(posedge clk_b,negedge rst)

- begin

- if(!rst)

- begin

- start_reg <= 1'b0;

- end

-

- else

- begin

- start_reg <= start;

- end

- end

-

- //Д§ВтаХКХЛКДц

- always@(posedge clk_b, negedge rst)

- begin

- if(!rst)

- begin

- clk_d_reg <= 1'b0;

- end

-

- else

- begin

- clk_d_reg <= clk_d;

- end

- end

-

- //Д§ВтЪБжгНјааМЦЪ§

- always@(posedge clk_d,negedge rst)

- begin

- if(!rst)

- begin

- cnt_d <= 32'b0;

- end

-

- else

- begin

- if(start == 0)

- begin

- cnt_d <= 0;

- end

- // ИпЕчЦНДЅЗЂ

- else

- begin

- cnt_d <= cnt_d + 1'b1;

- end

- end

- end

-

- //БъзМЪБжгНјааМЦЪ§

- always@(posedge clk_b,negedge rst)

- begin

- if(!rst)

- begin

- cnt_b <= 0;

- end

-

- else

- begin

- if(start == 0)

- begin

- cnt_b <= 0;

- end

-

- else

- begin

- cnt_b <= cnt_b + 1'b1;

- end

- end

- end

-

- //ИпЕчЦНМЦЪ§

- always@(posedge clk_b, negedge rst)

- begin

- if(!rst)

- begin

- cnt_h <= 0;

- end

-

- else

- begin

- if(clk_d == 0)

- begin

- cnt_h <= 0;

- end

-

- else

- begin

- cnt_h <= cnt_h + 1'b1;

- end

- end

- end

-

- //БъзММЦЪ§КЭД§ВтМЦЪ§ЪфГі

- always@(posedge clk_b, negedge rst)

- begin

- if(!rst)

- begin

- cnt_b_out <= 0;

- cnt_b_out <= 0;

- end

-

- else

- begin

- if(start_reg && !start)

- begin

- cnt_b_out <= cnt_b;

- cnt_d_out <= cnt_d;

- end

-

- else

- begin

- cnt_b_out <= cnt_b_out;

- cnt_d_out <= cnt_d_out;

- end

- end

- end

-

- //ИпЕчЦНМЦЪ§ЪфГі

- always@(posedge clk_b,negedge rst)

- begin

- if(!rst)

- begin

- cnt_h_out<=0;

- end

-

- else

- begin

- if(clk_d_reg&&!clk_d)

- begin

- cnt_h_out<=cnt_h;

- end

-

- else

- begin

- cnt_h_out<=cnt_h_out;

- end

- end

- end

-

- endmodule

-

ЫљгазЪСЯ51heiЬсЙЉЯТди:

ВЩМЏФЃФтаХКХ.rar

(2.39 MB, ЯТдиДЮЪ§: 51)

ВЩМЏФЃФтаХКХ.rar

(2.39 MB, ЯТдиДЮЪ§: 51)

|

|

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664