|

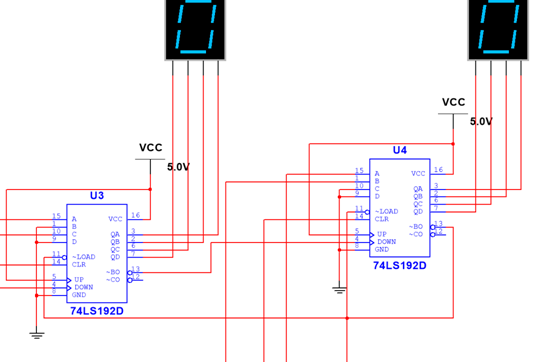

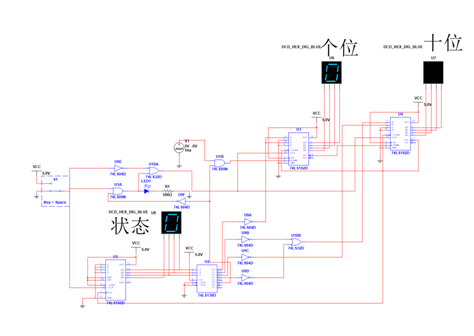

要求分析 根据任务要求,使用逻辑门电路设计一款电饭煲,主要目的: 1. 设计一款倒计时电路,最高支持倒计时20分钟。 2. 设计一款计数器电路,最高支持4~6种不同状态。 3. 支持根据不同状态,设置不同倒计时参数。 二 问题分析根据项目分析可以确定该设计可以通过:信号源、减法电路、加法电路、以及相关逻辑门电路几个部分构成。 由于项目中最小时间单位是分钟,所以选用每一个时钟代表一分钟进行实验。基本设计思路如下图所示: 图2.1 整体设计思路 三 设计过程3.1 倒计时设置逻辑因为在初始上电状态下,芯片处于不稳定状态,所以状态标识如下所示: 0:启动;1:预加热5分钟; 2: 吸水10分钟3:加热煮饭20分钟;4:焖饭10分钟;5:保温并提示; 根据以上状态以及要求,列出需要设定的倒计时的真值表如下所示: 表3.1 倒计时时间真值表 由于存在单独状体的情况且状态的二进制表示不超过3bit,使用74LS138译码器能极大的减小设计难度。 根据上表,设个位十位的由低到高分别为A1、B1、C1、D1、A1、B1、C1、D1,74LS138的输出分别为Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7则可以得出以下关系: A1= C1=Y0’ A2= Y1’ +Y3’ B2=Y2’ 图3.1 倒计时时间设置逻辑 3.2 CLR信号处理根据74LS192和74LS160的手册,对CLR信号进行分析。使用单刀双掷开关作为电饭煲开关,开关置于VCC是,认为启动,为数字逻辑1,反之置于GND则为0。开关S1=0时,所有芯片清零,S1=1时,所有倒计时结束后74LS160不置零,74LS192置零并且CLK无输入。所以74LS192的CLR取决于S1状态、和Y5的状态如下表。根据分析得出CLR=Y5’S1+S1’。 表3.2 74LS192CLR引脚逻辑真值表 图3.2 74LS192CLR引脚逻辑电路图 3.3 CLK信号处理根据芯片手册可知74LS160的CLK输入可以从74LS192的~BO引脚获取,并且个位的~BO引脚可以作为十位的74LS192CLK信号。减发器将使用异步方式递减,个位的倒计时解释后从十位借位,如果十位为0,则~BO引脚将输出一个低电平。该低电平可作为74LS160的状态转化CLK输入。根据以上分析可知个位的74LS194CLK还需要满足S1=1时, 74LS192CLK无输入,即在Y5=0时,CLK没有输入。将个位和十位的74LS194的CLK信号分别命名为CLK1,CLK2则CLK1真值表如下: 表3.3 CLK真值表 由此得出:CLK1= Y5CLK。电路图如下所示: 图3.3 个位74LS192CLK逻辑电路图 3.4 LOAD信号处理因为默认情况下74LS192的置数是0,根据芯片时序图可知,初始状态下即可获取一个借位信号,所以在初始状态下十位的74LS192接收到个位的借位信号时,同样需要借位,所以可以将十位的借位信号作为两片74LS192的LOAD信号。

图3.4 74LS192LOAD信号逻辑电路图 74LS160由于通过CLR清零,并不需要LOAD处理,所以为保证稳定性,74LS160的LOAD信号接地。 3.5 显示部分与报警信号显示使用BCD八段数码管做显示,报警信号时在S1=1并且Y5=0时,逻辑为1,所以报警信号等于Y5’S1。 图3.5 报警信号逻辑电路图 四 仿真结果

图4.1 整体电路图上电时,若S1状态为0,则所有芯片清零,无显示。若S1为1,则74LS160的CLK被74LS192的借位触发,74LS160显示状态1,74LS192同时被置位显示05,CLK开始倒计时。然后倒计时结束,74LS192借位,74ls160显示状态2,74LS192同时被置位显示10,然后倒计时结束,74LS192借位,74ls160显示状态3,74LS192同时被置位显示20,然后倒计时结束,74LS192借位,74ls160显示状态4,74LS192同时被置位显示10,然后倒计时结束,74LS192借位,74ls160显示状态5,74LS192同时被清零,CLK输入被置低,显示00,发光二极管被点亮。在该过程中任意时刻将S1置0,所有芯片立刻清零,系统复位,所有数码管显示0,S1重新置1后恢复以上步骤。

Multisim仿真工程文件和word下载:

电饭煲.rar

(516.49 KB, 下载次数: 0)

电饭煲.rar

(516.49 KB, 下载次数: 0)

|