//顶层

module timer_top(

input clk_12M,//12Mhz时钟

input reset,//复位

input stop,//暂停

output [1:0]wela,//位选

output [7:0]dula1,//第一个数码管段选

output [7:0]dula2//第二个数码管段选

);

wire [7:0]sec;

time_cnt u1(

.clk_12M(clk_12M),

.reset(reset),

.stop(stop),

.sec(sec)

);//例化分频计数模块

display u2(

.clk_12M(clk_12M),

.sec(sec),

.wela(wela),

.dula1(dula1),

.dula2(dula2)

);//例化显示模块

endmodule

//分频计数

module time_cnt(

input clk_12M,

input reset,

input stop,

output [7:0] sec

);

/*12M时钟分频1s 计数6M次*/

reg [23:0]cnt;

reg clk_1s;

always @(posedge clk_12M or negedge stop)

begin

if(!stop)//暂停信号为0时有效

begin

cnt <= 0;

end//停止信号有效时,暂停

else if(cnt == 24'h5b8d80)//计数为5999999

begin

clk_1s <= ~clk_1s;

cnt <= 0;

end

else

begin

cnt <= cnt+1;

clk_1s <= clk_1s;

end//暂停信号无效时继续计时

end

/*用于产生1s的秒表计数*/

reg [7:0]sec_reg=0;

always @(posedge clk_1s or negedge reset)

begin

if(!reset)//复位信号为0时有效

begin

sec_reg <= 0;//复位信号有效时置0

end

else if(sec_reg[3:0] == 4'd9)//秒个位计数到9

begin

if(sec_reg[7:4] == 4'd5)//秒十位计数到5

begin

sec_reg <= 0;//清0

end

else

begin

sec_reg[7:4] <= sec_reg[7:4] + 1;//秒十位加1

sec_reg[3:0] <= 0;//秒个位清零

end

end

else

begin

sec_reg[3:0] <= sec_reg[3:0] + 1;

end

end

assign sec = sec_reg;

endmodule

//显示

module display(

input clk_12M,

input [7:0]sec,

output reg [1:0]wela=0,

output reg [7:0]dula1=0,

output reg [7:0]dula2=0

);

/*数码管需要动态扫描,所以产生一个1ms的时钟*/

reg [12:0]cnt;

reg clk_1ms;

always @(posedge clk_12M)

begin

if(cnt == 13'h1770)

begin

cnt <= 0;

clk_1ms <= ~clk_1ms;

end

else

begin

cnt <= cnt + 1;

clk_1ms <= clk_1ms;

end

end

reg state;

reg [3:0]sec_reg1;

reg [3:0]sec_reg2;

always @(posedge clk_1ms)

case(state)//位选

0:begin

wela<=2'b01;state<=1;sec_reg2 <= sec[3:0];

end

1:begin

wela<=2'b10;state<=0;sec_reg1 <= sec[7:4];

end

endcase

always @(posedge clk_12M)

begin

case(sec_reg1)

0:dula1 <= 8'h3f;

1:dula1 <= 8'h06;

2:dula1 <= 8'h5b;

3:dula1 <= 8'h4f;

4:dula1 <= 8'h66;

5:dula1 <= 8'h6d;

6:dula1 <= 8'h7d;

7:dula1 <= 8'h07;

8:dula1 <= 8'h7f;

9:dula1 <= 8'h6f;

endcase

end//第一个数码管段选0~9

always @(posedge clk_12M)

begin

case(sec_reg2)

0:dula2 <= 8'h3f;

1:dula2 <= 8'h06;

2:dula2 <= 8'h5b;

3:dula2 <= 8'h4f;

4:dula2 <= 8'h66;

5:dula2 <= 8'h6d;

6:dula2 <= 8'h7d;

7:dula2 <= 8'h07;

8:dula2 <= 8'h7f;

9:dula2 <= 8'h6f;

endcase

end//第二个数码管段选0~9

endmodule

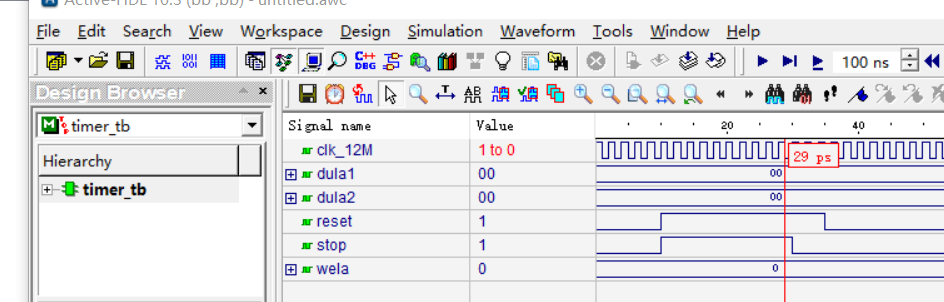

//测试文件

module timer_tb();

reg clk_12M;

reg stop;

reg reset;

wire [7:0]dula1;

wire [7:0]dula2;

wire [1:0]wela;

timer_top u1(

.clk_12M(clk_12M),

.stop(stop),

.reset(reset),

.dula1(dula1),

.dula2(dula2),

.wela(wela)

);

initial

begin

clk_12M=1;

reset=0;

stop=0;

#10 reset=1;stop=1;

#20 stop=0;

#5 reset=0;

#20 $stop;

end

always #1 clk_12M=~clk_12M;

endmodule

全部资料51hei下载地址:

timer.zip

(677.37 KB, 下载次数: 31)

timer.zip

(677.37 KB, 下载次数: 31)

|