原谅我记忆力不好。。。花了好久弄明白的东西才十个小时不到就忘记了,所以趁现在记得赶紧记录下来。本文内容:重建de1-soc中HPS-FPGA工程。

PS:原工程在http://pan.baidu.com/s/1gdkoniN,我用的是lab\SW\de1_soc_lab3_hardware和de1_soc_sw_lab3。最后的结果应该是流水灯,60次。

打开Quartus ii 软件,新建工程Qsystrying,选择5CSEMA5F31C6,新建verilog HDL文件Qsys.v,文件内容copy de1_soc_traning\lab\SW\de1_soc_lab3_hardware\ghrd_top.v文件内容,注意模块名改为Qsys,实例化处soc_system改为sys。ghrd.v中只有一个模块,一次模块实例化(注意原模块实例化名字是soc_system,w我的Qsys系统名是sys)

建立Qsys系统sys.qsys。

1,注意先copy de1_soc_traning\lab\SW\de1_soc_lab3_hardware\ip文件夹到Qsys工程下。ip文件夹中是四个ip核,建立Qsys系统中除Quartus自带ip核外还应添加其他需要的ip核,可以自己写,也可以从网上下载。

2,Quartus软件下tools->Qsys或者直接快捷键,依次添加所需模块并连线,最后generate产生相应的文件。注意设置每一个模块的参数(这里面的东西好多,我自己也不完全懂)。如果只是熟悉整个过程,可以直接copyde1_soc_traning\lab\SW\de1_soc_lab3_hardware\soc_system.qsys文件,文件名改成sys.qsys,同样需要Quartus软件下tools->Qsys,打开后generate产生与qsys同名的文件夹(这里是sys文件夹)及其他文件。产生的文件中需要特别注意的是.sopcinfo文件、sys\synthesis\sys.qip、sys\synthesis\sys.v(Qsys.v文件中实例化的sys模块原型就在这个sys.v中),sys\synthesis\submodules\hps_sdram_p0_pin_assignments.tcl文件。

3,执行hps_sdram_p0_pin_assignments.tcl文件。Quartus->tools->Tclscripts,run hps_sdram_p0_pin_assignments.tcl文件。

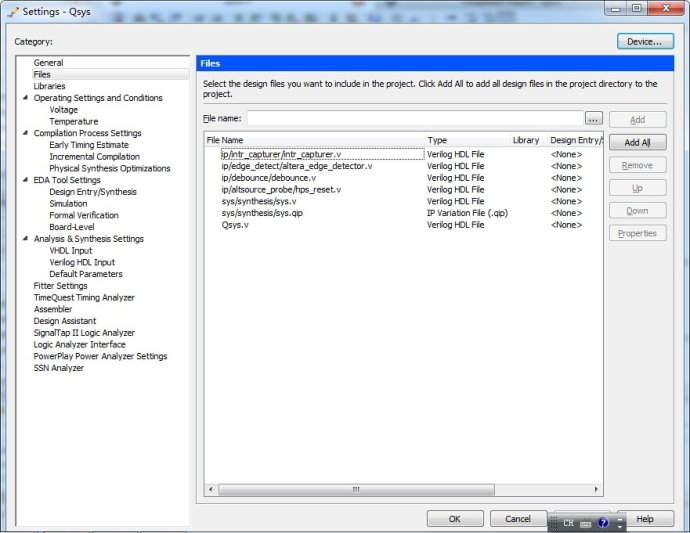

4,添加相应的文件,具体如图:(其实就是用到的ip核的.v文件和Qsys系统生成的.v和.qip文件)

5,分析和综合

6,执行引脚分配.tcl脚本文件,或者自己用pin planner分配引脚。这里如果只是熟悉过程就直接从原项目

de1_soc_lab3_hardware中的工程导出别人的引脚分配的TCL文件。具体方法是:打开工程后,Assignment->pinplanner,file ->export,选择文件类型tcl,名字改为Qsystrying(其他名字也可以)。复制该文件到我们的Qsystrying工程目录。回到Qsys工程的Quartus界面,同样执行Qsystrying.tcl文件,就会发现引脚分配好了。

7,Compile Design。之后就是下载到FPGA的板子上。此时看到所有的LED灯都亮。

以上这些仅仅是搭建Qsys系统,FPGA和HPS在Qsys系统上连接,工程文件仅仅是指定各个输入输出口和引脚分配。真正功能的实现是在HPS中的ARM 上跑的程序,具体的就在.c文件中了。

1,产生HPS头文件。具体是利用C:\altera\13.1\embedded的Embedded_Command_Shell.bat运行generate_hps_qsys_header.sh脚本文件(该脚本文件在de1_soc_traning\lab\SW\de1_soc_lab3_hardware中,注意把soc_system.sopcinfo改为自己的.sopcinfo文件,这里是sys.sopcinfo)。

2,生成可执行文件。新建或者直接复制de1_soc_traning\lab\SW\de1_soc_sw_lab3中的main.c文件,可以打开看看文件内容就是跑马灯程序,里面值得注意的是FPGA上地址映射到HPS中的地方,其他的比较容易理解。新建或者直接复制de1_soc_traning\lab\SW\de1_soc_sw_lab3中的Makefile文件,把Makefile,main.c,hps_0.h文件放在一个目录下。用C:\altera\13.1\embedded的Embedded_Command_Shell.bat,make一下产生my_first_hps-fpga文件。

3,利用U盘或以太网方式copy my_first_hps-fpga文件到SD卡,putty连接,运行my_first_hps-fpga。此时看到流水灯。

总结:

自己要做的--------FPGA这块:ip核,Quartus Qsys系统,工程.v文件,分配引脚的tcl文件

----------HPS 这块:Makefile,main.c,generate_hps_qsys_header.sh

最后需要的---------.sof文件下载进FPGA,可执行文件进SD卡中执行

拓展:自启动。

FPGA:.pof文件固化到FPGA中,注意我们的de1-soc用的不是EPCS,而是EPCQ,具体方式见用户手册倒数第二章。

HPS:在/etc/rcS.d中添加需要自动执行的shell文件。这里可以新建shell文件,用shell文件执行我们的my_first_hps-fpga可执行文件。

之后再上电就会自启动流水灯了。

|