|

|

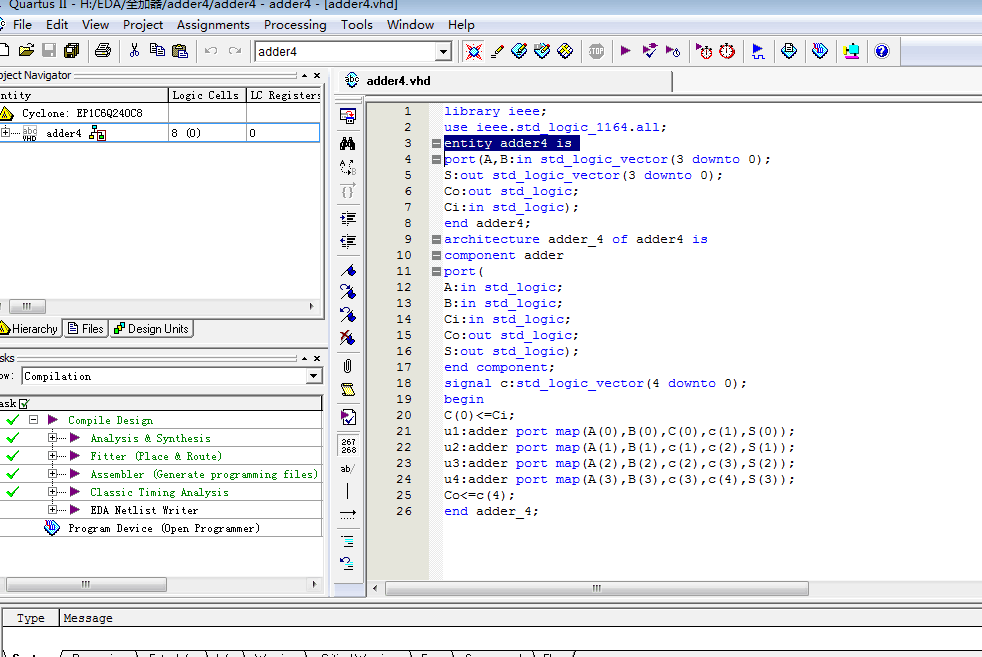

library ieee;

use ieee.std_logic_1164.all;

entity adder4 is

port(A,B:in std_logic_vector(3 downto 0);

S:out std_logic_vector(3 downto 0);

Co:out std_logic;

Ci:in std_logic);

end adder4;

architecture adder_4 of adder4 is

component adder

port(

A:in std_logic;

B:in std_logic;

Ci:in std_logic;

Co:out std_logic;

S:out std_logic);

end component;

signal c:std_logic_vector(4 downto 0);

begin

C(0)<=Ci;

u1:adder port map(A(0),B(0),C(0),c(1),S(0));

u2:adder port map(A(1),B(1),c(1),c(2),S(1));

u3:adder port map(A(2),B(2),c(2),c(3),S(2));

u4:adder port map(A(3),B(3),c(3),c(4),S(3));

Co<=c(4);

end adder_4;

注:本程序是有一位全加器生成的四位全加器,注意一定要把一位全加器的顶成层文件放到四位全加器的根目录下,否则一定会报错,一位,四位全加器的程序在附件中。

|

-

图片附上

-

-

全加器.zip

343.83 KB, 下载次数: 24, 下载积分: 黑币 -5

工程文件附上

评分

-

查看全部评分

|