|

课程设计报告

课程:EDA技术基础 题目:频率计的设计学生

姓名:李*学号:201556110210

班级:1502班

专业:电子信息科学与技术

指导教师:贺*

长沙理工大学课程设计任务书 物理与电子科学 学院 电子信息科学与技术 专业 1502 班 姓名 李* 课程名称 EDA技术基础 题 目 频率计的设计 | 用FPGA设计一个频率计,测量TTL电平方波信号的频率。具体要求如下: (1)测量频率范围: 10Hz~100kHz (2)数字显示,全测量范围精度:2 % (3)测量速度不低于每秒8次 (4)量程选择:拨码开关或键控 (5)自行设计简易方波信号发生器,测试验证频率计性能 发挥部分: (1)自动量程(2)提高精度(3)拓宽量程(4)等精度方案(5)周期测量(6)上电自检或键控自检。

工作计划 (1)时间 本课程设计安排2周时间: 2017.12.18 ~2017.12.29 (2)进度安排 第1周周一周二:查阅资料,拿出整体设计方案,划分模块; 第1周周三至周五:各模块的设计、调试、验证。 第2周周三前完成项目整体调试和测试。 第2周周三周四文档写作整理 第2周周五:答辩讨论

| 指导教师:

贺慧勇 钟海丽 唐立军 文勇军 周晓萍

2017年11月8 日 | |

|

长沙理工大学课程设计成绩评定表

学生姓名: 李* 学号: 201556110210 专业班级: 电子信息科学与技术 1502班 课程设计题目: 频率计设计

| | | | | | | |

| | | |

| | | |

| | 完全符合撰写规范要求,结构严谨,逻辑性强,层次清晰,表述准确,文字流畅。 | |

| | | |

| |

| |

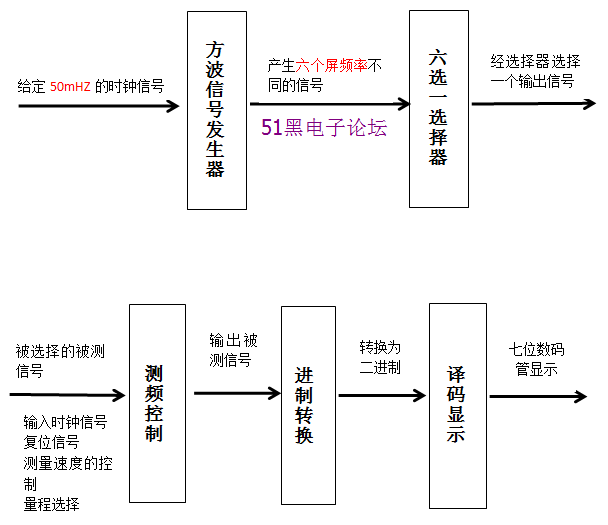

摘要 所谓频率就是某信号在时间T内的变化次数N,公式:F=N/T。本次频率计的设计的基本原理是:用一个频率稳定度高的频率源作为基准时钟,对比测量待测信号的频率。通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1秒。闸门时间可以根据需要取值,闸门时间越长,的得到的频率值就越准确,但时间间隔会相对较长,闸门时间越短,频率值显示速度就会越快,但精度会因此受到影响,所以一般情况下设计频率计以1s作为闸门时间。基本的测量原理是,首先让被测信号与标准信号一起通过一个闸门,然后用计数器计数信号脉冲的个数,把标准时间内的计数结果用锁存器锁存起来,最后用显示译码器,把锁存的结果用LED数码显示管显示出来。 目录 一、综合概述 5 1、EDA技术及频率计概述 5 2、使用设计软件及工具 6 二、模块设计 8 1、信号产生及六选一选择器 9 2、测频控制模块 9 3、进制转换模块 10 2、译码显示模块 10 2、顶层设计模块 11 2、本人负责模块 13 三、设计要求的实现及问题的发现 14 四、总结 16 参考文献及附录 1、EDA及频率计概述 (1)、EDA技术概述:在计算机技术的推动下,20世纪末,电子技术获得了飞速的发展,现代电子产品渗透于社会的各个领域,有力的推动了社会生产力的发展和社会信息化程度的提高,同时有促使现代电子产品性能的进一步提高,产品更新换代的节奏也越开越快。EDA(electronic design automation)技术作为现代电子技术设计的核心,它依赖功能强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL(hardware description language)为系统逻辑描述手段完成设计文件,自动地完成逻辑简化,逻辑分割,逻辑综合,结构综合(布局布线),以及逻辑优化和仿真测试等功能,直至实现既定性能的电子系统功能。EDA技术使得设计者的工作几乎仅限于利用软件的方式,即利用硬件描述语言HDL和EDA软件来完成对系统硬件功能的实现。 (2)、频率计研究与应用:频率计已经广泛应用于高科技产品行业的生产之中,到今天频率计已开始向智能、精细方向发展,因此系统对电路的要求越来越高,传统的集成电路设计技术已经无法满足性能日益提高的系统要求。在信息技术高度发展的今天,电子系统数字化已成为有目共睹的趋势。从传统应用中小规模芯片构成系统到广泛应用单片机,直到今天FPGA/CPLD在系统设计中的应用,电子技术已迈入一个全新的阶段。而在电子技术中,频率是最基本的参数之一,而信号的频率往往与测量方案的制定、测量结果都有着十分密切的关系,所以测频率方法的研究越来越受到重视。 (3)、基本设计原理及测量方法:用一个频率稳定度高的频率源作为基准时钟,对比测量待测信号的频率。通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1秒。闸门时间可以根据需要取值,闸门时间越长,的得到的频率值就越准确,但时间间隔会相对较长,闸门时间越短,频率值显示速度就会越快,但精度会因此受到影响,所以一般情况下设计频率计以1s作为闸门时间。基本的测量原理是,首先让被测信号与标准信号一起通过一个闸门,然后用计数器计数信号脉冲的个数,把标准时间内的计数结果用锁存器锁存起来,最后用显示译码器,把锁存的结果用LED数码显示管显示出来。 对于quaturs Ⅱ软件的基本描述:QuartusII是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(AlteraHardwareDescriptionLanguage)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程.Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;芯片(电路)平面布局连线编辑;LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;功能强大的逻辑综合工具;完备的电路功能仿真与时序逻辑仿真工具;定时/时序分析与关键路径延时分析;可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;支持 软件 源文件的添加和创建,并将它们链接起来生成编程文件;使用组合 编译方式可一次完成整体设计流程;自动定位编译错误;高效的期间编程与验证工具;可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件;能生成第三方EDA 软件使用的VHDL网表文件和Verilog网表文件。 二、模块设计 根据前一章的叙述,频率计的工作流程基本是:由信号源发出周期信号——待测信号,通过由测频控制电路提供的基准测频信号即闸门信号,然后在单位时间内由计数器来计经由闸门的信号脉冲个数,计数器将所计个数交由锁存器进行存储,经过测频控制电路提供的使能信号,锁存器再将信号转送给译码器进行进制转换,最后在经过数码显示管将所测得频率值显示出来。所以,在设计频率计的工作中大概可以将设计模块分为五个模块即(设计原理图如下)1、信号发生模块;2、测频控制模块;3、计数器模块;4、锁存模块;5、译码及显示模块,各个模块完成后再经过顶层设计将其连接,最后再做整体调试、运行、改正。

该模块的设计是独立于频率计设计的,为得是从外部产生被测信号以检测频率计的测量精度,同时也证明所设计的频率计可以测量任何从外部 (1)信号发生器设计的过程是利用分频器将50mHz的时钟信号分为6个频率不同的信号分别是10Hz、100Hz、1000Hz、500Hz、10kHz、100kHz如下程序所示,分频器的是基于计数原理所设计的,当计数小于250时继续累加,直至下一个上升沿500时输出一个分频信号作为第一个被测信号其频率为100kHz,余下的五个信号也由此程序产生。 variable cnt1,cnt2,cnt3,cnt4,cnt5,cnt6 :INTEGER RANGE 0 TO 5000000; begin if clk'event and clk='1' then if cnt1<250 then cnt1:=cnt1+1; else a<=not a; cnt1:=0; end if; - 为方便测试,上述产生的六个信号需要控制着每次只输出一个给频率计测量,因此需要设计一个简单的选择,通过拨码开关控制每次输出的信号。部分程序如下

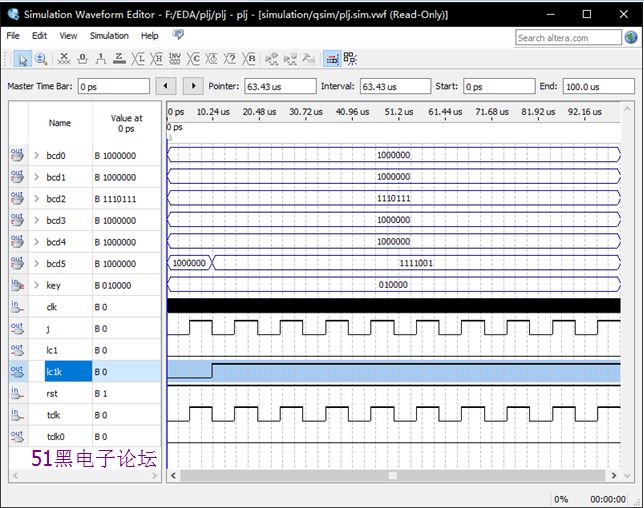

xuanze:process(key) ----选择方波 begin case(key) is when "10000" => tclk0<=e; when "01000" => tclk0<=d; tclk0是输出信号,e、d为输入信号,当拨码开关所示数值为“10000”时,输出信号为e,以此类推,完成对六个信号的选择。 测频控制模块是频率计的核心模块,其功能是计数所测信号在一秒钟内的脉冲数;计算测量速度;量程的自动切换控制等。部分程序如下: port(clk:in std_logic; --输入时钟50mHz tclk:in std_logic; rst : in std_logic; x : out integer range 0 to 500000000; j,lc1,lc1k: out std_logic); end z; architecture hav of z is signal a :std_logic ; SIGNAL cnt0:INTEGER RANGE 0 TO 5000000; begin cepin:process(clk,tclk) begin if rst='0' then cnt0<=0;x<=0;j<='0'; else j<=tclk; if clk'event and clk='1' then if tclk='1' then cnt0<=cnt0+1; else if cnt0>24999 then x<=(250000000/cnt0*10);lc1<='1';lc1k<='0'; cnt0<=0; elsif cnt0/=0 and cnt0<25000 then x<=2500000/cnt0;lc1<='0';lc1k<='1'; cnt0<=0; 其中,x为所测信号的计数值,rst为复位信号,j为测量速度,lc1、lc1k为两个档位的量程。设计过程中,将j信号的输出用LED灯显示,以其闪烁速度作为每次测量时的测量速度;在量程选择中,共有两个单位的量程,当被测信号的频率值小于1000Hz时,单位为Hz,当被测信号频率高于1000Hz时,量程自动切换,单位变为kHz。 进制转换模块的任务是将十进制脉冲数,转换为四进制BCD码。算法如下: variable b1,b2,b3,b4,b5:INTEGER RANGE 0 TO 500000000; begin b1:=X rem 10; b2:=((X-b1) rem 100)/10; b3:=((X-b1-10*b2) rem 1000)/100; ----------------------------------------------- A1<=CONV_STD_LOGIC_VECTOR(b1,4); A2<=CONV_STD_LOGIC_VECTOR(b2,4); X作为输入信号,A1、A2为输出信号。 将BCD码用七位数码管显示出来。部分程序如下: case (A1) is WHEN"0000" => BCD0(6 DOWNTO 0)<="1000000"; --0 WHEN"0001" => BCD0(6 DOWNTO 0)<="1111001"; --1 WHEN"0010" => BCD0(6 DOWNTO 0)<="0100100"; --2 WHEN"0011" => BCD0(6 DOWNTO 0)<="0110000"; --3 WHEN"0100" => BCD0(6 DOWNTO 0)<="0011001"; --4 WHEN"0101" => BCD0(6 DOWNTO 0)<="0010010"; --5 WHEN"0110" => BCD0(6 DOWNTO 0)<="0000010"; --6 WHEN"0111" => BCD0(6 DOWNTO 0)<="1111000"; --7 WHEN"1000" => BCD0(6 DOWNTO 0)<="0000000"; --8 WHEN"1001" => BCD0(6 DOWNTO 0)<="0010000"; --9 WHEN OTHERS => BCD0(6 DOWNTO 0)<="1111111"; bcd2(6 downto 0)<="1111111"; end case; 其中输出信号为bcd0,输入信号为A1. 顶层设计是个模块的综合,首先先将各模块的文件放在顶层设计的文件中方便调用,然后用例化语句将个模块的端口定义并连接。部分程序如下: component cepin port(clk,tclk,rst:in std_logic; x : out integer range 0 to 500000000; j,lc1,lc1k: out std_logic); end component; component yima port (x : in integer range 0 to 500000000; bcd0,bcd1,bcd2,bcd3,bcd4,bcd5:out std_logic_vector(6 downto 0)); end component; ---------------------------------------------------------------------------------------------------------- u1:cepin port map(clk=>clk,x=>f,tclk=>tclk,j=>j,rst=>rst,lc1=>lc1,lc1k=>lc1k); u2:yima port map(x=>f,bcd0=>bcd0,bcd1=>bcd1,bcd2=>bcd2,bcd3=>bcd3,bcd4=>bcd4,bcd5=>bcd5); end hav; 上述程序是顶层设计中对测评控制和译码显示模块的调用及两个模块的端口连接。顶层设计的仿真图如下:

由仿真结果可以看出,当拨码开关拨至“010000”时,频率计所测量的得输出信号如“lc1k”所示,随后由译码显示模块,将其转换为bcd码,其中bcd2所表示的是小数点的位置,bcd0,bcd1分别表示所保留的两位小数点。Lc1,lc1k分别表示单位为Hz和kHz两个单位的量程,从图中可以看出拨码开关拨至“010000”时所用量程的单位是kHz。

6、本人负责模块。

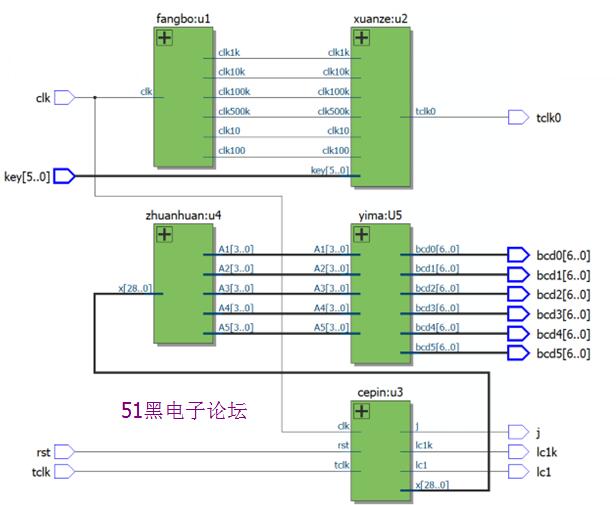

此次设计,我负责的是顶层设计,在组内的任务相对来说是最轻松的。顶层设计就是将组员设计的各个模块通过COMPONENT语句实现调用,再用端口映射语句PORT MAP语句将各个模块连接起来形成一个完整的电路。设计过程参照《EDA技术实用教程》中全加器顶层设计的过程来完成。原理图如下:

在该模块的设计中,要注意的问题就是各个模块可能会用到的重复的端口名称,其次就是要有一个明确的引脚分配思路,之后在开发板上运行时,集中可辨的按键可以减少操作难度,更加方便演示。

三、设计要求的实现及问题的发现

1、 由上一节中顶层设计的原理图可以看到,信号的发生和选择是完全独立的,所以该频率计还可以测量任何外部接入信号的频率。

2、 精度的计算:

3、本次设计的问题在于量程的选择问题上,在被测信号低于1000Hz时量程的单位为Hz,大于1000时单位为kHz,因此无法确认1000Hz时的量程应该怎样划分。

四、总结

短短两周的课程设计,让大家都获益良多。从一开始的被迫学习到后来慢慢主动的去查阅资料,整理思路,讨论问题,到最后大家一起主动解决问题,这一过程不仅是知识的增长更多的认识到团队合作的重要性。

像EDA,单片机这样的课程对于我来说仿佛是天书一样。在做实验的时候也是尽可能的去网上复制粘贴程序,没有投入一点点自己的思考在里面。上课的时候,尽管老师在讲台上讲的生龙活虎,但我整堂课就是左耳进右耳出,虽然有时候觉得应该积累一些知识,以免最后什么也没有学到,但当静心开始听课时,总会有那么一些专业术语卡在脑子,就像是编译过程中遇到了错误而怎么也找不到解决方法一般。

这两周的课程设计对我来说并不轻松,在与组员的讨论讨论过程中更是暴露自己在这门课程上的无知。模块划分的事情也是讨论一遍又一遍,第一个星期过后,看得出大家都有了些倦怠,但当第一次大家都做好各个模块时,我确实是长舒了一口气,殊不知,问题的出现才是从这会开始,在做整合的时候,我们发现各个人做的模块在很大程度上互相不匹配,但是讨论解决方案时又无从下手,最后大家都变得有些心烦意乱。

当今时代是信息技术高速发展的时代,各种信息产业及电子产品充斥着整个世界,推动着信息时代的前进,作为学习信息学科的学生来说,更是承担着未来信息技术发展的重任,《EDA技术基础》作为信息技术的主要学科,对于信息类学生来说更是重要。既然作为重要学科,所以学习难度也不会很轻松,虽然是基础知识但涵盖的知识也是相当全面,在一学期的学习过程中,觉得很多的知识都没有办法了解和运用,在课程设计之前大家都战战兢兢,不知道会抽到什么课题,也不知道最后能不能做出来,但两个星期的设计过程中,随着一个个问题的出现,大家的情绪也跟着起起伏伏,但经过组员的讨论和建议,一个个的问题又慢慢的被解决,直到最后在大家的一起努力之下完成设计。整个过程中,体现出了团队合作的重要性。

在学习了EDA技术的基础便开始做设计对于我们大多数普通学生来说都是不容易的,在讨论设计方案的时候都尽量的挑选最简单的过程进行设计,而最后设计出来的成果又存在很多的问题。在我们本次的设计中,我们直接将发挥部分的一个选项加入了设计过程,在量程选择问题上我们直接设计成了自动量程,在测频控制模块的设计中也存在不恰当的程序表达。但总体来说,我们本次设计的频率计虽然在很大程度上存在“偷工减料”所导致的问题,但在最后运行时,还是可以达到预期额效果,并且对我们的组员来说,只存在问题才会让大家投入更多的思考,解决问题的过程也是一个提高的过程。

本次模块的分配中,由于组员人数比较多,所以我所负责的模块是最为简单的顶层设计模块,但在第一个星期的设计过程,也有参与其他模块的设计和讨论,所以虽然最后的任务相对容易,但在整个过程中也学到了很多东西。

参考文献:

《EDA技术实用教程》——VHDL版/潘松,黄继业编著.——5版.——北京:科学出版社,2013.

附录:

所用程序:

1、方波信号发生及选择:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fangbo is

port(clk:in std_logic; --输入时钟50Mhz

key:in std_logic_vector(4 downto 0);

tclk: out std_logic);

end fangbo;

architecture hav of fangbo is

signal a,b,c,d,e :std_logic;

begin

fangbo:process(clk) --产生五种方波

variable cnt1,cnt2,cnt3,cnt4,cnt5 :INTEGER RANGE 0 TO 5000000;

begin

if clk'event and clk='1' then

if cnt1<250 then cnt1:=cnt1+1;

else a<=not a; cnt1:=0;

end if;

if cnt2<2500 then cnt2:=cnt2+1;

else b<=not b; cnt2:=0;

end if;

if cnt3<25000 then cnt3:=cnt3+1;

else c<=not c; cnt3:=0;

end if;

if cnt4<250000 then cnt4:=cnt4+1;

else d<=not d; cnt4:=0;

end if;

if cnt5<2500000 then cnt5:=cnt5+1;

else e<=not e; cnt5:=0;

end if;

end if;

end process;

xuanze:process(key) ----选择方波

begin

case(key) is

when "10000" => tclk<=e;

when "01000" => tclk<=d;

when "00100" => tclk<=c;

when "00010" => tclk<=b;

when "00001" => tclk<=a;

when others => NULL;

end case;

2、测频控制:library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

USE IEEE.STD_LOGIC_ARITH.ALL;

entity cepin is

port(clk:in std_logic; --输入时钟50Mhz

tclk:in std_logic;

rst : in std_logic;

x : out integer range 0 to 500000000;

j,lc1,lc1k: out std_logic);

end cepin;

architecture hav of cepin is

signal a :std_logic ;

SIGNAL cnt0:INTEGER RANGE 0 TO 5000000;

begin

cepin:process(clk,tclk)

begin

if rst='0' then cnt0<=0;x<=0;j<='0';

else

j<=tclk;

if clk'event and clk='1' then

if tclk='1' then cnt0<=cnt0+1;

else

if cnt0>24999 then

x<=(250000000/cnt0*10);lc1<='1';lc1k<='0'; cnt0<=0;

elsif cnt0/=0 and cnt0<25000 then

x<=2500000/cnt0;lc1<='0';lc1k<='1'; cnt0<=0;

end if;

end if;

end if;

end if;

end process;

end hav;

3、译码及显示:library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity yima is

port ( A1,A2,A3,A4,A5 : in STD_LOGIC_VECTOR(3 DOWNTO 0);

bcd0,bcd1,bcd2,bcd3,bcd4,bcd5:out std_logic_vector(6 downto 0));

end yima;

architecture hav of yima is

begin

yima:process(A1,A2,A3,A4,A5)

BEGIN

bcd2(6 downto 0)<="1110111"; -- _

case (A1) is

WHEN"0000" => BCD0(6 DOWNTO 0)<="1000000"; --0

WHEN"0001" => BCD0(6 DOWNTO 0)<="1111001"; --1

WHEN"0010" => BCD0(6 DOWNTO 0)<="0100100"; --2

WHEN"0011" => BCD0(6 DOWNTO 0)<="0110000"; --3

WHEN"0100" => BCD0(6 DOWNTO 0)<="0011001"; --4

WHEN"0101" => BCD0(6 DOWNTO 0)<="0010010"; --5

WHEN"0110" => BCD0(6 DOWNTO 0)<="0000010"; --6

WHEN"0111" => BCD0(6 DOWNTO 0)<="1111000"; --7

WHEN"1000" => BCD0(6 DOWNTO 0)<="0000000"; --8

WHEN"1001" => BCD0(6 DOWNTO 0)<="0010000"; --9

WHEN OTHERS => BCD0(6 DOWNTO 0)<="1111111";bcd2(6 downto 0)<="1111111";

end case;

case (A2) is

WHEN"0000" => BCD1(6 DOWNTO 0)<="1000000"; --0

WHEN"0001" => BCD1(6 DOWNTO 0)<="1111001"; --1

WHEN"0010" => BCD1(6 DOWNTO 0)<="0100100"; --2

WHEN"0011" => BCD1(6 DOWNTO 0)<="0110000"; --3

WHEN"0100" => BCD1(6 DOWNTO 0)<="0011001"; --4

WHEN"0101" => BCD1(6 DOWNTO 0)<="0010010"; --5

WHEN"0110" => BCD1(6 DOWNTO 0)<="0000010"; --6

WHEN"0111" => BCD1(6 DOWNTO 0)<="1111000"; --7

WHEN"1000" => BCD1(6 DOWNTO 0)<="0000000"; --8

WHEN"1001" => BCD1(6 DOWNTO 0)<="0010000"; --9

WHEN OTHERS => BCD1(6 DOWNTO 0)<="1111111";bcd2(6 downto 0)<="1111111";

end case;

case (A3) is

WHEN"0000" => BCD3(6 DOWNTO 0)<="1000000"; --0

WHEN"0001" => BCD3(6 DOWNTO 0)<="1111001"; --1

WHEN"0010" => BCD3(6 DOWNTO 0)<="0100100"; --2

WHEN"0011" => BCD3(6 DOWNTO 0)<="0110000"; --3

WHEN"0100" => BCD3(6 DOWNTO 0)<="0011001"; --4

WHEN"0101" => BCD3(6 DOWNTO 0)<="0010010"; --5

WHEN"0110" => BCD3(6 DOWNTO 0)<="0000010"; --6

WHEN"0111" => BCD3(6 DOWNTO 0)<="1111000"; --7

WHEN"1000" => BCD3(6 DOWNTO 0)<="0000000"; --8

WHEN"1001" => BCD3(6 DOWNTO 0)<="0010000"; --9

WHEN OTHERS => BCD3(6 DOWNTO 0)<="1111111";bcd2(6 downto 0)<="1111111";

end case;

case (A4) is

WHEN"0000" => BCD4(6 DOWNTO 0)<="1000000"; --0

WHEN"0001" => BCD4(6 DOWNTO 0)<="1111001"; --1

WHEN"0010" => BCD4(6 DOWNTO 0)<="0100100"; --2

WHEN"0011" => BCD4(6 DOWNTO 0)<="0110000"; --3

WHEN"0100" => BCD4(6 DOWNTO 0)<="0011001"; --4

WHEN"0101" => BCD4(6 DOWNTO 0)<="0010010"; --5

WHEN"0110" => BCD4(6 DOWNTO 0)<="0000010"; --6

WHEN"0111" => BCD4(6 DOWNTO 0)<="1111000"; --7

…………

…………

…………限于本文篇幅 余下代码请从51黑下载附件…………

完整的Word格式文档51黑下载地址:

EDA课程设计报告 频率计设计.docx

(300.47 KB, 下载次数: 70)

EDA课程设计报告 频率计设计.docx

(300.47 KB, 下载次数: 70)

|