EDA时钟的顶层设计部分

VHDL源码如下:

- // Copyright (C) 1991-2011 Altera Corporation

- // Your use of Altera Corporation's design tools, logic functions

- // and other software and tools, and its AMPP partner logic

- // functions, and any output files from any of the foregoing

- // (including device programming or simulation files), and any

- // associated documentation or information are expressly subject

- // to the terms and conditions of the Altera Program License

- // Subscription Agreement, Altera MegaCore Function License

- // Agreement, or other applicable license agreement, including,

- // without limitation, that your use is for the sole purpose of

- // programming logic devices manufactured by Altera and sold by

- // Altera or its authorized distributors. Please refer to the

- // applicable agreement for further details.

- // PROGRAM "Quartus II"

- // VERSION "Version 11.0 Build 208 07/03/2011 Service Pack 1 SJ Full Version"

- // CREATED "Sun Apr 16 10:29:37 2017"

- module dingceng(

- clk,

- reset,

- set,

- up,

- d_col,

- d_out

- );

- input wire clk;

- input wire reset;

- input wire set;

- input wire up;

- output wire [7:0] d_col;

- output wire [7:0] d_out;

- wire h_set;

- wire key_clk;

- wire m_set;

- wire s_clk;

- wire s_set;

- wire scan_clk;

- wire set_en;

- wire up_en;

- wire [7:0] SYNTHESIZED_WIRE_0;

- wire [7:0] SYNTHESIZED_WIRE_1;

- wire [7:0] SYNTHESIZED_WIRE_2;

- Clock_cnt b2v_inst(

- .clk(clk),

- .h_set(h_set),

- .m_set(m_set),

- .s_set(s_set),

- .up_en(up_en),

- .rst_n(reset),

- .s_clk(s_clk),

- .h_data(SYNTHESIZED_WIRE_0),

- .m_data(SYNTHESIZED_WIRE_1),

- .s_data(SYNTHESIZED_WIRE_2));

- Clock_ctl b2v_inst1(

- .clk(clk),

- .rst_n(reset),

- .set_en(set_en),

- .h_set(h_set),

- .m_set(m_set),

- .s_set(s_set));

- defparam b2v_inst1.hour_set = 2'b01;

- defparam b2v_inst1.minute_set = 2'b10;

- defparam b2v_inst1.normal = 2'b00;

- defparam b2v_inst1.second_set = 2'b11;

- Key_ctl b2v_inst2(

- .set(set),

- .rst_n(reset),

- .clk(clk),

- .key_clk(key_clk),

- .set_en(set_en));

- up b2v_inst3(

- .up(up),

- .rst_n(reset),

- .clk(clk),

- .key_clk(key_clk),

- .up_en(up_en));

- Freq_div b2v_inst4(

- .clk(clk),

- .rst_n(reset),

- .scan_clk(scan_clk),

- .key_clk(key_clk),

- .s_clk(s_clk));

- Display b2v_inst5(

- .clk(clk),

- .scan_clk(scan_clk),

- .rst_n(reset),

- .h_data(SYNTHESIZED_WIRE_0),

- .m_data(SYNTHESIZED_WIRE_1),

- .s_data(SYNTHESIZED_WIRE_2),

- .d_col(d_col),

- .d_out(d_out));

- endmodule

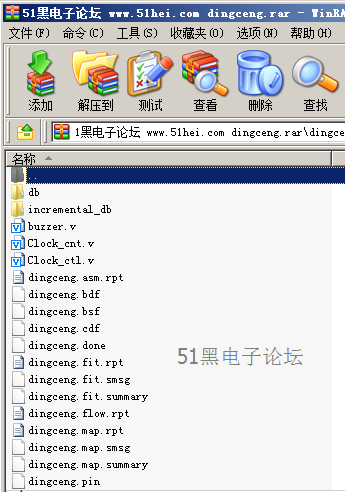

所有资料51hei提供下载:

dingceng.rar

(5.9 MB, 下载次数: 29)

dingceng.rar

(5.9 MB, 下载次数: 29)

|