|

电子科技大学实验文档

名称数字逻辑电路实验 实验名称基于一般模型的计数器设计 指导教师郑* 学生姓名郑* 学生学号17011737 学生班级 17040324 学生专业电子信息类 实验日期 2018年6月 (1)熟悉计数器的一般模型 (2)掌握在QuartusII中实现计数器一般模型的方法。 (3)掌握自顶向下的电路设计方法。 (4)掌握使用FPGA实现时序电路的方法。 如果把计数器看作是输出状态随时钟信号不断变化的状态机,可以把它抽象成如图5.2.1所示的一般结构模型。在这个模型里,包含一个根据现态求得次态的状态译码器,和一个由时钟信号同步控制的n位寄存器组。

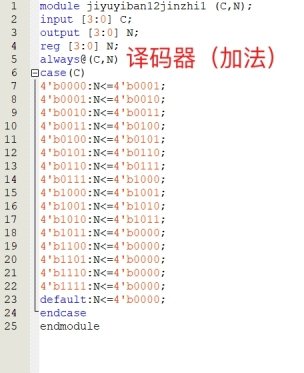

如果把计数器看作是输出状态随时钟信号不断变化的状态机,可以把它抽象成如图5.2.1所示的一般结构模型。在这个模型里,包含一个根据现态求得次态的状态译码器,和一个由时钟信号同步控制的n位寄存器组。 图5.2.1 计数器的一般模型 在QuartusII中,无论是实现寄存器组模块,还是实现译码器模块,都是比较容易的。例如实现一个模16计数器,根据第四章实验4.4广义译码器的设计方法,可以写Verilog HDL代码实现。

首先创建新工程counter16,为新工程建立新文件夹counter16,命名工程和顶层文件名为counter16。点击New|Verilog HDL File,新建文本文件,打开文本编辑窗口,键入Verilog HDL代码,如图5.2.2所示,生成CNT16元件。

图5.2.2 状态译码器

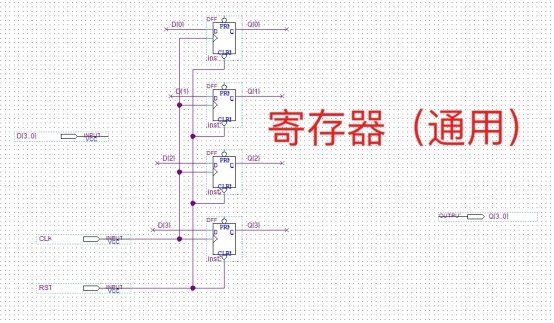

在这里,由于输出状态有4位,需要4个寄存器保存数据,所以寄存器组模块的电路图如图5.2.3所示。点击New|Block Diagram/Schematic File,新建一个原理图文件,命名为DFF4。在打开的图形编辑窗口,放置4个dff元件,以及相应的输入输出端口,连线。将所有的时钟信号用统一的时钟输入信号CLK来控制,所有的清零信号,用RST来统一控制。命名好输入输出端口,4位寄存器组模块就绘制好了,生成一个DFF4的元件。当然也可以调用元件库中的74175等集成的寄存器宏模块实现电路。

然后再新建一个原理图文件,命名为counter16,为顶层文件,和工程同名。调用CNT16和DFF4元件,按照计数器一般结构模型连接两个元件。注意模块间传输多位数据时,点击工具栏上的  符号,用总线进行连接。加上相应的输入和输出端口,绘制顶层电路,如图5.2.4所示。

图5.2.3 DFF4寄存器组

图5.2.4 计数器一般模型原理图

设计计数器时,有时需要设计进位输出或者借位输出信号,因此增加一个进位信号,如下图5.2.5所示。

图5.2.5 进位输出电路

电路原理图绘制完成后,接下来是编译、仿真和下载。仿真时,尽可能测试所有的输入情况。例如在RST信号初期,用鼠标左键拖曳的方式选中一段,置为低电平(有效,清零),后面置为高电平(无效,正常计数),如图5.2.6所示,以观察清零信号对输出的影响。

图5.2.6 对RST赋值

图5.2.7是16进制计数器的仿真结果。由图可见,在计数状态到达1110时,进位输出有一个毛刺。这是因为在输出状态从1011到1110变化时,变化时间不一致,导致有1111的信号短暂发生,因而出现了进位输出端的毛刺。

图5.2.7 16进制计数器仿真结果

在这个一般模型电路的基础上,增加一个比较器模块,可以实现反馈清零型的一般模型电路。例如实现一个模12计数器,电路模型图如图5.2.8所示。

图5.2.8 基于一般模型的反馈清零型电路模块图

在QuartusII中画出原理图,如图5.2.9所示。其中,译码器模块和寄存器组和之前电路一模一样。比较器模块,用来比较现态CS和反馈清零预置数A,如果两者相等,则清零;不相等,正常计数。

图5.2.9 反馈清零的一般模型电路原理图

比较器具体实现如下:

module comP(CS,A,R); //定义模块名,及输入输出端口

input [3:0]CS,A;// 定义输入端口,CS为现态输出,A为预置清零状态

output R;// 定义输出端口,R为清零标志数

reg R;// 输出端口定义为reg类型

always@(CS,A,R)// always过程语句,当CS、A、R发生变化,执行后面的块语句

case(CS) // case条件语句,这里也可以用if语句实现同样的功能

A:R<=1'b1; // 当CS等于A,R被赋值为1,这时反馈回寄存器,使输出清零

default:R<=1'b0;// 当CS不等于A,R被赋值为0,这时计数器正常计数;

endcase // case语句结束

endmodule // 模块结束

这个电路,可以通过修改清零预置数A,方便的更改计数模值,仿真结果如图5.2.10所示。

图5.2.10 反馈清零型一般模型电路的仿真结果 - 基于一般结构模型,设计一个10进制加法计数器。使用QuartusII 完成创建工程、编辑电路图、编译,编辑波形文件仿真,记录波形并说明仿真结果,最后在FPGA上进行硬件测试。

(2)根据计数器设计的一般模型,设计一个12进制加减法可逆计数器。使用QuartusII 完成创建工程、编辑电路图、编译,编辑波形文件仿真,记录波形并说明仿真结果,最 FPGA上进行硬件测试  - 根据计数器设计的一般模型,设计初值可预置的计数器,变换预置数可使计数模值在2-20之间变化。使用QuartusII 完成创建工程、编辑电路图、编译,编辑波形文件仿真,记录波形并说明仿真结果,最后在FPGA上进行硬件测试。

-

五.实验总结 本次实验先从最基本的一般模型设计计数器,按照一般模型的原理图,先设计译码器对输入信号进行编码输出译码后的信号给寄存器存储数据。再根据要求,设计出正确的进位输出。本次实验在预习的电路原理图设计与用语言设计译码器中出现不少问题。后不断查阅资料,理解完毕,且在设计初值可预调的计数器实验中,由于采取电路图的方式难以成功实现,故在此次实验设计中采取了以HDL语言的形式进行编译及仿真,并成功实现。而在实现引脚导入时未进行分频,但在仿真中已成功实现,且在位数上与理论设想相同。经过这次实验,我熟悉计数器的一般模型掌握在QuartusII中实现计数器一般模型的方法。掌握自顶向下的电路设计方法。掌握使用FPGA实现时序电路的方法。 六.思考题 在verilog设计中,给时序电路清0有两种不同方法,它们是什么?如何实现? 同步复位和异步复位。同步复位是指与时钟同步,当复位信号有效之后,出现时钟有效边沿时才对电路模块进行复位操作;而异步复位与时钟信号无关,只要复位信号有效,无论这时时钟信号是什么样,都对电路模块进行复位操作。

以上图文的Word格式文档下载(内容和本网页上的一模一样,方便大家保存):

|