БОЬћзюКѓгЩ zl2168 гк 2018-7-22 15:47 БрМ

ФуЕФЮЪЬтВЛЪЧвЛЖўОфЛАФмЫЕЧхЕФЃЌНщЩмФу2БОЪщЃЌЩЯУцгаД№АИЃЌздМКШЅПДАЩЃЁ

ЁЖЪ§зжЕчзгММЪѕЛљДЁЁЗЃЈISBN 978-7-111-21516-5ЃЉЛњаЕЙЄвЕГіАцЩч

ЁЖЪ§зжЕчзгбЇЯАжИЕМгыЯАЬтНтД№ЁЗЃЈISBN 978-7-111-21517-2ЃЉЛњаЕЙЄвЕГіАцЩчИУЪщжагаЃК

2.2.2 УХЕчТЗЭтВПЬиадКЭжївЊВЮЪ§

ЂБ ЕчбЙДЋЪфЬиад

ЂХ ЕчбЙДЋЪфЬиад

ЂЦ ГЃгУУћДЪКЭВЮЪ§

Ђй ЪфГіИпЕчЦНUOHЁЃ

Ђк ЪфГіЕЭЕчЦНUOLЁЃ

Ђл уажЕЕчбЙUTHЁЃ

Ђм ЙиУХЕчЦНUOFFЁЃ ЙиУХЕчЦНUOFFЁЃUOFFЪЧTTLгыЗЧУХЕчТЗЪфГіИпЕчЦНЪБЃЌЪфШыЖЫдЪаэЪфШыЕФзюДѓЕЭЕчЦНжЕЁЃМДЮЊБЃжЄTTLгыЗЧУХЪфГіИпЕчЦНЃЌгІТњзуuIЁмUOFFЃЌUOFFЕФШЗЧаЪ§жЕвђУПвЛЦїМўЖјвьЁЃвЛАуЃЌЪжВсжаИјГіЪфШыЕЭЕчЦНзюДѓжЕUILmaxДњЬцUOFFЁЃ74LSЯЕСаУХЕчТЗUILmaxЃН0.8VЁЃ

Ђн ПЊУХЕчЦНUONЁЃ ПЊУХЕчЦНUONЁЃUONЪЧTTLгыЗЧУХЕчТЗЪфГіЕЭЕчЦНЪБЃЌЪфШыЖЫдЪаэЪфШыЕФзюаЁИпЕчЦНжЕЁЃМДЮЊБЃжЄTTLгыЗЧУХЪфГіЕЭЕчЦНЃЌгІТњзуuIЁнUONЃЌUONЕФШЗЧаЪ§жЕвђУПвЛЦїМўЖјвьЁЃвЛАуЃЌЪжВсжаИјГіЪфШыИпЕчЦНзюаЁжЕUIHminДњЬцUONЁЃ74LSЯЕСаУХЕчТЗUIHminЃН2VЁЃ

Ђо дыЩљШнЯоЁЃ

ЂВ ЪфШыЬиад

ЂХ ЪфШыЗќАВЬиад

ЂЦ ЪфШыИКдиЬиад

ЭМ2-19ЮЊ74LSЯЕСаУХЕчТЗЪфШыИКдиЬиадЁЃRIНЯаЁЪБЃЌuIЯрЕБгкЪфШыЕЭЕчЦНЃЌгыЗЧУХДІгкЙиУХзДЬЌЃЛRIНЯДѓЪБЃЌuIЯрЕБгкЪфШыИпЕчЦНЃЌгыЗЧУХДІгкПЊУХзДЬЌЁЃМДЃКШєашБЃГжuIЮЊЕЭЕчЦНЃЈuI<UILmaxЃЉЃЌRIВЛФмЙ§ДѓЃЌаыRI<ROFFЁЃROFFГЦЮЊЙиУХЕчзшЃЌЪЧЪЙгыЗЧУХБЃГжЙиУХзДЬЌЕФRIзюДѓжЕЁЃ74LSЯЕСаУХЕчТЗROFF Ёж4.2kІИЁЃЕБRIзуЙЛДѓЪБЃЌuIЁж1VВЂБЃГжЛљБОВЛБфЃЌШчЭМ2-11жаЃЌuI =ЃЈuBE1+uBE5ЃЉ-uVD3Ёж1.4-0.4=1VЁЃЯрЕБгкЪфШыИпЕчЦНЃЌгыЗЧУХДІгкПЊУХзДЬЌЁЃМДЃКШєашБЃГжuIЯрЕБгкЪфШыИпЕчЦНЃЌRIВЛФмЙ§аЁЃЌаыRIЃОRONЁЃRONГЦЮЊПЊУХЕчзшЃЌЪЧЪЙгыЗЧУХБЃГжПЊУХзДЬЌЕФRIзюаЁжЕЁЃ74LSЯЕСаУХЕчТЗRON Ёж6.3kІИЁЃ

ЂГ ЪфГіЬиад

ЂХ РЕчСїИКдиЪфГіЬиад

ЂЦ ЙрЕчСїИКдиЪфГіЬиад

ЂД УХЕчТЗЕФжївЊВЮЪ§

ЂХ ОВЬЌЖЏКФPD

ЂЦ ДЋЪфбгГйЪБМфtpd

ЂЕ ВЛЭЌЯЕСаЕФTTLУХЕчТЗ

ЂХ 74ЯЕСаЃЈЛљБОаЭЃЉ

ЂЦ 74LЯЕСаЃЈЕЭЙІКФЃЉ

ЂЧ 74HЯЕСаЃЈИпЫйЃЉ

ЂШ 74SЯЕСаЃЈаЄЬиЛљЃЉ

ЂЩ 74LSЯЕСаЃЈЕЭЙІКФаЄЬиЛљЃЉ

ЂЪ 74ASЯЕСаЃЈЯШНјИпЫйаЄЬиЛљЃЉ

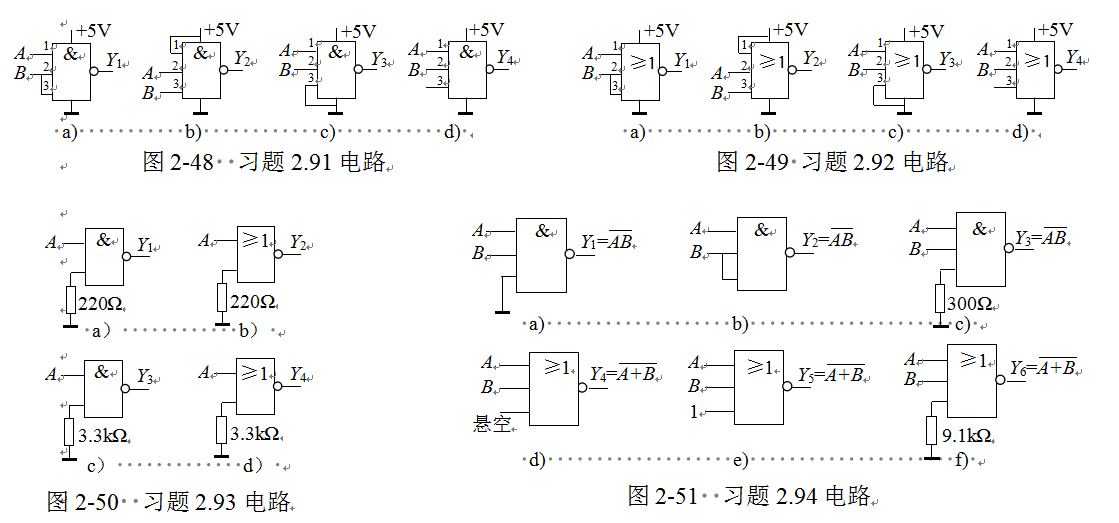

ЂЫ 74ALSЯЕСаЃЈЯШНјЕЭЙІКФаЄЬиЛљЃЉ ИДЯАЫМПМЬт 2.30 CMOSУХЕчТЗВЛгУЕФЪфШыЖЫФмЗёаќПеЃПдкетвЛЕуЩЯгыTTLУХЕчТЗгаЪВУДВЛЭЌЃП 2.5 ЯАЬт 2.91 вбжЊ74LSЯЕСаШ§ЪфШыЖЫгыЗЧУХЕчТЗШчЭМ2-48ЫљЪОЃЌЦфжа2ИіЪфШыЖЫЗжБ№НгЪфШыаХКХAЁЂBЃЌСэвЛИіЪфШыЖЫЮЊЖргрв§НХЁЃЪдЗжЮіЕчТЗжаЖргрв§НХЕФНгЗЈЪЧЗёе§ШЗЃП

2.92 вбжЊ74LSЯЕСаШ§ЪфШыЖЫЛђЗЧУХЕчТЗШчЭМ2-49ЫљЪОЃЌЦфжа2ИіЪфШыЖЫЗжБ№НгЪфШыаХКХAЁЂBЃЌСэвЛИіЪфШыЖЫЮЊЖргрв§НХЁЃЪдЗжЮіЕчТЗжаЖргрв§НХНгЗЈЪЧЗёе§ШЗЃП

2.93 вбжЊЭМ2-50ЕчТЗжаTTLУХЕчТЗЕФROFF=0.8kІИЃЌRON=2.5kІИЃЌЪдаДГіЪфГіЖЫY1~Y4КЏЪ§БэДяЪНЁЃ

2.94вбжЊ74LSЯЕСаШ§ЪфШыЖЫУХЕчТЗШчЭМ2-51ЫљЪОЃЌAЁЂBЮЊгааЇЪфШыаХКХЃЌСэвЛИіЪфШыЖЫЮЊЖргрв§НХЁЃШєвЊЧѓЕчТЗЪфГіY1~Y6АДЭМЫљЧѓЃЌЪдХаЖЯЕчТЗНгЗЈЪЧЗёе§ШЗЃПШєгаДэЃЌЪдгшвдИФе§ЁЃ 2.95 ШєЭМ 2-48жагыЗЧУХИФГЩ 74HCЯЕСаЛђCMOS 4000ЯЕСаЃЌдйХаЕчТЗНгЗЈЪЧЗёе§ШЗЃП

2.96 вбжЊCMOSУХЕчТЗШчЭМ 2-50ЫљЪОЃЌЪджиаТаДГіЪфГіЖЫY1~Y4КЏЪ§БэДяЪНЁЃ

2.97 вбжЊCMOSШ§ЪфШыЖЫУХЕчТЗШчЭМ 2-51ЫљЪОЃЌЪджиаТХаЖЯЕчТЗНгЗЈЪЧЗёе§ШЗЃПШєгаДэЃЌЪдгшвдИФе§ЁЃ

НЬИЈЪщЁЖЪ§зжЕчзгбЇЯАжИЕМгыЯАЬтНтД№ЁЗгыНЬВФЪщЁЖЪ§зжЕчзгММЪѕЛљДЁЁЗХфЬзЃЌЯАЬтЖМгаЯъНтЁЃ

|

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664