FPGA 驱动vga显示源码仿真与资料都有

- `timescale 1ns / 1ps

- /*==============================================================================

- Engineer : a fei

- Module Hierarchy : top function module

- Design Name : vga_module.v

- Module Name : vga_module

- Project Name : test_project_top.qsf

- Target Devices : Altera

- Tool versions : QUARTUSII11.0/Windows XP

- Description : 显示“囧”字,绿背景,蓝框,800*600@60Hz

- Dependencies :

- Revision : 0.01 - File Created

- Additional Comments : modify the pixer to 800X600@72Hz

- ==============================================================================*/

- module vga_module(

- input i_fpga_clk , //50MHz

- input i_rst_n , //低电平复位

-

- output o_vga_red ,

- output o_vga_green ,

- output o_vga_blue ,

- output o_vga_hsync , //行同步信号

- output o_vga_vsync //场同步信号

- );

- //================================================================================

- // 4、Wire and reg declaration

- //================================================================================

- reg[9:0] r_x_cnt; //行坐标(这里包括了行同步、后沿、有效数据区、前沿)

- reg[9:0] r_y_cnt; //列坐标(这里包括了场同步、后沿、有效数据区、前沿)

- always @ (posedge i_fpga_clk or negedge i_rst_n)

- if(!i_rst_n)

- r_x_cnt <= 10'd0;

- else if(r_x_cnt == 10'd1000)

- r_x_cnt <= 10'd0; //行计数只记到1000

- else

- r_x_cnt <= r_x_cnt+1'b1;

-

- always @ (posedge i_fpga_clk or negedge i_rst_n)

- if(!i_rst_n)

- r_y_cnt <= 10'd0;

- else if(r_y_cnt == 10'd665)

- r_y_cnt <= 10'd0; //场同步只记到665

- else if(r_x_cnt == 10'd1000)

- r_y_cnt <= r_y_cnt+1'b1;//每计数完一行,场同步就加一

- else

- r_y_cnt <= r_y_cnt;

-

- //================================================================================

- // 4、Wire and reg declaration

- //================================================================================

- wire w_vga_valid; //有效数据显示区标志,当坐标不处于有效显示区时,R、G、B三原色信号接的电平都必须拉底(0)*/

- assign w_vga_valid = (r_x_cnt > 10'd180) && (r_x_cnt < 10'd980) //800*600

- && (r_y_cnt > 10'd35) && (r_y_cnt < 10'd635);

-

- wire [9:0] w_x_pos;

- wire [9:0] w_y_pos; //有效显示区坐标

- assign w_x_pos = r_x_cnt-10'd180;//

- assign w_y_pos = r_y_cnt-10'd35;//

- reg r_vga_hsync;

- reg r_vga_vsync;

- always @ (posedge i_fpga_clk or negedge i_rst_n)

- if (!i_rst_n)

- begin

- r_vga_hsync <= 1'b0;

- r_vga_vsync <= 1'b0;

- end

- else

- begin

- r_vga_hsync <= r_x_cnt <= 10'd50; //产生hsync信号(行同步)0-50

- r_vga_vsync <= r_y_cnt <= 10'd6; //产生vsync信号(场同步)0-6

- end

-

- //================================================================================

- // 4、Wire and reg declaration

- //================================================================================

- //显示一个矩形框

- wire a_dis,b_dis,c_dis,d_dis; //矩形框显示区域定位

- assign a_dis = ( (w_x_pos>=200) && (w_x_pos<=220) )

- && ( (w_y_pos>=140) && (w_y_pos<=460) );

- assign b_dis = ( (w_x_pos>=580) && (w_x_pos<=600) )

- && ( (w_y_pos>=140) && (w_y_pos<=460) );

- assign c_dis = ( (w_x_pos>=220) && (w_x_pos<=580) )

- && ( (w_y_pos>140) && (w_y_pos<=160) );

- assign d_dis = ( (w_x_pos>=220) && (w_x_pos<=580) )

- && ( (w_y_pos>=440) && (w_y_pos<=460) );

-

- wire e_dis,f_dis,g_dis,h_dis; //矩形框显示区域定位

- assign e_dis = ( (w_x_pos>=320) && (w_x_pos<=340) )

- && ( (w_y_pos>=320) && (w_y_pos<=410) );

- assign f_dis = ( (w_x_pos>=460) && (w_x_pos<=480) )

- && ( (w_y_pos>=320) && (w_y_pos<=410) );

- assign g_dis = ( (w_x_pos>=340) && (w_x_pos<=460) )

- && ( (w_y_pos>320) && (w_y_pos<=340) );

- assign h_dis = ( (w_x_pos>=340) && (w_x_pos<=460) )

- && ( (w_y_pos>=390) && (w_y_pos<=410) );

- wire i_dis,j_dis,k_dis,l_dis;

- assign i_dis = ( (w_x_pos>=320) && (w_x_pos<=340) )

- && ( (w_y_pos>=210) && (w_y_pos<=290) );

- assign j_dis = ( (w_x_pos>=460) && (w_x_pos<=480) )

- && ( (w_y_pos>=210) && (w_y_pos<=290) );

- assign k_dis = ( (w_x_pos>=270) && (w_x_pos<=320) )

- && ( (w_y_pos>270) && (w_y_pos<=290) );

- assign l_dis = ( (w_x_pos>=480) && (w_x_pos<=530) )

- && ( (w_y_pos>=270) && (w_y_pos<=290) );

- //================================================================================

- // 2、output

- //================================================================================

- assign o_vga_red = w_vga_valid ? (i_dis | j_dis | k_dis | l_dis): 1'b0;

- assign o_vga_blue = w_vga_valid ? (a_dis | b_dis | c_dis | d_dis | e_dis | f_dis | g_dis | h_dis ) : 1'b0;

- assign o_vga_green = w_vga_valid ? ~(a_dis | b_dis | c_dis | d_dis | e_dis | f_dis | g_dis | h_dis | i_dis | j_dis | k_dis | l_dis) : 1'b0;

- assign o_vga_vsync = r_vga_vsync ;

- assign o_vga_hsync = r_vga_hsync ;

-

- //================================================================================

- endmodule

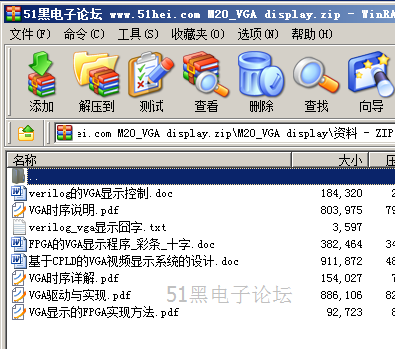

全部资料51hei下载地址:

M20_VGA display.zip

(4.48 MB, 下载次数: 65)

M20_VGA display.zip

(4.48 MB, 下载次数: 65)

|