FPGA技术综合设计实训

目录

1 概述

1.1 设计要求

1.1.1 设计任务

1.1.2 性能指标要求

1.2 总体设计基本原理及框图

1.2.1 基本原理

1.2.2 总体框图

2 系统软件设计分析

2.1时钟模块

2.2控制模块

2.3计程模块

2.4音乐模块

2.5 LCD显示模块

2.6计费模块

3 系统测试(调试)

3.1 测试仪器与设备

3.2 性能指标测试

3.3 结果分析

4 波形发生器设计

5 实训总结

6 参考文献

附录

出租车计费器的设计 1 概述EDA(Electronic Design Automation)即电子设计自动化,是电子设计技术的核心,它的系统级高层次电子设计方法,对整个系统进行方案设计和功能划分,无须通过门级原理图描述电路,而是针对设计目标进行功能描述,。 FPGA 是现场可编程门阵列的简称。它结合了微电子技术、电路技术和EDA技术,使设计者可以集中精力进行所需逻辑功能的设计,缩短设计周期,提高设计质量。FPGA的开发系统包括软件和硬件两个部分,开发系统软件指专用的编程语言和相应的汇编程序或编译程序。开发系统硬件部分包括计算机和编程器。编程器是对FPGA进行写入和擦除的专用装置,能够供写入或擦除操作所需要的电源电压和控制信号,并通过串行接口从计算机接收编程数据,最终写进FPGA之中。 基于FPGA的计费器系统利用Verilog HDL语言,采用模块化程序设计,自顶向下、由粗到细、逐步求精的方法,将基于FPGA的计费器系统的整体逐步分解各个模块。它不需要专门的硬件,只通过软件编程即可实现计费器系统的逻辑功能、电路结构和连接形式。Verilog HDL语言类似C语言,可读性强、更易理解,这种语言几乎覆盖了以往各种硬件描述语言的功能,在编程的过程中一般采用自顶向下的电路设计过程。 本设计利用Verilog HDL语言,在QuartusⅡ13.0软件中将出租车计费器基本结构分成6个模块对其进行程序汇编。将各块程序生成的.v文件组合在一起,生成数字钟源代码的.bdf 图形文件,最后下载到CycloneⅡ系列芯片EP20C8Q208C8N中,验证试验结果。 1.1 设计要求1.1.1 设计任务设计并制作一台出租车计费器。 1.1.2 性能指标要求① 用EDA实训仪的I/O设备和PLD芯片实现出租车计费器的设计。 ② 出租车起步开始计程和计费,计程系统按实际公里数计程,计费系统首先显示起步价(如7.0),车行驶2km以内,只收起步价7元。 ③ 出租车行驶超过2km后,按每公里1.6元在7.0元的基础上增加。 ④ 出租车行驶超过10km后(或超过20元路费),每公里加收50%的车费,即车费变为每公里2.4元。 ⑤ 出租车达到目的地后,(用一个按钮)计程和计费数据清零,为下一次计费开始。 1.2 总体设计基本原理及框图1.2.1 基本原理该出租车计费器的基本原理方框图如图1所示,由时钟模块、控制模块、计程模块、音乐模块、LCD显示模块、计费模块6部分组成。该计费系统通过分频模块将20MHz的时钟信号通过分频器变成1Hz的时钟信号和50Hz的显示输出信号。该出租车计费的标准是起步价是6元,2公里之内费用不变,当超过2公里时,每行驶1公里,费用加收50%元;由peo信号来控制有人或者没人,高电平有人,低电平显示空车,出租车计费显示模块显示相应的费用和行驶的里程。当res为低电平时,计费系统复位。该计费系统的显示费用是0~999.9元 1.2.2 总体框图图1 总体框图 2 系统软件设计分析整个系统由6个模块组成: 2.1时钟模块时钟模块,提供实时时间,并可以通过按键调节分钟和小时并由其qs、qm、qh分别输出秒、分、时,clk20m输入20Mhz,clrn清零,fj和hj为调分和调时。用于区分白天与夜间计费,白天时间6:00~00:00、夜间时间00:00~6:00,由两个60进制计数器和一个24进制计数器组成,生成一个元件符号。 图2-1 时钟模块元件符号图 60进制计数器程序: - module cont60(clk,clrn,q,cout,j);

- input j,clrn,clk;

- output reg [7:0] q;

- output reg cout;

- always @( posedge clk^j or posedge clrn )

- begin

- if(clrn) q=0;

- else

- begin

- q = q+1; if(q[3:0] >= 10)

- begin q[3:0] = 0;q[7:4] = q[7:4]+1;

- if(q[7:4] >= 6) q[7:4] = 0;

- end

- if( q == 'h00 ) cout = 1;else cout = 0;

- end

- end

- endmodule

- 24进制计数器程序:

- module cont24(clk,clrn,q,cout,j);

- input j,clk,clrn;

- output reg [7:0] q;

- output reg cout;

- always@( posedge clk^j or posedge clrn )

- begin

- if(clrn)begin q=0;cout = 0;end

- else

- begin

- q = q+1; if(q[3:0] >= 10)

- begin q[3:0] = 0; q[7:4] = q[7:4]+1;

- end

- if( q >= 'h24 )

- begin q = 0; cout = 1; end

- else cout = 0; end end endmodule

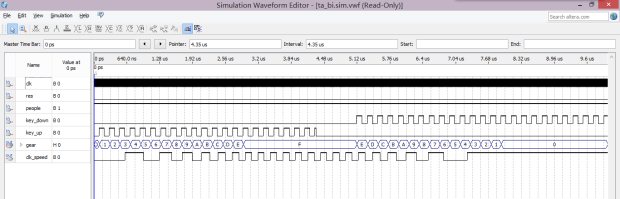

图2-2 时钟仿真图 2.2控制模块控制模块是用于控制车速的模块clk输入20Mhz,res清零作用,key_up是加速、key_down是减速,对应速度有0km/h、20km/h、40km/h——260km/h、280km/h、300km/h共15个速度调节来产生不同的频率由clk_speed输出,20km/h即11.1m每秒,所以20km/h要产生一秒为11100个上升沿,20Mhz/(2*11100),而gear输出不同的档位,通过对20MHz分频来产生不同的频率对应不同的速度,1秒内10000个上升沿表示1秒行驶了1m,改变频率即改变了1秒内上升沿的个数,就改变了速度。 图2-3 按键控制模块元件符号图 控制模块程序: - module key(clk,

- key_up,

- gear,

- res,

- key_down,

- clk_speed,

- people);

- input res,people;

- input key_up,clk,key_down;

- output reg clk_speed;

- reg [29:0] clk_sp_reg;

- output reg[3:0]gear;

- reg [29:0]up_c,down_c,n;

- initial begin

- gear='b1000;up_c=0;down_c=0;n=0;

- clk_sp_reg=0;

- end

- always@( posedge clk or posedge res)//加速减速控制

- begin

- if(res) begin down_c=0;up_c=0;end

- else if(!people)begin up_c=0; down_c =0; end else

- begin

- if(key_up)

- begin

- up_c=up_c+1'b1;

- end

- else

- begin

- up_c=0;

- end

- if(key_down)

- begin

- down_c=down_c+1'b1;

- end

- else

- begin

- down_c=0;

- end

- end

- end

- always @(posedge clk or posedge res)//速度对应的分频数,

- begin

- if(res) begin gear=0; end

- else if(!people)begin gear=0; clk_sp_reg=0; end else

- begin

- if(key_up ^ key_down )

- begin

- if(key_up==1)

- begin

- if(up_c==5 && gear<='b1110)//200000)

- gear=gear+1;

- if(gear>='b1111)

- gear='b1111;

- end

- if(key_down==1)

- begin

- if(down_c==5)//200000)

- if(gear=='b0)

- gear='b0;else gear=gear-1;

- end

- end

- case (gear)

- 0 : ; //速度为0

- 1 : clk_sp_reg=909;

- 2 : clk_sp_reg=454;

- 3 : clk_sp_reg=303;

- 4 : clk_sp_reg=227;

- 5 : clk_sp_reg=181;

- 6 : clk_sp_reg=151;

- 7 : clk_sp_reg=129;

- 8 : clk_sp_reg=113;

- 9 : clk_sp_reg=101;

- 10 : clk_sp_reg=90;

- 11 : clk_sp_reg=82;

- 12 : clk_sp_reg=75;

- 13 : clk_sp_reg=69;

- 14 : clk_sp_reg=64;

- 15 : clk_sp_reg=60;

- endcase

- end

- end

- always @( posedge clk or posedge res) //把20MHz分频,产生相对应速度的频率

- begin

- if(res)begin n<=0;clk_speed<=0;end

- else if(!people)begin n<=0;clk_speed<=0; end else

- begin

- if (n>=clk_sp_reg && gear!=0)

- begin n<=0;clk_speed<=~clk_speed; end

- else

- begin n<=n+1; clk_speed<=clk_speed;end

- end

- end

- endmodule

图2-4 控制模块仿真图

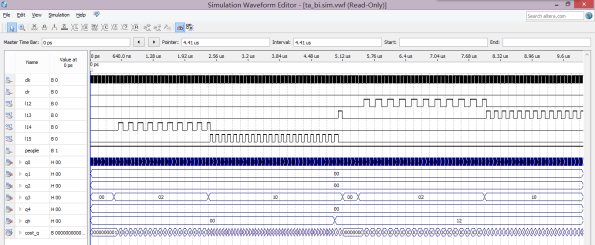

2.3计程模块计程模块由五个100进制的计数器组成,clk输入控制模块分频出来的频率,然后在计程模块进行计数,只显示qshiwan到qshiyi的计程其中qshiwan[7:4]是百米计程,这样能使计费精确到分以下,所以计程用1000个上升沿记为1米, 图2-5 计程模块元件符号图 计程模块程序: - module counter0_99(clk,clr,q,cout,people);

- input clk,clr,people;

- output reg [7:0] q;

- output reg cout;

- reg one='b1;

- initial q='h99;

- always@( posedge clk or posedge clr or negedge people )

- begin

- if(clr ) q=0;

- else

- begin if(!people) q=0;

- else

- begin

- q = q+1;

- if(q[3:0] >= 10)

- begin

- q[3:0] = 0;

- q[7:4] = q[7:4]+one;

- if(q[7:4] >= 10)

- q[7:4] = 0;

- end

- if( q == 0 )

- cout = 1;

- else

- cout = 0;

- end end end endmodule

图2-6 计程模块仿真图 2.4音乐模块音乐模块的clk是时钟输入,people是有人和没人的状态标志,beep外接蜂鸣器,并设定了两个音乐《送别》和《起风了》,作为乘客上车下车时播放的音乐,播放音乐的原理是通过改变频率来改变音高,改变延时时间来确定一小节拍的时间是240ms,通过分频产生。 //音高与频率的对应关系 //| | 1 | 2 | 3 | 4 | 5 | 6 | 7 | //|低音 |261.6Hz |293.7Hz |329.6Hz |349.2Hz | 392Hz | 440Hz |493.9Hz | //|中音 |523.3Hz |587.3Hz |659.3Hz |698.5Hz | 784Hz | 880Hz |987.8Hz | //|高音 |1045.5Hz|1174.7Hz|1318.5Hz|1396.9Hz| 1568Hz | 1760Hz |1975.5Hz| //乐谱参数:D=F/2K (D:参数,F:时钟频率,K:音高频率) 图2-7 音乐模块元件符号图 音乐模块程序: - module music( clk,people, beep);

- input clk,people;

- output reg beep;

- reg flag ,flag1;

- reg[7:0] state,state1; //乐谱状态机

- reg[16:0]count,count_end;

- reg[23:0]count1,count2; //乐谱参数:D=F/2K (D:参数,F:时钟频率,K:音高频率)

- parameter S_0=8'd20000000,

- L_1 = 17'd38226, M_1 = 17'd19109, H_1 = 17'd09564, //音1

- L_2 = 17'd34048, M_2 = 17'd17027, H_2 = 17'd08512, //音2

- L_3 = 17'd30339, M_3 = 17'd15167, H_3 = 17'd07584, //音3

- L_4 = 17'd28636, M_4 = 17'd14316, H_4 = 17'd07158, //音4

- L_5 = 17'd25510, M_5 = 17'd13368, H_5 = 17'd06377, //音5

- L_6 = 17'd22727, M_6 = 17'd11363, H_6 = 17'd05681, //音6

- L_7 = 17'd20247, M_7 = 17'd10123, H_7 = 17'd05062; //音7

- parameter TIME = 2400000; //控制每一个音的长短(480ms)

- parameter TIME1 = 4800000; //控制每一个音的长短(240ms)

- always @(posedge clk)

- begin

- if(people==0)

- begin

- flag=1; state1 =0;count2=0;

- if(flag1==1)

- begin

- count = count + 1'b1; //计数器加1

- if(count == count_end && count_end!=S_0)

- begin count = 17'h0; //计数器清零

- beep = !beep;end //输出取反

- if(count1 < TIME) count1 = count1 + 1'b1;

- //一个节拍240mS data=F/2/ms T=2*N*Tc

- else begin count1 = 24'd0;

- if(state == 8'd127)

- begin flag = 0;state=8'd0; end

- else state = state + 1'b1;

- case(state)

- 8'd0,8'd1,8'd2,8'd3: count_end = M_5;//低音"3",4个节拍

- 8'd4,8'd5: count_end = M_3;//低音"5",持续2个节拍

- 8'd6,8'd7: count_end = M_5;//低音"6",持续2个节拍

- 8'd8,8'd9,8'd10,8'd11,

- 8'd12,8'd13,8'd14,8'd15: count_end = H_1;//高音"1",8拍

- 8'd16,8'd17,8'd18,8'd19: count_end = M_6;//中音"6",4拍

- 8'd20,8'd21,8'd22,8'd23: count_end = H_1;//高音"1",4拍

- 8'd24,8'd25,8'd26,8'd27,

- 8'd28,8'd29,8'd30,8'd31,

- 8'd32,8'd33,8'd34,8'd35: count_end = M_5;//中音"5",8拍

- 8'd36,8'd37: flag1=0;//count_end = M_1;//低音"5",2拍

- endcase

- end

- end

- end

- else

- if(people==1)

- begin

- flag1=1; state =0;count1=0;

- if(flag==1)

- begin

- count = count + 1'b1; //计数器加1

- if(count == count_end)

- begin count = 17'h0; //计数器清零

- beep = !beep;end //输出取反

- if(count2 < TIME1) count2 = count2 + 1'b1;

- //一个节拍240mS data=F/2/ms T=2*N*Tc

- else begin count2 = 24'd0;

- if(state1 == 8'd229)

- begin flag = 0;state1=8'd0; end

- else state1 = state1 + 1'b1;

- case(state1)

- 8'd0,8'd1 : count_end = M_1;

- 8'd2,8'd3 : count_end = M_2;

- 8'd4,8'd5 : count_end = M_3;

- 8'd6,8'd7 : count_end = M_1;//

- 8'd8,8'd9 : count_end = M_6;

- 8'd10 : count_end = M_5;

- 8'd11 : count_end = M_6;

- 8'd12 : count_end = M_6;

- 8'd13,8'd14 : flag=0;//count_end = S_0;

- endcase

- end

- end

- end

- end

- endmodul

显示模块是使用LCD1602液晶屏,其中clk是时钟,people是有人和没人的状态为rstn是清零,in_data是档位输入,q0到q4是公里数输入,qs、qm、qh是时钟输入,cost_lcd_in是费用输入,显示界面可以显示时间、行驶路程、速度、费用,由于程序数据转换太多,这里只给出一部分程序,后面的程序在附录。 LCD1602主要技术参数:显示容量:16×2个字符、芯片工作电压:4.5—5.5V、工作电流:2.0mA(5.0V)、模块最佳工作电压:5.0V、字符尺寸:2.95×4.35(W×H)mm。 图2-8 LCD1602模型图

编号 | 符号 | 引脚说明 | 编号 | 符号 | 引脚说明 | 1 | VSS | 电源地 | 9 | D2 | 数据 | 2 | VDD | 电源正极 | 10 | D3 | 数据 | 3 | VL | 液晶显示偏压 | 11 | D4 | 数据 | 4 | RS | 数据/命令选择 | 12 | D5 | 数据 | 5 | R/W | 读/写选择 | 13 | D6 | 数据 | 6 | E | 使能信号 | 14 | D7 | 数据 | 7 | D0 | 数据 | 15 | BLA | 背光源正极 | 8 | D1 | 数据 | 16 | BLK | 背光源负极 |

表1 引脚接口说明表

序号 | 指令 | RS | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 1 | 清显示 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 2 | 光标返回 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | * | 3 | 置输入模式 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | I/D | S | 4 | 显示开/关控制 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | D | C | B | 5 | 光标或字符移位 | 0 | 0 | 0 | 0 | 0 | 1 | S/C | R/L | * | * | 6 | 置功能 | 0 | 0 | 0 | 0 | 1 | DL | N | F | * | * | 7 | 置字符发生存贮器地址 | 0 | 0 | 0 | 1 | 字符发生存贮器地址 | 8 | 置数据存贮器地址 | 0 | 0 | 1 | 显示数据存贮器地址 | 9 | 读忙标志或地址 | 0 | 1 | BF | 计数器地址 | 10 | 写数到CGRAM或DDRAM) | 1 | 0 | 要写的数据内容 | 11 | 从CGRAM或DDRAM读数 | 1 | 1 | 读出的数据内容 |

表2 控制指令表 1602液晶模块的读写操作,屏幕和光标的操作都是通过指令编程来实现的。(说明1为高电平,0为低电平) 指令1:清显示,指令码01H,光标复位到地址00H位置 指令2:光标复位,光标返回到地址00H 指令3:光标和显示位置设置I/D,光标移动方向,高电平右移,低电平左移,S:屏幕上所有文字是否左移或右移,高电平表示有效,低电平表示无效。 指令4:显示开关控制。D:控制整体的显示开与关,高电平表示开显示,低电平表示关显示。C:控制光标的开与关,高电平表示有光标,低电平表示无光标 B:控制光标是否闪烁,高电平闪烁,低电平不闪烁。 指令5:光标或显示移位 S/C :高电平时显示移动的文字,低电平时移动光标 指令6:功能设置命令 DL:高电平时为4位总线,低电平时为8位总线 N:低电平时为单行显示,高电平时为双行显示,F:低电平时显示5X7的点阵字符,高电平时显示5X10的显示字符。 指令7:字符发生器RAM地址设置。 指令8:DDRAM地址设置。 指令9:读忙信号和光标地址 BF:忙标志位,高电平表示忙,此时模块不能接收命令或数据,如果为低电平表示不忙。 图2-9 LCD显示模块元件符号图 LCD显示模块程序: - module lcd1602(sys_clk ,

- sys_rstn ,

- lcd_rs ,

- lcd_rw ,

- lcd_en ,

- lcd_data ,

- in_data,

- q0,q1,q2,q3,q4,qs,qm,qh,people,

- cost_lcd_in

- ); //输入输出信号定义

- input [31:0] cost_lcd_in;

- input [7:0] q0,q1,q2,q3,q4,qs,qm,qh;

- input sys_clk ;//系统时钟输入

- input people, sys_rstn ;//系统复位信号,低电平有效

- input [3:0] in_data;

- output lcd_rs ;//lcd的寄存器选择输出信号

- output lcd_rw ;//lcd的读、写操作选择输出信号

- output lcd_en ;//lcd使能信号

- output [7:0] lcd_data ;//lcd的数据总线(不进行读操作,故为输出)

- reg lcd_rs ;

- reg clk_div ;

- reg [7:0] q1h,q1l,q2h,q2l,q3h,q3l,q4l;

- reg [7:0] sp_reg1,sp_reg2,sp_reg3;

- reg [7:0] qsl,qsh,qml,qmh,qhl,qhh;

- reg [7:0] in_data_reg;

- reg [7:0] cost_reg0,cost_reg1,cost_reg2,cost_reg3;

- reg [17:0] delay_cnt ;

- reg [7:0] lcd_data ;

- reg [4:0] char_cnt ;

- reg [7:0] data_disp ;

- reg [9:0] state ;

- parameter

- idle = 10'b000000000, //初始状态,下一个状态为CLEAR

- clear = 10'b000000001, //清屏

- set_function = 10'b000000010,

- switch_mode = 10'b000000100,

- set_mode = 10'b000001000,

- shift = 10'b000010000,

- //光标、画面位移设置:光标向左平移一个字符位

- set_ddram1 = 10'b000100000,

- //设置DDRAM的地址:第一行起始为0x00(注意输出时DB7一定要为1)

- set_ddram2 = 10'b001000000, //设置DDRAM的地址:第二行为0x40 write_ram1 = 10'b010000000, //数据写入DDRAM相应的地址

- write_ram2 = 10'b100000000; //数据写入DDRAM相应的地址

- assign lcd_rw = 1'b0; //没有读操作,R/W信号始终为低电平

- assign lcd_en = clk_div; //E信号出现高电平以及下降沿的时刻与LCD时钟相同 always@(posedge sys_clk or posedge sys_rstn) /////分频

- begin if(sys_rstn) begin delay_cnt<=18'd0; clk_div<=1'b0;

- end else if(delay_cnt==18'd200000)

- begin

- delay_cnt<=18'd0; clk_div<=~clk_div; end else

- begin delay_cnt<=delay_cnt+1'b1; clk_div<=clk_div;

- end end

- always@(posedge clk_div or posedge sys_rstn) //State Machine

- begin if(sys_rstn)

- begin state <= idle; lcd_data <= 8'b0; char_cnt <= 5'd0;

- lcd_rs<=1'b0;//地址\数据

- end else begin

- case(state)

- idle: begin //初始状态

- state <= clear; lcd_data <= 8'b0; end

- clear: begin //清屏

- state <= set_function;

- lcd_rs<=1'b0;

- lcd_data <= 8'b00000001;

- end

- set_function: //功能设置(38H):8位数据接口/2行显示/5*8点阵字符

- begin state <= switch_mode; lcd_rs<=1'b0;

- lcd_data <= 8'b00111000; end

- switch_mode: //显示开关控制(0CH):开显示,光标和闪烁关闭

- begin state <= set_mode; lcd_rs<=1'b0;

- lcd_data <= 8'b00001110; end

- set_mode:begin //输入方式设置(06H):数据读写操作后,地址自动加一/画面不动

- state <= shift; lcd_rs<=1'b0;

- lcd_data <= 8'b00000110; end

- shift: begin //光标、画面位移设置(10H):光标向左平移一个字符位

- //(光标显示是关闭的,所以实际上设置是看不出效果的)

- state <= set_ddram1; lcd_rs<=1'b0;

- lcd_data <= 8'b0001_0000; end

- set_ddram1: //设置DDRAM的地址:第一行起始为00H(注意输出时DB7一定要为1)

- begin state <= write_ram1;

- lcd_rs<=1'b0; lcd_data <= 8'b1000_0000;//Line1

- end

- set_ddram2: //设置DDRAM的地址:第二行为40H(DB7一定要为1)

- begin state <= write_ram2;

- lcd_rs<=1'b0; lcd_data <= 8'b1100_0000;//Line2

- end

- write_ram1:

- begin

- if(char_cnt <=5'd15)

- begin char_cnt <= char_cnt + 1'b1;

- lcd_rs<=1'b1; lcd_data <= data_disp;

- state <= write_ram1; end

- else begin state <= set_ddram2; end

- end

- write_ram2:

- begin

- if(char_cnt <=5'd30)

- begin char_cnt <= char_cnt + 1'b1;

- lcd_rs<=1'b1; lcd_data <= data_disp;

- state <= write_ram2; end

- else begin char_cnt <=5'd0; state <= shift; end

- end

- default: state <= idle;

- endcase

- end

- end

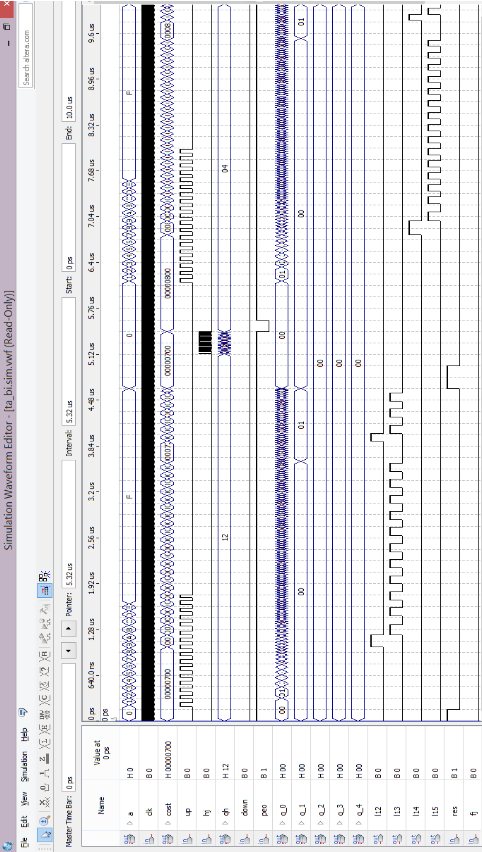

计费模块其中clk是20MHz输入,clrn清零,people是有人没人的状态位,q0到q4为里程输入,qh为小时输入,用于判断白天计程和夜间计费,其中又分0~2km不计程,2~10km加20%费用,且白天和夜间的四个计费阶段都有相对应的指示灯闪烁(L12到L15),白天:7元2km内7元,2km-10km每公里收费1.6元,10km以上每公里收费2.4元;夜间:起步价8元2km内8元,2km-10km每公里收费2元,10km以上每公里收费3元。cost_q输出费用。10km以上加收费用,1000个上升沿即为1米,则1km——1.6元,1000000个上升沿对应160分,1分即6250个上升沿,由于程序数据转换太多,这里只给出一部分程序,后面的程序在附录。 图2-10 计费模块元件符号图 计费模块程序: - module counter0_99_16(

- clk,clr,cost_q,people,

- q0,q1,q2,q3,q4,qh,

- l12,l13,l14,l15

- );

- input clk,clr,people;

- output reg l12,l13,l14,l15;

- input [7:0] q0,q1,q2,q3,q4,qh;

- output reg [31:0] cost_q;

- reg [13:0] n;

- reg one='b1;

- initial n=0;

- initial cost_q='b0000_0000_0000_0000_0000_1000_0000_0000;

- always@( posedge clk or posedge clr or negedge people )

- begin

- if(clr ) begin l12=0;l13=0;l14=0;l15=0;cost_q=0;end

- else

- begin if(!people) begin l12=0;l13=0;l14=0;l15=0;

- if(qh>'b00000110)cost_q='b0000_0000_0000_0000_0000_0111_0000_0000;

- else if(qh<='b00000110)cost_q='b0000_0000_0000_0000_0000_1000_0000_0000; end

- else

- begin

- if(qh>8'b00000110)

- begin

- if({q4,q3,q2,q0}<=32'b0000_0000_0001_0000_0000_0000_0000_0000

- && {q4,q3,q2,q0}>32'b0000_0000_0000_0010_0000_0000_0000_0000 ) begin

- //1000000电平除以160分,得出一分6250个上升沿

- if(n < 'd6250) //1.6元

- begin n=n+'d1; end

- if(n >= 'd6250)

- begin

- n<=0;

- begin

- l12=~l12;l13=0;l14=0;l15=0;

- cost_q = cost_q+1;

- if(cost_q[3:0] >= 10)

- begin cost_q[3:0] = 0;

- cost_q[7:4] = cost_q[7:4]+one;end

- if(cost_q[7:4] >= 10)

- begin cost_q[7:4] = 0;

- cost_q[11:8] = cost_q[11:8]+one;end

- if(cost_q[11:8] >= 10)

- begin cost_q[11:8] = 0;

- cost_q[15:12] = cost_q[15:12]+one;end

- if(cost_q[15:12] >= 10)

- begin cost_q[15:12] = 0;

- cost_q[19:16] = cost_q[19:16]+one;end

- if(cost_q[19:16] >= 10)

- begin cost_q[19:16] = 0;

- cost_q[23:20] = cost_q[23:20]+one;end

- if(cost_q[23:20] >= 10)

- begin cost_q[23:20] = 0;

- cost_q[27:24] = cost_q[27:24]+one;end

- if(cost_q[27:24] >= 10)

- begin cost_q[27:24] = 0;

- cost_q[31:28] = cost_q[31:28]+one;end

- end

- end

- end else

- end

- end

- end

- end

- endmodule

图2-11 计费模块仿真图 3 系统测试(调试)3.1 测试仪器与设备① EDA实验仪一台。 ② 计算机一台(装有Quartus Ⅱ软件) 3.2 性能指标测试把程序下载进实验箱,按键控制有人和没人的状态,蜂鸣器能正常播放音乐,然后运行计费器,通过计算的出的费用和路程相符合,白天和夜间的起步价、2km到10km计费标准和10km以上的计费标准都正确,且能显示正确的速度,时间,路程,四个收费阶段都有相对应的指示灯闪烁提示,速度的各档速也有相对应的灯点亮。 图3-1 引脚锁定

图3-2 白天计费测试图 图3-3 夜间计费测试图 3.3 结果分析达到了所要完成的基本功能,并在此功能上扩展出来,一些额外功能,在显示方面使用了LCD1602的液晶显示屏显示时间、速度、里程和费用,并有一个一天的计时器,且能够分为白天和夜间计费,并在人上车下车的时候能够用蜂鸣器播放音乐。 4 波形发生器设计波形发生器设计,能够产生锯齿波、三角波、方波和正弦波,采用LPM_ROM,储存四个波形的数字,然后直接输出波形的数据即可,并在此基础上采用两个按键控制四个频率的转换。 锯齿波ROM数据,从0自加到255。 三角波ROM数据:从0到127自加,每次加2,从128到255自减每次减2。 正弦波ROM数据:用正弦波发生函数。 正弦波数据C语言程序: #include <stdio.h> #include "math.h" main() { int i,k; for(i=0;i<256;i++) { k=128+128*sin(360.0*i/256.0*3.1415926/180); printf("%d : %d\n",i,k); } return 0; } 方波ROM数据:从0到127自加,为255,从128到255为0。 计数模块: 图4-1 计数器元件符号图 LPM_ROM模块: 图4-2 数据存储模块元件符号图

选择波形部分: 图4-3 选择波形元件符号图 选择波形的程序: module data_selector4_1 (A,B,C,D,s0,s1,z); input s0; input s1; input [7:0] A; input [7:0] B; input [7:0] C; input [7:0] D; output reg [7:0] z; always@( s0 or s1 or A or B or C or D) begin case ( {s1,s0} ) 'b00 : z=A; 'b01 : z=B; 'b10 : z=C; 'b11 : z=D; default : z='bz; endcase end endmodule 分频选择部分: 图4-4 选择频率元件符号图 分频选择程序: module clk_ch (key1,key2,clk,clk_c); input clk; input key1; input key2; output reg clk_c; reg [7:0]h; reg [7:0]y; always@( posedge clk ) begin case ({key2,key1}) 'b00:y=0; 'b01:y=2; 'b10:y=4; 'b11:y=6; endcase if(h == y) begin h<=0;clk_c<=~clk_c; end else begin h<=h+1;clk_c<=clk_c;end end endmodule 图4-5 波形发生器原理图 图4-6 Simulation的波形仿真图

方波 三角波 正弦波 锯齿波 图4-7 各波形图的嵌入式逻辑分析仪结果 图4-8 频率转换结果图 5 实训总结在做本次课程设计的过程中,我感触最深的当属查阅大量的设计资料了。为了让自己的设计更加完善,查阅这方面的设计资料是十分必要的,同时也是必不可少的。另外,这次课程设计让我感到了团队合作的重要性。在团队中,我们互帮互助,对整个课程设计来说,这是至关重要的,缺少每一个人都会对我们的设计产生影响。还有要感谢指导老师在我们遇到困难时,给予我们的建议与鼓励。一周的课程设计结束了,但是从中学到的知识会让我受益终身。发现、提出、分析、解决问题和实践能力的提高都会受益于我在以后的学习、工作和生活中。 为期一个星期的课程实训,在覃老师的亲切指导和同学的帮助下,此次设计才得以完成,在此向所有给予我此次课程设计指导和帮助的老师和同学表示最诚挚的感谢! 6 参考文献[1] 江国强,覃琴.EDA技术与应用(第5版):电子工业出版社,2017 [2]赵倩,叶波,林丽萍,周多,王晓华.Verilog数字系统设计与FPGA应用[M].北京:清华大学出版社,2012 [3]吴迪,杨梅,严飞.EDA与数字系统实验教程[M].大连:大连海事大学出版社,2011

附录总体原理图

总仿真图

LCD显示模块程序:

- module counter0_99_16(

- clk,clr,cost_q,people,

- q0,q1,q2,q3,q4,qh,

- l12,l13,l14,l15

- );

- input clk,clr,people;

- output reg l12,l13,l14,l15;

- input [7:0] q0,q1,q2,q3,q4,qh;

- output reg [31:0] cost_q;

- reg [13:0] n;

- reg one='b1;

- initial n=0;

- initial cost_q='b0000_0000_0000_0000_0000_0111_0000_0000;

- always@( posedge clk or posedge clr or negedge people )

- begin

- if(clr ) begin l12=0;l13=0;l14=0;l15=0;cost_q=0;cost_q='b0000_0000_0000_0000_0000_0111_0000_0000;end

- else

- begin if(!people) begin l12=0;l13=0;l14=0;l15=0;

- if(qh>'b00000110)cost_q='b0000_0000_0000_0000_0000_0111_0000_0000;

- else if(qh<='b00000110)cost_q='b0000_0000_0000_0000_0000_1000_0000_0000; end

- else

- begin

- if(qh>8'b00000110)

- begin

- if({q4,q3,q2,q0}<=32'b0000_0000_0001_0000_0000_0000_0000_0000

- && {q4,q3,q2,q0}>32'b0000_0000_0000_0010_0000_0000_0000_0000 ) begin//1000000电平除以160分,得出一分6250个上升沿

- if(n < 'd6250) //1.6元

- begin n=n+'d1; end

- if(n >= 'd6250)

- begin

- n<=0;

- begin

- l12=~l12;l13=0;l14=0;l15=0;

- cost_q = cost_q+1;

- if(cost_q[3:0] >= 10)

- begin cost_q[3:0] = 0;

- cost_q[7:4] = cost_q[7:4]+one;end

-

- if(cost_q[7:4] >= 10)

- begin cost_q[7:4] = 0;

- cost_q[11:8] = cost_q[11:8]+one;end

- if(cost_q[11:8] >= 10)

- begin cost_q[11:8] = 0;

- cost_q[15:12] = cost_q[15:12]+one;end

-

- if(cost_q[15:12] >= 10)

- begin cost_q[15:12] = 0;

- cost_q[19:16] = cost_q[19:16]+one;end

- if(cost_q[19:16] >= 10)

- begin cost_q[19:16] = 0;

- cost_q[23:20] = cost_q[23:20]+one;end

-

- if(cost_q[23:20] >= 10)

- begin cost_q[23:20] = 0;

- cost_q[27:24] = cost_q[27:24]+one;end

- if(cost_q[27:24] >= 10)

- begin cost_q[27:24] = 0;

- cost_q[31:28] = cost_q[31:28]+one;end

- end

- end

- end else

- if({q4,q3,q2,q0}>32'b0000_0000_0000_0010_0000_0000_0000_0000)

- begin//////////////2.4元

- if(n < 'd4166)

- begin n=n+'d1; end

- if(n >= 'd4166)

- begin

- n<=0;

- begin

- l12=0;l13=~l13;l14=0;l15=0;

- cost_q = cost_q+1;

- if(cost_q[3:0] >= 10)

- begin cost_q[3:0] = 0;

- cost_q[7:4] = cost_q[7:4]+one;end

-

- if(cost_q[7:4] >= 10)

- begin cost_q[7:4] = 0;

- cost_q[11:8] = cost_q[11:8]+one;end

- if(cost_q[11:8] >= 10)

- begin cost_q[11:8] = 0;

- cost_q[15:12] = cost_q[15:12]+one;end

-

- if(cost_q[15:12] >= 10)

- begin cost_q[15:12] = 0;

- cost_q[19:16] = cost_q[19:16]+one;end

- if(cost_q[19:16] >= 10)

- begin cost_q[19:16] = 0;

- cost_q[23:20] = cost_q[23:20]+one;end

- end

- end

- end

- else;

- end else

- if(qh<=8'b00000110)

- begin

- if({q4,q3,q2,q0}<=32'b0000_0000_0001_0000_0000_0000_0000_0000

- && {q4,q3,q2,q0}>32'b0000_0000_0000_0010_0000_0000_0000_0000)

- begin//////////////20

- if(n < 'd5000)

- begin n=n+'d1; end

- if(n>= 'd5000)

- begin

- n<=0;

- begin

- l12=0;l13=0;l14=~l14;l15=0;

- cost_q = cost_q+1;

- if(cost_q[3:0] >= 10)

- begin cost_q[3:0] = 0;

- cost_q[7:4] = cost_q[7:4]+one;end

-

- if(cost_q[7:4] >= 10)

- begin cost_q[7:4] = 0;

- cost_q[11:8] = cost_q[11:8]+one;end

- if(cost_q[11:8] >= 10)

- begin cost_q[11:8] = 0;

- cost_q[15:12] = cost_q[15:12]+one;end

-

- if(cost_q[15:12] >= 10)

- begin cost_q[15:12] = 0;

- cost_q[19:16] = cost_q[19:16]+one;end

- if(cost_q[19:16] >= 10)

- begin cost_q[19:16] = 0;

- cost_q[23:20] = cost_q[23:20]+one;end

- end

- end

- end else

- if({q4,q3,q2,q0}>32'b0000_0000_0000_0010_0000_0000_0000_0000)

- begin//////////////30

- if(n < 'd3333)

- begin n=n+'d1; end

- if(n >= 'd3333)

- begin

- n<=0;

- begin

- l12=0;l13=0;l14=0;l15=~l15;

- cost_q = cost_q+1;

- if(cost_q[3:0] >= 10)

- begin cost_q[3:0] = 0;

- cost_q[7:4] = cost_q[7:4]+one;end

-

- if(cost_q[7:4] >= 10)

- begin cost_q[7:4] = 0;

- cost_q[11:8] = cost_q[11:8]+one;end

- if(cost_q[11:8] >= 10)

- begin cost_q[11:8] = 0;

- cost_q[15:12] = cost_q[15:12]+one;end

-

- if(cost_q[15:12] >= 10)

- begin cost_q[15:12] = 0;

- cost_q[19:16] = cost_q[19:16]+one;end

- if(cost_q[19:16] >= 10)

- begin cost_q[19:16] = 0;

- cost_q[23:20] = cost_q[23:20]+one;end

- end

- end

- end

- else;

- end

- end

- end

- end

- endmodule

-

- 计费器模块程序:

- module lcd1602(sys_clk ,

- sys_rstn ,

- lcd_rs ,

- lcd_rw ,

- lcd_en ,

- lcd_data ,

- in_data,

- q0,q1,q2,q3,q4,qs,qm,qh,people,

- cost_lcd_in

- );

- input [31:0] cost_lcd_in;

- input [7:0] q0,q1,q2,q3,q4,qs,qm,qh;

- input sys_clk ;

- input people, sys_rstn ;

- input [3:0] in_data;

- output lcd_rs ;

- output lcd_rw ;

- output lcd_en ;

- output [7:0] lcd_data ;

- reg lcd_rs ;

- reg clk_div ;

- reg [7:0] q1h,q1l,q2h,q3h,q3l,q4l;

- reg [7:0] sp_reg1,sp_reg2,sp_reg3;

- reg [7:0] qsl,qsh,qml,qmh,qhl,qhh;

- reg [7:0] in_data_reg;

- reg [7:0] cost_reg0,cost_reg1,cost_reg2,cost_reg3;

- reg [17:0] delay_cnt ;

- reg [7:0] lcd_data ;

- reg [4:0] char_cnt ;

- reg [7:0] data_disp ;

- reg [9:0] state ;

- parameter

- idle = 10'b000000000,

- clear = 10'b000000001,

- set_function = 10'b000000010,

- switch_mode = 10'b000000100,

- set_mode = 10'b000001000,

- shift = 10'b000010000,

-

- set_ddram1 = 10'b000100000,

-

- set_ddram2 = 10'b001000000,

- write_ram1 = 10'b010000000,

- write_ram2 = 10'b100000000;

- assign lcd_rw = 1'b0;

- assign lcd_en = clk_div;

- always@(posedge sys_clk or posedge sys_rstn)

- begin if(sys_rstn) begin delay_cnt<=18'd0; clk_div<=1'b0;

- end else if(delay_cnt==18'd200000)

- begin

- delay_cnt<=18'd0; clk_div<=~clk_div; end else

- begin delay_cnt<=delay_cnt+1'b1; clk_div<=clk_div;

- end end

-

-

- always@(posedge clk_div or posedge sys_rstn)

- begin if(sys_rstn)

- begin state <= idle; lcd_data <= 8'b0; char_cnt <= 5'd0;

- lcd_rs<=1'b0;

- end else begin

-

- case(state)

-

- idle: begin

- state <= clear; lcd_data <= 8'b0; end

-

- clear: begin

- state <= set_function;

- lcd_rs<=1'b0;

- lcd_data <= 8'b00000001;

- end

- set_function:

- begin state <= switch_mode; lcd_rs<=1'b0;

- lcd_data <= 8'b00111000; end

-

- switch_mode:

- begin state <= set_mode; lcd_rs<=1'b0;

- lcd_data <= 8'b00001110; end

- set_mode:begin

- state <= shift; lcd_rs<=1'b0;

- lcd_data <= 8'b00000110; end

- shift: begin

-

- state <= set_ddram1; lcd_rs<=1'b0;

- lcd_data <= 8'b0001_0000; end

- set_ddram1:

- begin state <= write_ram1;

- lcd_rs<=1'b0; lcd_data <= 8'b1000_0000;

- end

- set_ddram2:

- begin state <= write_ram2;

- lcd_rs<=1'b0; lcd_data <= 8'b1100_0000;

- end

- write_ram1:

- begin

- if(char_cnt <=5'd15)

- begin char_cnt <= char_cnt + 1'b1;

- lcd_rs<=1'b1; lcd_data <= data_disp;

- state <= write_ram1; end

- else begin state <= set_ddram2; end

- end

- write_ram2:

- begin

- if(char_cnt <=5'd30)

- begin char_cnt <= char_cnt + 1'b1;

- lcd_rs<=1'b1; lcd_data <= data_disp;

- state <= write_ram2; end

- else begin char_cnt <=5'd0; state <= shift; end

- end

- default: state <= idle;

- endcase

- end

- end

- always @ (cost_lcd_in)

- begin

- if( people == 0) begin cost_reg0="0";

- cost_reg1="0";cost_reg2="0";cost_reg3="0"; end

- else

- case(cost_lcd_in[7:4])//显示金钱

- 'd0 : cost_reg0="0";

- 'd1 : cost_reg0="1";

- 'd2 : cost_reg0="2";

- 'd3 : cost_reg0="3";

- 'd4 : cost_reg0="4";

- 'd5 : cost_reg0="5";

- 'd6 : cost_reg0="6";

- 'd7 : cost_reg0="7";

- 'd8 : cost_reg0="8";

- 'd9 : cost_reg0="9";

- endcase

- case(cost_lcd_in[11:8])

- 'd0 : cost_reg1="0";

- 'd1 : cost_reg1="1";

- 'd2 : cost_reg1="2";

- 'd3 : cost_reg1="3";

- 'd4 : cost_reg1="4";

- 'd5 : cost_reg1="5";

- 'd6 : cost_reg1="6";

- 'd7 : cost_reg1="7";

- 'd8 : cost_reg1="8";

- 'd9 : cost_reg1="9";

-

- endcase

- case(cost_lcd_in[15:12])

- 'd0 : cost_reg2="0";

- 'd1 : cost_reg2="1";

- 'd2 : cost_reg2="2";

- 'd3 : cost_reg2="3";

- 'd4 : cost_reg2="4";

- 'd5 : cost_reg2="5";

- 'd6 : cost_reg2="6";

- 'd7 : cost_reg2="7";

- 'd8 : cost_reg2="8";

- 'd9 : cost_reg2="9";

-

- endcase

- case(cost_lcd_in[19:16])

- 'd0 : cost_reg3="0";

- 'd1 : cost_reg3="1";

- 'd2 : cost_reg3="2";

- 'd3 : cost_reg3="3";

- 'd4 : cost_reg3="4";

- 'd5 : cost_reg3="5";

- 'd6 : cost_reg3="6";

- 'd7 : cost_reg3="7";

- 'd8 : cost_reg3="8";

- 'd9 : cost_reg3="9";

-

- endcase

- end

- always @(qs or qm or qh )//实时时间

- begin

- case(qs[3:0])

- 'd0 : qsl="0";

- 'd1 : qsl="1";

- 'd2 : qsl="2";

- 'd3 : qsl="3";

- 'd4 : qsl="4";

- 'd5 : qsl="5";

- 'd6 : qsl="6";

- 'd7 : qsl="7";

- 'd8 : qsl="8";

- 'd9 : qsl="9";

- endcase

- case(qs[7:4])

- 'd0 : qsh="0";

- 'd1 : qsh="1";

- 'd2 : qsh="2";

- 'd3 : qsh="3";

- 'd4 : qsh="4";

- 'd5 : qsh="5";

- endcase

- case(qm[3:0])

- 'd0 : qml="0";

- 'd1 : qml="1";

- 'd2 : qml="2";

- 'd3 : qml="3";

- 'd4 : qml="4";

- 'd5 : qml="5";

- 'd6 : qml="6";

- 'd7 : qml="7";

- 'd8 : qml="8";

- 'd9 : qml="9";

- endcase

- case(qm[7:4])

- 'd0 : qmh="0";

- 'd1 : qmh="1";

- 'd2 : qmh="2";

- 'd3 : qmh="3";

- 'd4 : qmh="4";

- 'd5 : qmh="5";

- endcase

- case(qh[3:0])

- 'd0 : qhl="0";

- 'd1 : qhl="1";

- 'd2 : qhl="2";

- 'd4 : qhl="4";

- 'd5 : qhl="5";

- 'd6 : qhl="6";

- 'd7 : qhl="7";

- 'd8 : qhl="8";

- 'd9 : qhl="9";

- endcase

- case(qh[7:4])

- 'd0 : qhh="0";

- 'd1 : qhh="1";

- 'd2 : qhh="2";

- 'd3 : qhh="3";

- endcase

- end

-

-

-

- always@( people or q2 or q3 or q4)//公里显示寄存

- begin

- if( people == 0) begin q3l="0";q2h="0";q3h="0";q4l="00"; end

- else

- begin

- case(q2[7:4])

- 'd0 : q2h="0";

- 'd1 : q2h="1";

- 'd2 : q2h="2";

- 'd3 : q2h="3";

- 'd4 : q2h="4";

- 'd5 : q2h="5";

- 'd6 : q2h="6";

- 'd7 : q2h="7";

- 'd8 : q2h="8";

- 'd9 : q2h="9";

- endcase

- case(q3[3:0])

- 'd0 : q3l="0";

- 'd1 : q3l="1";

- 'd2 : q3l="2";

- 'd3 : q3l="3";

- 'd4 : q3l="4";

- 'd5 : q3l="5";

- 'd6 : q3l="6";

- 'd7 : q3l="7";

- 'd8 : q3l="8";

- 'd9 : q3l="9";

- endcase

- case(q3[7:4])

- 'd0 : q3h="0";

- 'd1 : q3h="1";

- 'd2 : q3h="2";

- 'd3 : q3h="3";

- 'd4 : q3h="4";

- 'd5 : q3h="5";

- 'd6 : q3h="6";

- 'd7 : q3h="7";

- 'd8 : q3h="8";

- 'd9 : q3h="9";

- endcase

- case(q4[3:0])

- 'd0 : q4l="0";

- 'd1 : q4l="1";

- 'd2 : q4l="2";

- 'd3 : q4l="3";

- 'd4 : q4l="4";

- 'd5 : q4l="5";

- 'd6 : q4l="6";

- 'd7 : q4l="7";

- 'd8 : q4l="8";

- 'd9 : q4l="9";

- endcase

- end

- end

- always @(in_data)//速度寄存

- begin

- if(people == 0)begin sp_reg2 ="0";sp_reg1="0"; end

- else

- begin

- case (in_data)

- 4'd0 : begin sp_reg2="0";sp_reg1="0";end

- 4'd1 : begin sp_reg2="0";sp_reg1="2";end

- 4'd2 : begin sp_reg2="0";sp_reg1="4";end

- 4'd3 : begin sp_reg2="0";sp_reg1="6";end

- 4'd4 : begin sp_reg2="0";sp_reg1="8";end

-

- 4'd5 : begin sp_reg2="1";sp_reg1="0";end

- 4'd6 : begin sp_reg2="1";sp_reg1="2";end

- 4'd7 : begin sp_reg2="1";sp_reg1="4";end

- 4'd8 : begin sp_reg2="1";sp_reg1="6";end

- 4'd9 : begin sp_reg2="1";sp_reg1="8";end

- 4'd10: begin sp_reg2="2";sp_reg1="0";end

- 4'd11: begin sp_reg2="2";sp_reg1="2";end

- 4'd12: begin sp_reg2="2";sp_reg1="4";end

- 4'd13: begin sp_reg2="2";sp_reg1="6";end

- 4'd14: begin sp_reg2="2";sp_reg1="8";end

- 4'd15: begin sp_reg2="3";sp_reg1="0";end

-

- endcase

- end

-

- end

-

- always @(char_cnt ) //输出的字符 有人坐车界面

- begin

- if(people)

- begin

- case (char_cnt)

- 5'd0: data_disp = qhh;

- 5'd1: data_disp = qhl;

- 5'd2: data_disp = ":";

- 5'd3: data_disp = qmh;

- 5'd4: data_disp = qml;

- 5'd5: data_disp = ":";

- 5'd6: data_disp = qsh;

- 5'd7: data_disp = qsl;

- 5'd8: data_disp = " ";

- 5'd9: data_disp = q4l;

- 5'd10: data_disp = q3h;

- 5'd11: data_disp = q3l;

- 5'd12: data_disp = ".";

- 5'd13: data_disp = q2h;

- 5'd14: data_disp = "k";

- 5'd15: data_disp = "m";

-

- 5'd16: data_disp = sp_reg2;

- 5'd17: data_disp = sp_reg1;

- 5'd18: data_disp = "0";

- 5'd19: data_disp = "k";

- 5'd20: data_disp = "m";

- 5'd21: data_disp = "/";

- 5'd22: data_disp = "h";

- 5'd23: data_disp = " ";

- 5'd24: data_disp = " ";

- 5'd25: data_disp = cost_reg3;

- 5'd26: data_disp = cost_reg2;

- 5'd27: data_disp = cost_reg1;

- 5'd28: data_disp = ".";

- 5'd29: data_disp = cost_reg0;

- 5'd30: data_disp = "[ DISCUZ_CODE_13 ]quot;;

- 5'd31: data_disp = "[ DISCUZ_CODE_13 ]quot;;

- default : data_disp =" ";

- endcase

- end

- else //没人坐车

- begin

- case (char_cnt)

- 5'd0: data_disp = qhh;

- 5'd1: data_disp = qhl;

- 5'd2: data_disp = ":";

- 5'd3: data_disp = qmh;

- 5'd4: data_disp = qml;

- 5'd5: data_disp = ":";

- 5'd6: data_disp = qsh;

- 5'd7: data_disp = qsl;

- 5'd8: data_disp = " ";

- 5'd9: data_disp = " ";

- 5'd10: data_disp = " ";

- 5'd11: data_disp = " ";

- 5'd12: data_disp = " ";

- 5'd13: data_disp = " ";

- 5'd14: data_disp = " ";

- 5'd15: data_disp = " ";

-

- 5'd16: data_disp = " ";

- 5'd17: data_disp = " ";

- 5'd18: data_disp = "E";

- 5'd19: data_disp = "m";

- 5'd20: data_disp = "p";

- 5'd21: data_disp = "t";

- 5'd22: data_disp = "y";

- 5'd23: data_disp = " ";

- 5'd24: data_disp = " ";

- 5'd25: data_disp = "c";

- 5'd26: data_disp = "a";

- 5'd27: data_disp = "r";

- 5'd28: data_disp = " ";

- 5'd29: data_disp = " ";

- 5'd30: data_disp = " ";

- 5'd31: data_disp = " ";

- default : data_disp =" ";

- endcase

- end

- end

- endmodule

-

全部资料51hei下载地址(源码+word格式完整的设计报告):

taxi_billing.7z

(7.71 MB, 下载次数: 244)

taxi_billing.7z

(7.71 MB, 下载次数: 244)

|