|

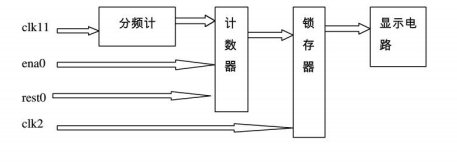

���� FPGA ���ֳ��ɱ�������У�Field Programmable Gate Array���ļ�ơ�FPGA�������俪��ϵͳ�ǿ������ģ���ּ��ɵ�·���¼����������ü����������ƣ����Ƴ�ʵ���û�����ԭ��ͼ���༭�������̻���Ӳ���������Եȷ�ʽ��Ϊ������룻Ȼ��һϵ��ת�������Զ����ֲ��ߡ�ģ�����Ĺ��̣������������FPGA�����������ļ�����FPGA������ʼ����������ʵ���������û�Ҫ���ר�ü��ɵ�·�������ﵽ���û�������ơ��������ƺ������������ɵ�·��Ŀ�ġ� FPGA��һ�ְ붨�Ƶļ��ɵ�·�����ص���ֱ�������û������м��������Ժ�ͨ���ԣ�����Ч�ʸߣ�Ӳ�����Ժ�ʵ�ֿ�ݣ������ɿ��Ժö��Ҽ���ά���� ���ŵ��Ӽ����ķ�չ�����ɵ�·�Ĺ�ģԽ��Խ���ӳ̶�ҲԽ��Խ�ߡ�������˴��ģ�ĺ��ӳ̶ȵĵ�·������⣬��ͳ���ż����������Եù�����������Թ�������VHDL���Ծ���ǿ��Ĺ��ܣ�������㣬��������ǿ�������ڴ��ż�����·��ֱ��ϵͳ����������������ۺϡ������Ҫ������VHDL���ԡ� VHDL��Ӣ��ȫ����Very-High-Speed Intergrated Circuit Hardware Description Language������1982�ꡣ1987��ף�VHDL��IEEE������������ȷ��Ϊ��Ӳ���������ԡ���IEEE������VHDL�ı��汾��IEEE-1076�����87�棩֮��EDA��˾����Ƴ����Լ���VHDL��ƻ������������Լ�����ƹ��߿��Ժ�VHDL�ӿڡ��˺�VHDL�ڵ����������õ��˹㷺�Ľ��ܣ�����ȡ����ԭ�еķDZ���Ӳ���������ԡ�1993�꣬IEEE��VHDL�����������Ӹ��ߵij����κ�ϵͳ������������չVHDL�����ݣ��������°汾��VHDL����IEEE����1076-1993�汾�����93�棩�����ڣ�VHDL��Verilog��ΪIEEE�Ĺ�ҵ��Ӳ���������ԣ��ֵõ��ڶ�EDA��˾��֧�֡��ڵ��ӹ��������ѳ�Ϊ��ʵ�ϵ�ͨ��Ӳ���������ԡ���ר����Ϊ�����µ������У�VHDL��Verilog���Խ��е���ֵ�����ϵͳ�������VHDL��Ҫ������������ϵͳ�Ľṹ����Ϊ�����ܺͽӿڡ����˺����������Ӳ������������⣬VHDL��������ʽ�����������䷨��ʮ��������һ��ļ���������ԡ�VHDL�ij���ṹ�ص��ǽ�һ�����ơ���������ʵ�壨������һ��Ԫ����һ����·ģ���һ��ϵͳ���ֳ��ⲿ����ƿ��Ӳ��֣����˿ڣ����ڲ�����Ʋ����Ӳ��֣��������ʵ����ڲ����ܺ��㷨��ɲ��֡��ڶ�һ�����ʵ�嶨�����ⲿ�����һ�����ڲ�������ɺ���������ƾͿ���ֱ�ӵ������ʵ�塣���ֽ����ʵ��ֳ����ⲿ�ֵĸ�����VHDLϵͳ��ƵĻ����㡣 Quartus II��Altera��˾�Ƴ���CPLD/FPGA���ɻ������������������������롢���ۺϡ������벼�ߡ����桢ʱ�������Ӳ������������PLD������̡�Quartus���ṩ�˶���������뷽ʽ�����ٵı����ֱ������������̡������Ѻõ��û����棬 ���ٵ��ۺ��ٶȺ��Ż����ۺϺ����书�ܡ�Quartus II�Դ��깦��ģ��⣬���������û��Ĺ��������ӿ�����ٶȡ�Quartus II ���÷����������ڹ����з����κ���ơ��ɽ��й��ܷ��桢ʱ�������������Ƶ������ܺͼ�����Ƶ��ڲ���ʱ�Ƿ������ơ����������Է���������ƣ��������Ƶ��κβ��֡�֧�ֿɱ��ϵͳ��SOPC���ʹ��ģFPGA��ƿ�������ϵͳ����ơ�Ƕ��ʽ�����������ɱ���������һ�壬��һ���ۺ��ԵĿ���ƽ̨�� ������֧��Altera��˾��Stratix ��Stratix GX��Stratix��MAX3000A��MAX 7000B��MAX 7000AE��MAX ��FLEX6000��FLEX10Kϵ�С�Cyclone��Cyclone��APEX ��APEX20K��ACEX1Kϵ�С� 1 ������Ʒ��� ��ƻ���FPGA�ļ�������Ҫ����ʾ1��0-9999����λ��������������4��ģ��Ϊ10��ʮ���Ƽ������������ɣ����Կ�����ʾ��Ƶ�ʷ�Χ��1-9999HZ�����Ƶ�ʼƵĹ��ָܷ���ĸ�ģ�飺��Ƶ�ơ��������������������������ʾ��·������ģ�����VHDL������������Quartus����з��档����Ʋ������ط�Ƶ�ƿ��Զ��ź�ʵ�ֲ�ͬ��Ƶ������ź���Ϊ���������롣��������һ���ⲿ������ƿ��Կ�����ʾ������ʾ���ڡ���ϵͳ��������ʱ�������źű��ṩƵ�ʣ�������Ƶ����Ƶ�����������ź����������ģ�飬����ģ������������������м���������������������������У���֤ϵͳ�����ȶ���ʾ���ݣ���������ܹ���ʾ���߶�������ʾ���ϡ�

ͼ1-1������Ʒ��� 2������ģ����Ƽ����� 2.1��Ƶ������� 2.1.1��Ƶ�����ԭ�� Ƕ��ʽ�豸Ʒ�ַ���������ܲ���Ҳʮ�־���ЩǶ��ʽ�豸��VoIP�绰���ij���ϵͳ���Ļ����еȣ��������ǵ�����һ�����ܼ���˼��������ʹ洢�ռ䶼�����ޡ�������Щ�豸������ֲ��Ȼ�Dz���ʵ�ġ���ˣ���Ƕ��ʽ�豸��ѡ���ϣ�����Ŀ����ֲ��Ŀ���豸��λ�ھ���һ�����������ʹ洢�ռ���и߶�Ƕ��ʽ�豸�ϡ��Ƚ��д����Ե�Ƕ��ʽ�豸�������и߶�PDA���и߶����ܵ绰���и߶˻����еȡ����⣬Ϊ�˼ӿ���ֲ���ٶȣ����̿������ڣ���ˣ���Ƕ��ʽ�豸��Ӳ��ƽ̨ѡ��ΪX86��ϵ�ṹ��Ӳ��ƽ̨������������·����У���Ƶ����һ�ֻ�����·��ͨ����Ƶ���Եõ���Ҫ��ʱ��Ƶ�ʡ������ķ�Ƶ���ж����Ʒ�Ƶ����ż���η�Ƶ���������η�Ƶ����ռ�ձȿɵ��ķ�Ƶ����С����Ƶ������Ƶ�ķ����ܶ�����ľ������üӷ�����ʱ���źŽ��з�Ƶ����ȻҲ��������һЩר�õĵ�·�ṹ��ʵ�֡� ���ط�Ƶ���Ĺ�����������˸�����ͬ����ʱ�����������ʱ���ź��в�ͬ�ķ�Ƶ�ȣ�����һ��N��Ƶ������Ƶ����ʱ��������ԭʱ�����ڵ�N����Ƶ�ʱ�Ϊԭ����1/N������һ��8λ�����������������D��Ȼ��������������������D����ʱ�����ڼ��������ʱ�����full��Ϊ�ߵ�ƽ������fullΪ�����źţ���fout����ȡ�����������N=2D������һ�κ������¼�������������ֱ�����뱻������ֵ���������ط�Ƶ������װ�ز�ͬ�ļ�����ʼֵʱ�����в�ͬƵ�ʵ�����źţ��Ӷ��õ���ͬ����������ط�Ƶ�������ü���ֵ�ɲ���Ԥ�õļӷ������������ɵġ� 2.1.2Դ�����η��� module clk_gen (clk_33m, //system input clock; rst, //system reset; clk_1, //output 1hz clock clk_8, //output 8hz clock clk_16, //output 16hz clock clk_32, //output 32hz clock clk_32k); //output 32khz clock

input clk_33m,rst; output clk_1,clk_8,clk_16,clk_32,clk_32k;

wire clk_33m,rst; reg [24:0] count; wire clk_32k,clk_1,clk_8,clk_16,clk_32;

//************* clock generator****************************

always @(posedge clk_33m or negedge rst) if (!rst) count<=25'd0; else count<=count+1'b1;

assign clk_1=count[24]; assign clk_32k=count[9]; assign clk_8=count[21]; assign clk_16=count[20]; assign clk_32=count[19];

endmodule

ͼ2-1 ��Ƶ��ʱ�����

2.1.3��Ƶ��RTL ��·ͼ

ͼ2-2 ��Ƶ��RTL��·ͼ 2.2����������� 2.2.1��Ƶ�����ԭ�� ������һ������������㣬����������ʵ���������������·��������������ϵͳ����Ҫ�Ƕ�����ĸ������м�������ʵ�ֲ����������Ϳ��ƵĹ��ܣ�ͬʱ���з�Ƶ���ܣ����������ɻ����ļ�����Ԫ��һЩ����������ɣ�������Ԫ����һϵ�о��д洢��Ϣ���ܵĸ��ഥ�������ɣ���Щ��������RS��������T��������D��������JK�������ȡ�������������ϵͳ��Ӧ�ù㷺�����ڵ��Ӽ�����Ŀ������ж�ָ���ַ���м������Ա�˳��ȡ����һ��ָ��������������˷�����������ʱ���¼ӷ����������������������������ж�����ļ����ȵȡ�����������������ʾ��Ʒ�Ĺ���״̬��һ����˵��Ҫ��������ʾ��Ʒ�Ѿ�����˶��ٷݵ���ҳ��ҳ����������Ҫ��ָ�����ڼ�������λ������������3λ��4λ�ġ�����Ȼ��3λ���ļ�������������ʾ��999��4λ������������ʾ��9999�������ֵ��Ӽ�����Ӧ�õ�����ʱ������·�����������������ڶ�ʱ��������������������ڷ�Ƶ����ʱ������������������������Լ�������������ȡ����Dz�����ʾ��������һ�㶼��Ҫͨ�����LCD��LED��������ʾ�� 2.2.2��ʮ���Ƽ����� odule COUNT_60 (clk, //count input clock; rst, //system reset; rco, //carry output q); //BCD code output

input clk,rst; output reg rco; output [6:0] q;

wire clk,rst; reg [6:0] q; reg en;

//*********************************************************

always @(posedge clk or negedge rst)

if (!rst) q[3:0]<=4'd0; else if(q[3:0]==4'd8) begin q[3:0]<=q[3:0]+1'b1; en<=1'b1; end else if (q[3:0]==4'd9) begin q[3:0]<=4'd0; en<=1'b0; end else begin q[3:0]<=q[3:0]+1'b1; en<=1'b0; end

always @(posedge clk or negedge rst)

if (!rst) q[6:4]<=3'd0; else if (en) begin if (q[6:4]==3'd5) begin q[6:4]<=3'd0; rco<=1'b1; end else begin q[6:4]<=q[6:4]+1'b1; rco<=1'b0; end end else ;

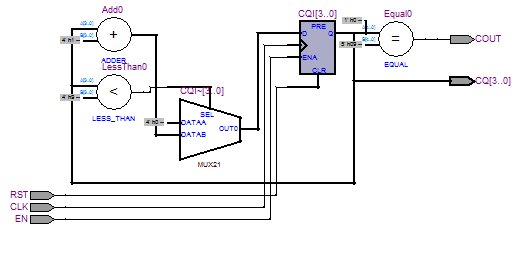

Endmodule 2.2.3RTL��·ͼ

ͼ2-3��ʮ���Ƽ�����RTL��·ͼ 2.3�����������2.3.1���������ԭ����ν����������������˵�״̬����������˵�״̬�仯���仯�������������ź�ʱ�����״̬�����浽�����ֱ����һ�������źŵ���ʱ�Ÿı䡣���͵�����������·��D ��������·����LED���������ʾ���棬Ҫά��һ�����ݵ���ʾ������Ҫ�����Ŀ��ٵ�ˢ�¡����������Ķΰ�λ����ܵ���ЩҪѡͨ����ʾ�豸�ϡ��������ܹ����ܵ�ˢ��Ƶ��֮�ڣ����ÿ��ʮ�����Ҫˢ��һ�Ρ���ʹ��ռ���˴������Ĵ���ʱ�䣬�����˴������Ĵ������������˷��˴������Ĺ��ġ���������ʹ�ÿ��Դ��Ļ���������ⷽ���ѹ�����������������ݴ��䵽�������������������������������ű��һֱ��������״ֱ̬����һ�������µ�����Ϊֹ������������ܵ���ʾ���ݲ���֮ǰ���������Ĵ���ʱ���IO���ű�����ͷš����Կ�����������������ʱ���������ʾ���ݷ����仯��ʱ������������ʾʱ����ֻ�Ƿdz��ٵ�һ�����֡����������ڴ����������и����ʱ����ִ�������������������������LED���������ʾ���������:��ʡ�˱����MCUʱ�䡣

2.3.2������Դ�����η��� module sem_drive (oSEG0, oSEG1, oSEG2, oSEG3, oSEG4, oSEG5, oSEG6, oSEG7, //output to 8 SEG iDIG ); //input 8-BCD code (4*8=32bit) input [31:0] iDIG; output [6:0] oSEG0,oSEG1,oSEG2,oSEG3,oSEG4,oSEG5,oSEG6,oSEG7;

wire [31:0] iDIG; wire [6:0] oSEG0,oSEG1,oSEG2,oSEG3,oSEG4,oSEG5,oSEG6,oSEG7;

SEG7_LUT U0 (.oSEG(oSEG0),.iDIG(iDIG[3:0])); SEG7_LUT U1 (.oSEG(oSEG1),.iDIG(iDIG[7:4])); SEG7_LUT U2 (.oSEG(oSEG2),.iDIG(iDIG[11:8])); SEG7_LUT U3 (.oSEG(oSEG3),.iDIG(iDIG[15:12])); SEG7_LUT U4 (.oSEG(oSEG4),.iDIG(iDIG[19:16])); SEG7_LUT U5 (.oSEG(oSEG5),.iDIG(iDIG[23:20])); SEG7_LUT U6 (.oSEG(oSEG6),.iDIG(iDIG[27:24])); SEG7_LUT U7 (.oSEG(oSEG7),.iDIG(iDIG[31:28]));

Endmodule ͼ2-4 ������ʱ�����ͼ 2.2.3������RTL ��·ͼ ͼ2-5 ������RTL��·ͼ 2.4��ʾ���ֵ���� 2.4.1�߶��������ʾԭ�� �����˻�����ʽ��Ƭ��ϵͳ��˵��������Ҫ��Ӧ�û����룬ͬʱҲ��Ҫ��һЩ�����Ϣ�����ʾ����Щ��ʾ��Ϣ�����ṩʵʱ�����ݻ�ͼ�ν�����Ա�������ϵͳ��״̬�����з���������Ŀǰ����õ���LED�������ʾ����ɱ�������ʹ�ü�㣬������ʾ���ֻ��ض����ַ������������ܵ�һ���ǰ뵼�巢������������ܿɷ�Ϊ�߶�����ܺͰ˶�����ܣ��������ڰ˶�����ܱ��߶�����ܶ�һ����������ܵ�Ԫ���������Ԫ�Ƿ�������ܡ������ͨ�����䲻ͬ�Ĺܽ�������Եĵ�����ʹ�䷢�����Ӷ���ʾ�������ܹ���ʾʱ�䡢���ڡ��¶ȵ����п������ֱ�ʾ�IJ������������ڵ����ر��Ǽҵ�����Ӧ�ü�Ϊ�㷺������ʾ�����յ�����ˮ��������ȵȡ����������ˮ���õĶ�������ܣ������ҵ�Ҳ��Һ������ӫ������ 2.4.2�߶��������ʾԴ�����η���module SEG7_LUT (oSEG, //output SEG7 code iDIG); //input BCD code input [3:0] iDIG; output [6:0] oSEG; reg [6:0] oSEG;

// --a-- // | | // f b // | | // --g-- // | | // e c // | | // --d-- O DP

always @(iDIG) case(iDIG) //gfedcba 4'h0: oSEG = 7'b1000000; //display 0; 4'h1: oSEG = 7'b1111001; //display 1; 4'h2: oSEG = 7'b0100100; //display 2; 4'h3: oSEG = 7'b0110000; //display 3; 4'h4: oSEG = 7'b0011001; //display 4; 4'h5: oSEG = 7'b0010010; //display 5; 4'h6: oSEG = 7'b0000010; //display 6; 4'h7: oSEG = 7'b1111000; //display 7; 4'h8: oSEG = 7'b0000000; //display 8; 4'h9: oSEG = 7'b0010000; //display 9; // 4'ha: oSEG = 7'b0001000; //display A; 4'ha: oSEG = 7'b0111111; //display - for clock; 4'hb: oSEG = 7'b0000011; //display B; 4'hc: oSEG = 7'b1000110; //display C; 4'hd: oSEG = 7'b0100001; //display D; 4'he: oSEG = 7'b0000110; //display E; 4'hf: oSEG = 7'b0001110; //display F; endcase

Endmodule 3ϵͳ������� 3.1�Զ����µ���Ʒ��� ��ν�Զ�������Ʒ���,���Dz��ÿ���ȫ������оƬ���̼����Ʒ�ṹ��������,�ڹ��ܼ�����Ʋ�Ʒ���ж���,����Ϲ��ܷ��漼��,��ȷ����Ƶ���ȷ��,�ܶ�����ɺ�,�������ۺϼ���,�ѹ�������ת����ijһ����ṹоƬ�������ļ�,��������̵IJ��ֲ��������в��ֲ��ߡ����ֲ��߽�����ɷ����ͬһ������,���а������ܺ�ʱ��ĺ���֤,�Ա�֤���ֲ���������������ʱ������ʱ����Ӱ����Ƶ����ܡ� �Զ�������Ʒ�������Խ�����Զ����ġ�����,���ڹ�����������ȫ������оƬ�ṹ,����Ƶ������,���ʦ�ɲ���оƬ�ṹ��Լ��,���о������в�Ʒ���,�����˴�ͳ��Ʒ�������������������Ʒ���,���������������ڡ����,��Ƶ������õõ���֤��Ŀǰ�ĵ��Ӳ�Ʒ����ģ�黯��չ����νģ�黯���Ƕ�������Ƴɹ�������,��Ϻ�������,����ȫ�µĻ��������,���Զ�������Ʒ����Ĺ�����������оƬ�ṹ�ء���˿�����һ��IP�ķ�ʽ���д浵,�Ա㽫�����������á� ����,��ƹ�ģ�����ߡ�����������������ɸ��ӵĹ���,������Ҫ�ֹ���ͼ�����ģ�оƬѡ����������ʦ���ڽ϶̵�ʱ���ڲ��ø��ֽṹоƬ�����ͬһ��������,�Ӷ�����ƹ�ģ���ٶȡ�оƬ�۸�ϵͳ����Ҫ��ȷ������ƽ��,ѡ����ѽ���� 3.2�������Դ��������沨�� module sem_drive (oSEG0, oSEG1, oSEG2, oSEG3, oSEG4, oSEG5, oSEG6, oSEG7, //output to 8 SEG iDIG ); //input 8-BCD code (4*8=32bit) input [31:0] iDIG; output [6:0] oSEG0,oSEG1,oSEG2,oSEG3,oSEG4,oSEG5,oSEG6,oSEG7;

wire [31:0] iDIG; wire [6:0] oSEG0,oSEG1,oSEG2,oSEG3,oSEG4,oSEG5,oSEG6,oSEG7;

SEG7_LUT U0 (.oSEG(oSEG0),.iDIG(iDIG[3:0])); SEG7_LUT U1 (.oSEG(oSEG1),.iDIG(iDIG[7:4])); SEG7_LUT U2 (.oSEG(oSEG2),.iDIG(iDIG[11:8])); SEG7_LUT U3 (.oSEG(oSEG3),.iDIG(iDIG[15:12])); SEG7_LUT U4 (.oSEG(oSEG4),.iDIG(iDIG[19:16])); SEG7_LUT U5 (.oSEG(oSEG5),.iDIG(iDIG[23:20])); SEG7_LUT U6 (.oSEG(oSEG6),.iDIG(iDIG[27:24])); SEG7_LUT U7 (.oSEG(oSEG7),.iDIG(iDIG[31:28]));

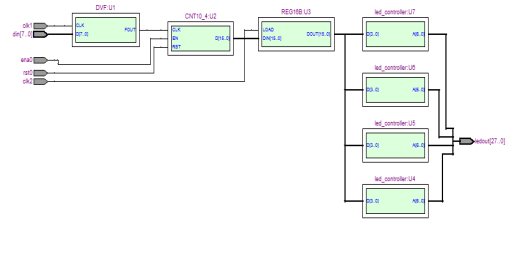

endmodule 3.2.1ϵͳ����RTL ��·ͼ

ͼ3-1ϵͳ����RTL ��·ͼ 4�ܽ� ���������������˺ܶ�ʵ���Ե����⣬��ʵ������вŷ��֣��鱾�������ԵĶ�������ʵ�������еĻ�����һ���ij���ģ�������Щ���ⲻ��Ҫ��������⣬����Ҫ���ϵظ�����ǰ�Ĵ���˼ά��һ���������Ҫ���Լ�һ��һ�εĽ�������ڽ���Ĺ��̵�����ᷢ���Լ��ڷ��ٵ����������ڽ̲Ĺ���ϵͳ��������DZȽϼģ���Ҫ�ǽ����������е����⣬�����������һ�������Ķ���������ӳ�������������˼ά�ʹ���������������һ����Ƶ�������ڡ������������ƹ����д�ʱ�������ڳ�������ġ��ܶ��ӳ����ǿ��Խ���鱾�ϵģ��������νӸ����ӳ�����ǹؼ����������ڣ�����Ҫ��ϵͳ�Ľṹ����Ϥ��ͨ����������Ҳ�������������ڵIJ���֮������Ȼ�о��������Ѿ����գ��������õ�ʵ���Ĺ������������벻����������һ��Ŭ���ŵ��Խ����

������Word��ʽ�ĵ�51�����ص�ַ��

Ф��ȫ20125024033.doc

(422 KB, ���ش���: 17)

Ф��ȫ20125024033.doc

(422 KB, ���ش���: 17)

|

����ԱQQ:125739409;��������QQȺ281945664

����ԱQQ:125739409;��������QQȺ281945664