ФПТМ

вЛЁЂ ЩшМЦШЮЮёгывЊЧѓ 3

ЖўЁЂЩшМЦЫМТЗ 4

1.1ЩшМЦЗНАИ 4

1.2ЩшМЦвЊЕу 4

1.3ЙЄзїдРэ 4

Ш§ЁЂГЬађдЫааМАНсЙћ 5

ЃЈ1ЃЉЗжЦЕФЃПщ 5

ЃЈ2ЃЉУыФЃПщ 6

ЃЈ3ЃЉЗжФЃПщЃЈminuteЃЉ 8

ЃЈ4ЃЉЪБФЃПщЃЈhourЃЉ 10

ЃЈ5ЃЉЪ§ТыЯдЪОЧ§ЖЏФЃПщ 12

(6)ЦЌбЁФЃПщЃЈsellЃЉ 13

(7)выТыЯдЪОФЃПщ(display) 14

ЃЈ8ЃЉБЈЪБФЃПщЃЈalartЃЉ 15

ЃЈ9ЃЉСљНјжЦМЦЪ§ЦїФЃПщЃЈcnt6ЃЉ 16

ЃЈ10ЃЉСНЪфШыгыФЃПщЃЈand2aЃЉ 17

ЃЈ11ЃЉСНЪфШыЛђФЃПщ(or2a) 18

ЫФЁЂЖЅВуЕчТЗЩшМЦМАЗТецНсЙћгыЗжЮі 19

ЮхЁЂаФЕУЬхЛс 22

СљЁЂВЮПМЮФЯз 23

ЦпЁЂ дДГЬађ 23

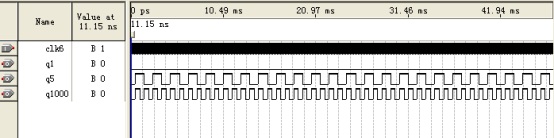

еЊвЊЃКНќФъРДЫцзХЪ§зжММЪѕЕФбИЫйЗЂеЙЃЌИїжжжаЁЂДѓЙцФЃМЏГЩЕчТЗдкЪ§зжЯЕЭГЁЂПижЦЯЕЭГЁЂаХКХДІРэЕШЗНУцЖМЕУЕНСЫЙуЗКЕФгІгУЁЃетОЭЦШЧавЊЧѓРэЙЄПЦДѓбЇЩњЪьЯЄКЭеЦЮеГЃгУжаЁЂДѓЙцФЃМЏГЩЕчТЗЙІФмМАЦфдкЪЕМЪжаЕФгІгУЗНЗЈЃЌГ§ЭЈЙ§ЪЕбщНЬбЇХрбјЪ§зжЕчТЗЕФЛљБОЪЕбщЗНЗЈЁЂЗжЮіЮЪЬтКЭЙЪеЯМьВщЗНЗЈвдМАЫЋзйЪОВЈЦїЕШГЃгУвЧЦїЪЙгУЗНЗЈЕШЛљБОЕчТЗЕФЛљБОЪЕбщММФмЭтЃЌЛЙБиаыХрбјДѓбЇЩњЙЄГЬЩшМЦКЭзщжЏЪЕбщФмСІЁЃ

БОДЮЩшМЦЕФФПЕФдкгкХрбјбЇЩњЖдЛљБОЕчТЗЕФгІгУКЭеЦЮеЃЌЪЙбЇЩњдкЪЕбщдРэЕФжИЕМЯТЃЌГѕВНОпБИЛљБОЕчТЗЕФЗжЮіКЭЩшМЦФмСІЃЌВЂеЦЮеЦфгІгУЗНЗЈЃЛздааФтЖЈЪЕбщВНжшЃЌМьВщКЭХХГ§ЙЪеЯ ЁЂЗжЮіКЭДІРэЪЕбщНсЙћМАзЋаДЪЕбщБЈИцЕФФмСІЁЃзлКЯЪЕбщЕФЩшМЦФПЕФЪЧХрбјбЇЩњГѕВНеЦЮеаЁаЭЪ§зжЯЕЭГЕФЩшМЦФмСІЃЌАќРЈбЁдёЩшМЦЗНАИЃЌНјааЕчТЗЩшМЦЁЂАВзАЁЂЕїЪдЕШЛЗНкЃЌдЫгУЫљбЇжЊЪЖНјааЙЄГЬЩшМЦЁЂЬсИпЪЕбщММФмЕФЪЕМљЁЃЪ§зжЕчзгжгЪЧвЛжжМЦЪБзАжУЃЌЫќОпгаЪБЁЂЗжЁЂУыМЦЪБЙІФмКЭЯдЪОЪБМфЙІФмЃЛОпгаећЕуБЈЪБЙІФмЁЃ БОДЮЩшМЦЮвВщдФСЫДѓСПЕФЮФЯззЪСЯЃЌбЇЕНСЫКмЖрЙигкЪ§зжЕчТЗЗНУцЕФжЊЪЖЃЌВЂЧвИќМгЙЎЙЬКЭеЦЮеСЫПЮЬУЩЯЫљбЇЕФПЮБОжЊЪЖЃЌЪЙздМКЖдЪ§зжЕчзгММЪѕгаСЫИќНјвЛВНЕФШЯЪЖКЭСЫНтЁЃ ЛљБОЙІФмЃКФмНјаае§ГЃЕФЪБЁЂЗжЁЂУыМЦЪБЙІФмЃЌЗжБ№гЩ6ИіЪ§ТыЙмЯдЪО24аЁЪБЃЌ60ЗжжгЃЌ60УыжгЕФМЦЪ§ЦїЯдЪОЁЃ ИНМгЙІФмЃК1ЃЉФмРћгУгВМўВПЗжАДМќЪЕЯжЁАаЃЪБЁБЁАаЃЗжЁБЁАЧхСуЁБЙІФмЃЛ 2ЃЉФмРћгУЗфУљЦїзіећЕуБЈЪБЃКЕБМЦЪБЕНДя59ЁЏ59ЁЏЁЏЪБПЊЪМБЈЪБЃЌУљНаЪБМф1УыжгЃЛ 3ЃЉЖЈЪБФжСхЃКБОЩшМЦжаЩшжУЕФЪЧдкЦпЕуЪБНјааФжжгЙІФмЃЌУљНаЙ§ГЬжаЃЌФмЙЛНјаажаЖЯФжСхЙЄзїЁЃ ЖўЁЂЩшМЦЫМТЗ 1.1ЩшМЦЗНАИ 1ЁЂЪБжгЙІФмЃЌОпгаЯдЪОЪБЁЂЗжЁЂУыЕФЙІФмЃЛ 2ЁЂОпгаећЕуБЈЪБЙІФмЃЌдкећЕуЪБЪЙгУЗфУљЦїНјааБЈЪБЃЌОпгаФжжгЙІФмЃЌУљНаЙ§ГЬжаЃЌОпгажаЖЯФжСхЙІФмЁЃ 1.2ЩшМЦвЊЕу Ъ§зжжгвЛАуЪЧгЩеёЕДЦїЁЂЗжЦЕЦїЁЂМЦЪ§ЦїЁЂвыТыЦїЁЂЯдЪОЦїЕШМИВПЗжзщГЩЁЃетаЉЖМЪЧЪ§зжЕчТЗжагІгУзюЙуЗКЕФЛљБОЕчТЗЃЌБОЩшМЦЗжФЃПщЩшМЦЪЕЯжИїВПЗжЙІФмЃЌВЩгУШэМўБрГЬПижЦFPGAаОЦЌФкВПВњЩњеёЖЏжмЦкЮЊ1sЕФТіГхЁЃВЂНЋаХКХЫЭШыМЦЪ§ЦїНјааМЦЫуЃЌВЂАбРлМгЕФНсЙћвдЁАЪБЁБЁЂЁАЗжЁБЁЂЁАУыЁБЕФЪ§зжЯдЪОГіРДЁЃЁАУыЁБЕФЯдЪОгЩСНМЖМЦЪ§ЦїКЭвыТыЦїзщГЩЕФСљЪЎНјжЦМЦЪ§ЕчТЗЪЕЯжЃЛЁАЗжЁБЕФЯдЪОЕчТЗЁАУыЁБЯрЭЌЃЌЁАЪБЁБЕФЯдЪОгЩСНМЖМЦЪ§ЦїКЭвыТыЦїзщГЩЕФЖўЪЎЫФНјжЦЕчТЗРДЪЕЯжЁЃЫљгаМЦЪБНсЙћгЩСљЮЛЪ§ТыЙмЯдЪОЁЃ 1.3ЙЄзїдРэ Ъ§зжЕчзгжггЩеёЕДЦїЁЂЗжЦЕЦї МЦЪ§ЦїЁЂвыТыЯдЪОЁЂБЈЪБЕШЕчТЗзщГЩЁЃеёЕДЦїВњЩњЮШЖЈЕФИпЦЕТіГхаХКХЃЌзїЮЊЪ§зжжгЕФЪБМфЛљзМЃЌШЛКѓОЙ§ЗжЦЕЦїЪфГіБъзМУыТіГхЁЃУыМЦЪ§ЦїТњ60КѓЯђЗжМЦЪ§ЦїНјЮЛЃЌЗжМЦЪ§ЦїТњ60КѓЯђаЁЪБМЦЪ§ЦїНјЮЛЃЌаЁЪБМЦЪ§ЦїАДееЁА24З1ЁБЙцТЩМЦЪ§ЁЃМЦТњКѓИїМЦЪ§ЦїЧхСуЃЌжиаТМЦЪ§ЁЃМЦЪ§ЦїЕФЪфГіЗжБ№ОвыТыЦїЫЭЪ§ТыЙмЯдЪОЃЌМЦЪБГіЯжЮѓВюЪБЃЌПЩвдгУаЃЪБЕчТЗЁАаЃЪБЁБЁАаЃЗжЁБЁАЧхСуЁБЁЃУыТіГхПЩвдЭЈЙ§ЗжЦЕЕчТЗЕУЕНЁЃЭЈЙ§БЈЪБЩшМЦФЃПщПЩвдЪЕЯжећЕуБЈЪБМАЖЈЪБФжСхЃЌвыТыЯдЪОгЩЦпЖЮвыТыЦїЭъГЩЃЌЯдЪОгЩЪ§ТыЙмЙЙГЩЃЌВЩгУЕФЪЧЖЏЬЌЯдЪОЗНЪНЁЃЪ§ТыЙмЖЏЬЌЯдЪОЃКЖЏЬЌЩЈУшЕчТЗНЋМЦЪ§ЦїЪфГіЕФ8421BGDТызЊЛЛЮЊЪ§ТыЙмашвЊЕФТпМзДЬЌЃЌВЂЧвЪфГіЪ§ТыЙмЕФЦЌбЁаХКХКЭЮЊбЁаХКХЁЃЫљЮНЖЏЬЌЩЈУшЯдЪОЗНЪНЪЧдкЯдЪОФГвЛЮЛLED ЯдЪОПщЕФЪ§ОнЕФЪБКђЃЌШУЦфЫќЮЛВЛЯдЪОЃЌШЛКѓдйЯдЪОЯТвЛЮЛЕФЪ§ОнЁЃжЛвЊБЃжЄУПвЛЮЛЯдЪОЕФЪБМфМфИєВЛвЊЬЋДѓЃЌРћгУШЫблЕФЪгОѕднСєЕФЯжЯѓЃЌОЭПЩвддьГЩИїЮЛЪ§ОнЭЌЪБЯдЪОЕФМйЯѓЁЃвЛАуУПвЛЮЛЕФЯдЪОЪБМфЮЊ1~10msЁЃ Ш§ЁЂГЬађдЫааМАНсЙћ ЃЈ1ЃЉЗжЦЕФЃПщЃЈfenpinЃЉ 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; entity fenpin is port(clk6:in std_logic; q1000,q5,q1:out std_logic); end fenpin; architecture ccc_arc of fenpin is signal x:std_logic; begin process(clk6) variable cnt:integer range 0 to 24999; begin if clk6'event and clk6='1' then if cnt<24999 then cnt:=cnt+1; else cnt:=0; x<=not x; end if; end if; end process; q1000<=x; process(x) variable cnt2:integer range 0 to 999; variable y:std_logic; begin if x'event and x='1' then if cnt2<999 then cnt2:=cnt2+1; q1<='0'; else cnt2:=0; q1<='1'; end if; end if; if x'event and x='1' then y:=not y; end if; q5<=y; end process; end ccc_arc; 2ЃЉЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃКВњЩњгУгкМЦЪБЃЌЩЈУшЪфШыЃЌЩЈУшЯдЪОЃЌвдМАЗфУљЦїЫљашЕФИїИіЦЕТЪЕФаХКХЁЃ

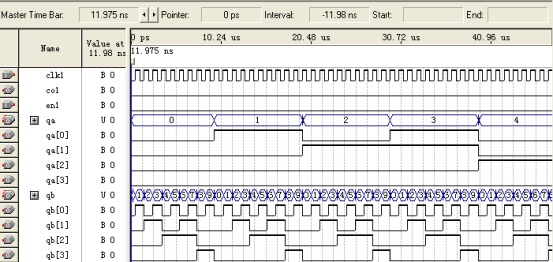

ЃЈ2ЃЉУыФЃПщЃЈsecondЃЉ 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity second is port (clk1,en1:in std_logic; qa:out std_logic_vector(3 downto 0); co1:out std_logic; qb:out std_logic_vector(3 downto 0)); end second; architecture cc of second is signal cout2,cout1:std_logic_vector(3 downto 0); signal mm: std_logic; begin process(clk1,en1) begin if en1='1' then cout2<="0000";cout1<="0000"; elsif (clk1'event and clk1='1')then if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;mm<='1'; elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";mm<='0'; else if (cout1=9) then cout2<=cout2+1;cout1<="0000";mm<='0'; else cout2<=cout2;cout1<=cout1+1;mm<='0'; end if; end if; end if; end process; co1<=mm; qa<=cout2; qb<=cout1; end cc; 2ЃЉЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃКИУФЃПщЪЕМЪЪЧвЛИіСљЪЎНјжЦМЦЪ§ЦїЃЌЖјСљЪЎУыЮЊвЛЗжжгЃЌЙЪгУДЫФЃПщПЩвдзїЮЊУыВПЗжЩшМЦЃЌЭЈЙ§ЙлВьПЩжЊЃЌЗТецВЈаЮЪЧе§ШЗПЩааЕФЁЃ

ЃЈ3ЃЉЗжФЃПщЃЈminuteЃЉ 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity minute is port (clk2,en2:in std_logic; qc:out std_logic_vector(3 downto 0); co2:out std_logic; qd:out std_logic_vector(3 downto 0)); end minute; architecture bb of minute is signal cout2,cout1:std_logic_vector(3 downto 0); signal cc:std_logic; begin process(clk2,en2) begin if en2='1' then if (clk2'event and clk2='1')then if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;cc<='1'; elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";cc<='0'; else if (cout1=9) then cout2<=cout2+1;cout1<="0000";cc<='0'; else cout2<=cout2;cout1<=cout1+1;cc<='0'; end if; end if; end if; end if; end process; co2<=cc; qc<=cout2; qd<=cout1; end bb 2ЃЉЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃКДЫФЃПщЪЕМЪвВЪЧвЛИіСљЪЎНјжЦЕФМЦЪ§ЦїФЃПщЃЌСљЪЎЗжжгМДЮЊвЛИіаЁЪБЃЌгУДЫФЃПщОЭГЩЙІНтОіСЫЗжЩшМЦФЃПщетИіФбЬтЁЃДгЗТецВЈаЮПЩжЊЃЌИУЩшМЦЪБе§ШЗЕФЁЃ

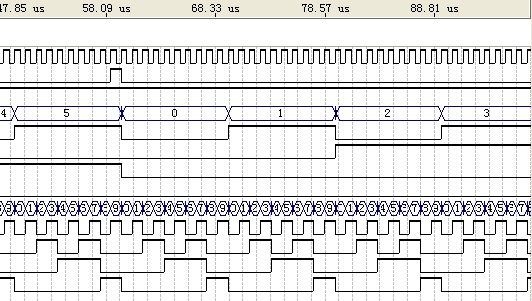

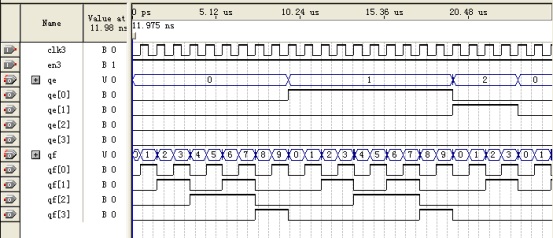

ЃЈ4ЃЉЪБФЃПщЃЈhourЃЉ 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity hour is port (clk3,en3:in std_logic; qe:out std_logic_vector(3 downto 0); qf:out std_logic_vector(3 downto 0)); end hour; architecture aa of hour is signal cout2,cout1:std_logic_vector(3 downto 0); begin process(clk3,en3) begin if en3='1' then if (clk3'event and clk3='1')then if (cout2=2 and cout1=3) then cout2<="0000";cout1<="0000"; else if (cout1=9) then cout2<=cout2+1;cout1<="0000"; else cout2<=cout2;cout1<=cout1+1; end if; end if; end if; end if; end process; qe<=cout2; qf<=cout1; end aa; 2ЃЉЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃКетЪЧвЛИі24МЦЪ§ЦїЃЌгУРДБэЪО24аЁЪБЃЌЭЈЙ§ВЈаЮПЩжЊЃЌГЬађЩшМЦе§ШЗЃЌе§ГЃМЦЪБЪЧУПДЮЧхСуКѓДг00:00:00ПЊЪММЦЪБЕФЃЌШєвЊДгдЄжУЪБМфПЊЪМЃЌПЩвдЭЈЙ§ЁАаЃЪБЁБЁАаЃЗжЁБЁАЧхСуЁБШ§ИіАДМќЕїећЪБМфЁЃ

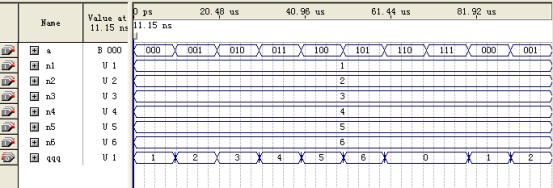

ЃЈ5ЃЉЪ§ТыЯдЪОЧ§ЖЏФЃПщ 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity hhh is port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0); a:in std_logic_vector(2 downto 0); qqq:out std_logic_vector(3 downto 0)); end hhh; architecture dd of hhh is begin with a select qqq<=n1 when "000", n2 when "001", n3 when "010", n4 when "011", n5 when "100", n6 when "101", "0000" when others; end dd; 2ЃЉЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃКЦфЪЕетЪЧвЛИібЁдёЦїЃЌДгВЈаЮЭМПЩвдКмШнвзПДГіРДЁЃЫќЪЧгУРДбЁдёашвЊЯдЪОЕФЪ§зжЃЌБШШчУыЕФЪЎЮЛЃЌОЭЛсбЁдёn1ЕНвыТыЯдЪОЦїЯдЪОГіРДЃЌОпБИЧ§ЖЏЪ§ТыЙмЕФзїгУ!

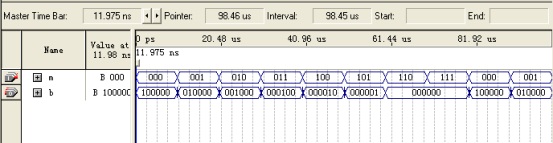

(6)ЦЌбЁФЃПщЃЈsellЃЉ 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity ggg is port(m:in std_logic_vector(2 downto 0); b:out std_logic_vector(5 downto 0)); end ggg; architecture ee of ggg is begin with m select b<="100000" when "000", "010000" when "001", "001000" when "010", "000100" when "011", "000010" when "100", "000001" when "101", "000000" when others; end ee; 2ЃЉЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃКЩшжУЪБМфЪБНЋЫљашЕФЪ§ОнДЋИјЯдЪОФЃПщЃЌЕБЩшжУФжСхЪБНЋЪ§ОнДЋИјФжжгКЭЯдЪОФЃПщЁЃ

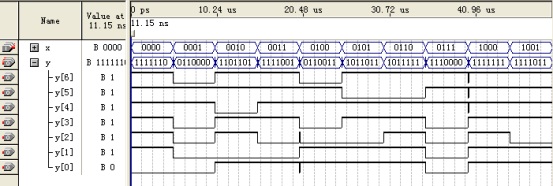

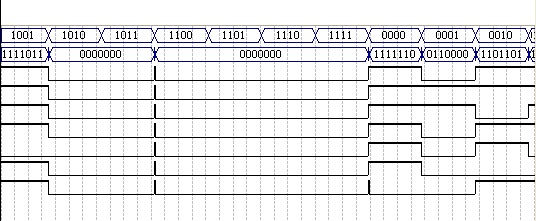

(7)выТыЯдЪОФЃПщ(display) 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity decoder is port(x:in std_logic_vector(3 downto 0); y:out std_logic_vector(6 downto 0)); end decoder; architecture one of decoder is begin with x select y<="1111110" when "0000", "0110000" when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111", "1111111" when "1000", "1111011" when "1001", "0000000" when others; end one; 2ЃЉЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃКДЫФЃПщЪЧгУРДЯдЪОЪБМфЕФЃЌВЩгУЖЏЬЌЯдЪОЗНЪНЁЃ

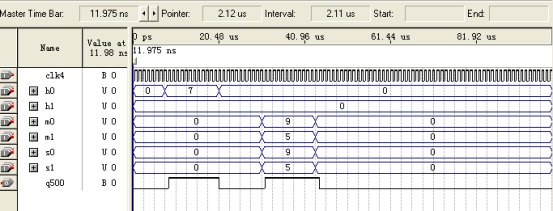

ЃЈ8ЃЉБЈЪБФЃПщЃЈalartЃЉ 1) ГЬађЃК library ieee; use ieee.std_logic_1164.all; entity sst is port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0); clk4:in std_logic; q500:out std_logic); end sst; architecture sss of sst is begin process(clk4,m1,m0,s1,s0) begin if (clk4'event and clk4='1') then if ((h1="0000" and h0="0111" and m1="0000" and m0="0000") or (m1="0101" and m0="1001" and s1="0101" and s0="1001"))then q500<='1'; else q500<='0'; end if; end if; end process; end sss; 2) ЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃКЭЈЙ§ЙлВьВЈаЮПЩжЊЃЌЕБЪБжгЪБМфгыећЕуЛђФжСхдЄЩшЪБМфЯрЭЌЪБЃЌИјГівЛИіТіГхаХКХЃЌЪЙЗфУљЦїУљНаЃЌЪЕЯжећЕуБЈЪБКЭЖЈЪБФжСхЙІФмЁЃ

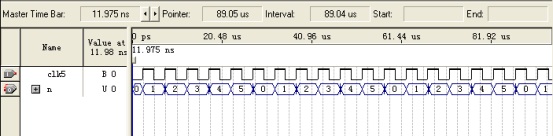

ЃЈ9ЃЉСљНјжЦМЦЪ§ЦїФЃПщЃЈcnt6ЃЉ 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt6 is port (clk5:in std_logic; n:out std_logic_vector(2 downto 0)); end cnt6; architecture behav of cnt6 is signal q1:std_logic_vector(2 downto 0); begin process(clk5) begin if clk5'event and clk5='1' then if q1<5 then q1<=q1+1; else q1<=(others=>'0'); end if; end if; end process; n<=q1; end behav; 2ЃЉЗТецВЈаЮЃК

- ЗТецНсЙћЗжЮіЃККмУїЯдПЩвдПДГіетЪЧвЛИіМђЕЅЕФСљНјжЦМЦЪ§ЦїЁЃЫќгы3-6выТыЦїХфКЯзїгУВњЩњЦЌбЁаХКХЁЃ

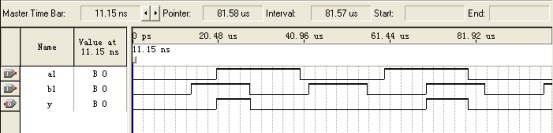

ЃЈ10ЃЉСНЪфШыгыФЃПщЃЈand2aЃЉ 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; entity anda is port (a1,b1:in std_logic; y:out std_logic); end anda; architecture an of anda is begin y<=a1 and b1; end an; 2ЃЉЗТецВЈаЮЃК

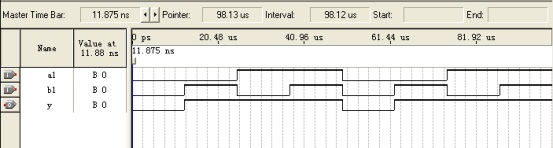

3) ЗТецНсЙћЗжЮіЃКОЙлВьВЈаЮЃЌГЬађе§ШЗЁЃИУгыУХЕФСНИіЪфШыЖЫЗжБ№ЮЊУыФЃПщКЭЗжФЃПщЕФНјЮЛЪфГіаХКХЃЌЕБЫќУЧОљЮЊИпЕчЦНЪБЃЌЪБФЃПщЪЙФмЖЫМДЮЊИпЕчЦНЃЌЪБФЃПщЙЄзїЁЃ ЃЈ11ЃЉСНЪфШыЛђФЃПщ(or2a) 1ЃЉГЬађЃК library ieee; use ieee.std_logic_1164.all; entity or_1 is port (a1,b1:in std_logic; y:out std_logic); end or_1; architecture oo of or_1 is begin y<=a1 or b1; end oo; 2ЃЉЗТецВЈаЮЃК

3) ЗТецНсЙћЗжЮіЃКдкећИіЪ§зжжгГЬађЩшМЦжаЃЌСНДІгУЕНСНЪфШыЛђУХЁЃвЛДІЪЧЗжФЃПщЃЌЛђУХСНЪфШыЗжБ№ЪЧУыФЃПщЕФНјЮЛЪфГіаХКХКЭЭтВПаЃЗжаХКХЃЌШЮвЛвЛИіаХКХЮЊИпЕчЦНЃЌЗжФЃПщЪЙФмЖЫОЭЮЊИпЕчЦНЃЌЗжФЃПщЙЄзїЁЃСэвЛДІЪЧдкЪБФЃПщЕФЪЙФмЖЫЃЌЫќЪмЗжФЃПщНјЮЛЪфГіКЭЭтВПаЃЪБаХКХЪфШыЕФПижЦЃЌжЛвЊЦфвЛЮЛИпЕчЦНЃЌЪБФЃПщЖМНЋЙЄзїЁЃ ЫФЁЂЖЅВуЕчТЗЩшМЦМАЗТецНсЙћгыЗжЮі - library ieee;

- use ieee.std_logic_1164.all;

- entity digital_clock is

- port(clk,sa,sb,sc:in std_logic;

- q1:out std_logic;

- r:out std_logic_vector(5 downto 0);

- q0:out std_logic_vector(6 downto 0));

- end digital_clock;

- architecture main of digital_clock is

- component anda

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component or_1

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component fenpin

- port(clk6:in std_logic;

- q1000,q1,q5:out std_logic);

- end component;

- component hour

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end component;

- component minute

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end component;

- component second

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end component;

- component sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end component;

- component hhh

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end component;

- component ggg

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end component;

- component cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end component;

- component decoder

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end component;

- signal a,b,c,h, i,j,z:std_logic;

- signal k,l,e,f,u,v,t:std_logic_vector(3 downto 0);

- signal s: std_logic_vector(2 downto 0);

- begin

- u1:fenpin port map(clk6=>clk,q1=>h,q1000=>z);

- u2:second port map(clk1=>h,en1=>sc,qa=>k,qb=>l,co1=>I);

- u0:or_1 port map(a1=>i,b1=>sb,y=>a);

- u3:minute port map(clk2=>h,en2=>a,qc=>e,qd=>f,co2=>j);

- u30:anda port map(a1=>i,b1=>j,y=>b);

- u31:or_1 port map(a1=>b,b1=>sa,y=>c);

- u4:hour port map(clk3=>h,en3=>c,qe=>u,qf=>v);

- u5:sst port map(h1=>u,h0=>v,m1=>e,m0=>f,s1=>k,s0=>l,clk4=>h,q500=>q1);

- u6:hhh port map(n1=>k,n2=>l,n3=>e,n4=>f,n5=>u,n6=>v,qqq=>t,a=>s);

- u7:ggg port map(b=>r,m=>s);

- u8:cnt6 port map(n=>s,clk5=>z);

- u9:decoder port map(x=>t,y=>q0);

- end architecture main;

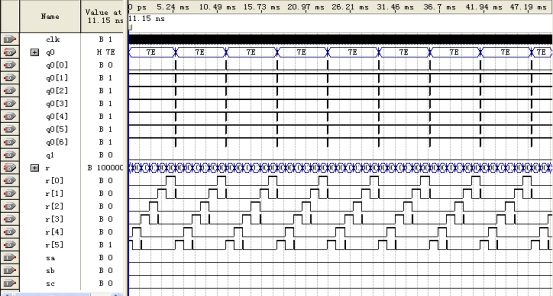

3ЃЉЗТецНсЙћЗжЮіЃКБОДЮЪдбщИјГіЕФЦЕТЪЪЧ50MHZЃЌгУQUARTUS-2ШэМўАбЪ§зжжгЕФШЋВПЙЄзїЙ§ГЬМЧТМЯТРДВЛШнвзЃЌЙЪетЗљЭМжЛЪЧЦфЙЄзїЕФвЛаЁВПЗжЁЃНЋГЬађЯТдиЕНFPGAаОЦЌжаЃЌВЂгыгВМўВПЗжЖдгІСЌНгКУЃЌПЩвдбщжЄЕНЮвУЧЫљдЄЦкЕФЫљгаЙІФмЃЌЙЪПЩжЊИУЖЅВуЮФМўЪЧе§ШЗЕФЃЌУПвЛИіФЃПщЕФЙІФмвВЖМЪЧе§ШЗЕФЃЌФЃПщжЎМфЕФСЌНгвВЖМЪЧе§ШЗЕФЁЃ дкШэМўЕїЪдЗТецЙ§ГЬжаЃЌЮвУЧвдВЮПМзЪСЯЩЯЕФГЬађЮЊФЃАхЃЌвРОнИіШЫЕФашвЊЬэМгаоИФИїИіЙІФмФЃПщЃЌОЁЙмгаФЃАхзїЮЊВЮПМЃЌЗТецЙ§ГЬжаЛЙЪЧГіСЫКмЖрЕФЮЪЬтЃЌР§ШчдкзіЪ§ТыЙмЖЏЬЌЯдЪОжаЃЌЮвУЧВЩгУСЫNPNаЭ9013ОЇЬхШ§МЋЙмзїЮЊЪ§ТыЙмЕФНгЕиЧ§ЖЏЃЌетРяЕФЦЌбЁаХКХгІИУЪЧИпЕчЦНгааЇЃЌЮвУЧдГЬађЪЧЕЭЕчЦНЃЌОЙ§ЖрДЮЕФКЭЦфЫћзщЕФбЇЯАНЛСїжаЃЌевЕНСЫетИіДэЮѓЁЃНтОіЗжЦЕЮЪЬтжаЃЌЮвУЧвВдкЗжЦЕФЃПщжазіСЫаоИФЃЌЕУЕНЮвУЧЫљашвЊЕФЦЕТЪЁЃ ЮхЁЂаФЕУЬхЛс ОЙ§етДЮЕФЪ§зжЕчТЗПЮГЬЩшМЦ,ЮвИіШЫЕУЕНСЫВЛЩйЕФЪеЛё,вЛЗНУцМгЩюСЫЮвЖдПЮБОРэТлЕФШЯЪЖ,СэвЛЗНУцвВЬсИпСЫЪЕбщВйзїФмСІЁЃЯждкЮвзмНсСЫвдЯТЕФЬхЛсКЭОбщЁЃ етДЮЕФПЮГЬЩшМЦИњЮвУЧвдЧАзіЕФВЛЭЌЃЌвђЮЊЮвОѕЕУетДЮЮвЪЧецеце§е§ЕФздМКЧзздШЅЭъГЩЁЃЫљвдЪЧЮвОѕЕУетДЮЪЕбщзюБІЙѓЃЌзюЩюПЬЕФЁЃОЭЪЧЩшМЦЕФЙ§ГЬШЋЪЧЮвУЧбЇЩњздМКЖЏЪжРДЭъГЩЕФЃЌетбљЃЌЮвУЧОЭБиаывЊХЊЖЎвЛИіЕчТЗЕФдРэЁЃдкетРяЮвЩюЩюЬхЛсЕНембЇЩЯРэТлЖдЪЕМљЕФжИЕМзїгУЃКХЊЖЎЪЕбщдРэЃЌЖјЧвЬхЛсЕНСЫЪЕбщЕФВйзїФмСІЪЧППздМКЧзздЖЏЪжЃЌЧзздПЊЖЏФдНюЃЌЧзздШЅЧыНЬБ№ШЫВХФмЕУЕНЬсИпЕФЁЃ ЮвУЧзіЪЕбщОјЖдВЛФмШЫдЦврдЦЃЌвЊгаздМКЕФПДЗЈЃЌетбљЮвУЧОЭвЊгаГфЗжЕФзМБИЃЌШєЪЧзіСЫвВВЛжЊЕРЪЧИіЪВУДЪЕбщЃЌФЧУДзіСЫвВЪЧАззіЁЃЪЕбщзмЪЧгыПЮБОжЊЪЖЯрЙиЕФЃЌгаСЫПЮБОЕФжЊЪЖЃЌЮвУЧВХФмБраДГіздМКашвЊЕФГЬађЃЌЪЕЯжздМКдЄЦкЕФЙІФмЁЃ ЮвУЧзіЪЕбщВЛвЊвЛГЩВЛБфКЭФЋЪиГЩЙцЃЌгІИУгаИФСМДДаТЕФОЋЩёЁЃЪЕМЪЩЯЃЌдкХЊЖЎСЫЪЕбщдРэЕФЛљДЁЩЯЃЌЮвУЧЕФЪБМфЪЧГфЗжЕФЃЌзіЪЕбщгІИУЪЧгЮШагагрЕФЃЌШчЙћЫЕДДаТЖдгкЮвУЧРДЫЕЪЧМўФбЪТЃЌФЧИФСМзмЪЧгаПЩФмЕФЁЃЪ§зжЪБжгДѓЬхПДЩЯШЅКмМђЕЅЃЌЕЋЦфжаЕФПЩБфЕФЕиЗНЛЙЪЧгаКмЖрЕФЃЌЦЉШчЫЕећЕуБЈЪБЙІФмЃЌБЈЪБГжајЕФЪБМфГЄЖЬОЭЪЧвЛИіПЩБфЕФЕиЗНЁЃ дкЪЕбщЕФЙ§ГЬжаЮвУЧвЊХрбјздМКЕФЖРСЂЗжЮіЮЪЬтЃЌКЭНтОіЮЪЬтЕФФмСІЁЃдкБрГЬЙ§ГЬжаЃЌЮвУЧвВгіЕНСЫКмЖрЕФЮЪЬтЃЌОЭжЎЧАЬсЕНЕФЖЏЬЌЩЈУшЧ§ЖЏЮЪЬтЃЌШчЙћвЛЮЖЕФШЅзёбзЪСЯЩЯЕФГЬађЕФЛАЃЌФЧећИіЩшМЦНЋЛсЪЇАмЃЌжЛгаВЛЖЯЕФбЇЯАбаОПЃЌВХФмНтОіЮЪЬтЁЃ етДЮЕФПЮГЬЩшМЦЃЌЮвЕФЪеЛёКмЖрЃЌОЭЮвБОЩэРДЫЕЃЌВЛЕЋЖдРэТлжЊЪЖгаСЫИќМгЩюЕФРэНтЃЌЖдгкЪЕМЪЕФВйзїКЭвВгаСЫжЪЕФЗЩдОЁЃОЙ§етДЮЕФЪЕбщЃЌЮвУЧећЬхЖдИїИіЗНУцЖМЕУЕНСЫВЛЩйЕФЬсИпЃЌЭХЖгЕФКЯзївтЪЖвВдіЧПСЫКмЖрЁЃ СљЁЂВЮПМзЪСЯЃК ИЖМвВХ .ЁЖ EDAЙЄГЬЪЕМљММЪѕ ЁЗ.ЛЏбЇЙЄвЕГіАцЩч.2004Фъ12дТ ГТжвЦН .ЁЖ ЛљгкQuartus IIЕФFPGA/CPLDЩшМЦгыЪЕМљ ЁЗ.ББОЉЕчзгЙЄвЕГіАцЩч.2010Фъ4дТ - library ieee;

- use ieee.std_logic_1164.all;

- entity fenpin is

- port(clk6:in std_logic;

- q1000,q5,q1:out std_logic);

- end fenpin;

- architecture ccc_arc of fenpin is

- signal x:std_logic;

- begin

- process(clk6)

- variable cnt:integer range 0 to 24999;

- begin

- if clk6'event and clk6='1' then

- if cnt<24999 then

- cnt:=cnt+1;

- else

- cnt:=0;

- x<=not x;

- end if;

- end if;

- end process;

- q1000<=x;

- process(x)

- variable cnt2:integer range 0 to 999;

- variable y:std_logic;

- begin

- if x'event and x='1' then

- if cnt2<999 then

- cnt2:=cnt2+1;

- q1<='0';

- else

- cnt2:=0;

- q1<='1';

- end if;

- end if;

- if x'event and x='1' then

- y:=not y;

- end if;

- q5<=y;

- end process;

- end ccc_arc;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity second is

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end second;

- architecture cc of second is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- signal mm: std_logic;

- begin

- process(clk1,en1)

- begin

- if en1='1' then

- cout2<="0000";cout1<="0000";

- elsif (clk1'event and clk1='1')then

- if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;mm<='1';

- elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";mm<='0';

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";mm<='0';

- else cout2<=cout2;cout1<=cout1+1;mm<='0';

- end if;

- end if;

- end if;

- end process;

- co1<=mm;

- qa<=cout2;

- qb<=cout1;

- end cc;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity minute is

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end minute;

- architecture bb of minute is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- signal cc:std_logic;

- begin

- process(clk2,en2)

- begin

- if en2='1' then

- if (clk2'event and clk2='1')then

- if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;cc<='1';

- elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";cc<='0';

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";cc<='0';

- else cout2<=cout2;cout1<=cout1+1;cc<='0';

- end if;

- end if;

- end if;

- end if;

- end process;

- co2<=cc;

- qc<=cout2;

- qd<=cout1;

- end bb

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity hour is

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end hour;

- architecture aa of hour is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- begin

- process(clk3,en3)

- begin

- if en3='1' then

- if (clk3'event and clk3='1')then

- if (cout2=2 and cout1=3) then cout2<="0000";cout1<="0000";

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";

- else cout2<=cout2;cout1<=cout1+1;

- end if;

- end if;

- end if;

- end if;

- end process;

- qe<=cout2;

- qf<=cout1;

- end aa;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity hhh is

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end hhh;

- architecture dd of hhh is

- begin

- with a select

- qqq<=n1 when "000",

- n2 when "001",

- n3 when "010",

- n4 when "011",

- n5 when "100",

- n6 when "101",

- "0000" when others;

- end dd;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity ggg is

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end ggg;

- architecture ee of ggg is

- begin

- with m select

- b<="100000" when "000",

- "010000" when "001",

- "001000" when "010",

- "000100" when "011",

- "000010" when "100",

- "000001" when "101",

- "000000" when others;

- end ee;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity decoder is

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end decoder;

- architecture one of decoder is

- begin

- with x select

- y<="1111110" when "0000",

- "0110000" when "0001",

- "1101101" when "0010",

- "1111001" when "0011",

- "0110011" when "0100",

- "1011011" when "0101",

- "1011111" when "0110",

- "1110000" when "0111",

- "1111111" when "1000",

- "1111011" when "1001",

- "0000000" when others;

- end one;

- library ieee;

- use ieee.std_logic_1164.all;

- entity sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end sst;

- architecture sss of sst is

- begin

- process(clk4,m1,m0,s1,s0)

- begin

- if (clk4'event and clk4='1') then

- if ((h1="0000" and h0="0111" and m1="0000" and m0="0000")

- or (m1="0101" and m0="1001" and s1="0101" and s0="1001"))then

- q500<='1';

- else

- q500<='0';

- end if;

- end if;

- end process;

- end sss;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end cnt6;

- architecture behav of cnt6 is

- signal q1:std_logic_vector(2 downto 0);

- begin

- process(clk5)

- begin

- if clk5'event and clk5='1' then

- if q1<5 then q1<=q1+1;

- else q1<=(others=>'0');

- end if;

- end if;

- end process;

- n<=q1;

- end behav;

- library ieee;

- use ieee.std_logic_1164.all;

- entity anda is

- port (a1,b1:in std_logic;

- y:out std_logic);

- end anda;

- architecture an of anda is

- begin

- y<=a1 and b1;

- end an;

- library ieee;

- use ieee.std_logic_1164.all;

- entity or_1 is

- port (a1,b1:in std_logic;

- y:out std_logic);

- end or_1;

- architecture oo of or_1 is

- begin

- y<=a1 or b1;

- end oo;

- library ieee;

- use ieee.std_logic_1164.all;

- entity digital_clock is

- port(clk,sa,sb,sc:in std_logic;

- q1:out std_logic;

- r:out std_logic_vector(5 downto 0);

- q0:out std_logic_vector(6 downto 0));

- end digital_clock;

- architecture main of digital_clock is

- component anda

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component or_1

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component fenpin

- port(clk6:in std_logic;

- q1000,q1,q5:out std_logic);

- end component;

- component hour

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end component;

- component minute

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end component;

- component second

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end component;

- component sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end component;

- component hhh

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end component;

- component ggg

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end component;

- component cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end component;

- component decoder

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end component;

- signal a,b,c,h, i,j,z:std_logic;

- signal k,l,e,f,u,v,t:std_logic_vector(3 downto 0);

- signal s: std_logic_vector(2 downto 0);

- begin

- u1:fenpin port map(clk6=>clk,q1=>h,q1000=>z);

- u2:second port map(clk1=>h,en1=>sc,qa=>k,qb=>l,co1=>I);

- u0:or_1 port map(a1=>i,b1=>sb,y=>a);

- u3:minute port map(clk2=>h,en2=>a,qc=>e,qd=>f,co2=>j);

- u30:anda port map(a1=>i,b1=>j,y=>b);

- u31:or_1 port map(a1=>b,b1=>sa,y=>c);

- u4:hour port map(clk3=>h,en3=>c,qe=>u,qf=>v);

- u5:sst port map(h1=>u,h0=>v,m1=>e,m0=>f,s1=>k,s0=>l,clk4=>h,q500=>q1);

- u6:hhh port map(n1=>k,n2=>l,n3=>e,n4=>f,n5=>u,n6=>v,qqq=>t,a=>s);

- u7:ggg port map(b=>r,m=>s);

- u8:cnt6 port map(n=>s,clk5=>z);

- u9:decoder port map(x=>t,y=>q0);

- end architecture main;

вдЩЯЕФWordИёЪНЮФЕЕ51КкЯТдиЕижЗЃК

Ъ§ЕчПЮГЬЩшМЦЁЊЁЊЛљгкfpgaЕФЪ§зжЪБжгЕФЩшМЦ.doc

(364.62 KB, ЯТдиДЮЪ§: 81)

Ъ§ЕчПЮГЬЩшМЦЁЊЁЊЛљгкfpgaЕФЪ§зжЪБжгЕФЩшМЦ.doc

(364.62 KB, ЯТдиДЮЪ§: 81)

|

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664