文中应用了MATLAB和VHDL联合设计,提出基于电路分割技术实现通信系统发送端根升余弦波形成型滤波器查表法的FPGA结构,节省了ROM单元,讨论其ROM初始化时波形数据的组织方法,完成了该结构VHDL实现,最后给出使用查找表在FPGA上实现基带脉冲成型滤波器的设计方法和ModelSim环境下的仿真结果

方案1:卷积法的原理,是用一系列乘法和加法对信号进行流水线运算,需要消耗大量的乘法器和加法器,设计较复杂,并有一定的延时。这是一种分布式算法的设计结构,将传统的乘法运算和累加运算加以改进,转变为移位、累加运算,降低了硬件消耗,当运算数据的字宽较小时,极大的降低了硬件电路的复杂度,提高了响应速度;但当运算数据的字长较长时,则需要更多的移位迭代运算而不适合高速处理的需求。

方案2:查表法的原理,采用二进制基带信号的连续查表法实现在FPGA上完成信号的脉冲成型,原理是预先将所有可能的成形后的基带波形样本存入ROM,根据输入序列,从ROM中查找对应输出波形,这种方法简单直观、速度快,且当码间样点增加时,仅增长地址电路即可,不影响运行时间,可在一定的精度内高效的实现脉冲成型滤波。

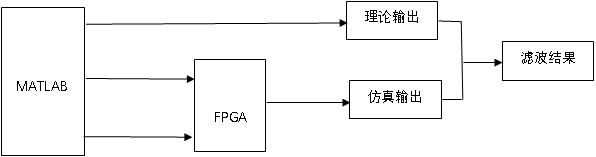

总体框图

框图

本次设计首先利用MATLAB中的FDAtool工具设计出一个采样频率为10MHZ、截止频率为50KHZ、滚降系数为0.35的升余弦滚降滤波器,通过FDAtool导出16点系数,然后将系数进行放大、取整,以便于在FPGA中使用,最后通过QuartusII进行Verilog语言编写滤波器算法,然后通过Modesim仿真结果和MATLAB仿真结果的比较来验证该滤波器的正确性

(1) 首先,在MATLAB command window 命令窗内输入 FDAtool命令,按Enter,出现FDAtool界面,FDAtool界面如图所示。

(2)设置本课题要求的平方根升余弦滤波器的参数,设置的参数见界面如图所示。本次课题采用海明窗,Fc设置为20KHZ,滚降系数设置为0.35,采样频率设置为10MHZ,阶数设置为17,即n=16。然后点击点击“designfilter”按钮。 (3)查看平方根升余弦滤波器的幅度响应图 (4)接着用MATLAB中simulink,构建滤波器仿真模块,simulink仿真如图所示。 二 FPGA 以下是用FIR核实现平方根升余弦滚降滤波器的步骤: (1)打开Quartus II 软件,新建一个“project”。点击“tool”打开“IP Catalog”界面。

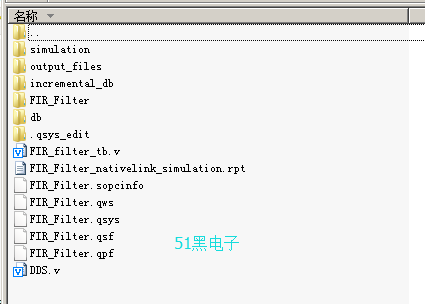

(2)在“Import from file”里导入滤波器系其频谱图如所示。 导入的系数是前面MATLAB FDAtool中生成的滤波器系数。 (3)将我们准备好的测试文件FIR_filter_tb.v和DDS .v拷贝至工程目录文件夹下,文件添加界面如图所示。

Assignment->setting->EDA tool setting->simulation->testbenches添加仿真文件。 (4)ModelSim仿真 直接启动仿真软件Modelsim-Altera,并显示仿真波形数据(模拟形式显示) data1 信号为 24KHz 正弦波,量化位宽为 12bit data2 信号为 240KHz 正弦波,量化位宽为 12bit data_in 信号为 data1 和 data2 的叠加信号,量化位宽为13bit

data_out 信号为 data_in信号经过 FIR 数字滤波后的输出,量化位宽为 28bit。仿真结果如图所示。 最后可知 matlab和FPGA的滤波结果相同。 - 附 录

- FIR_filter_tb.v

- // --------------------------------------------------------------------

- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

- // --------------------------------------------------------------------

- // Module: FIR_filter_tb

- //

- // Author: Step

- //

- // Description: FIR_filter_tb

- //

- // --------------------------------------------------------------------

- // Code Revision History :

- // --------------------------------------------------------------------

- `timescale 1ps/1ps

-

- module FIR_filter_tb;

-

- parameter PERIOD = 20;

- reg clk, rst_n;

- wire signed [26:0] data_out;

-

- initial begin

- clk = 0;

- rst_n = 0;

- #100;

- rst_n = 1;

- #6000;

- $stop;

- end

- always #10 clk = ~clk;

-

- wire signed[9:0] data1;

- DDS dds_24k

- (

- .clk_in(clk), //clock in

- .rst_n_in(rst_n), //reset, active low

- .dds_en_in(1), //dds work enable

- .f_increment(24'h60000), //frequency increment

- .p_increment(0), //phase increment

- .dac_data_out(data1) //data out

- );

-

- wire signed[9:0] data2;

- DDS dds_240k

- (

- .clk_in(clk), //clock in

- .rst_n_in(rst_n), //reset, active low

- .dds_en_in(1), //dds work enable

- .f_increment(24'h3c0000), //frequency increment

- .p_increment(0), //phase increment

- .dac_data_out(data2) //data out

- );

-

- wire signed[10:0] data_in = data1 + data2;

- FIR_Filter u0 (

- .ast_sink_data (data_in), // avalon_streaming_sink.data

- .ast_sink_valid (1), // .valid

- .ast_sink_error (0), // .error

- .ast_source_data (data_out), // avalon_streaming_source.data

- .ast_source_valid (), // .valid

- .ast_source_error (), // .error

- .clk (clk), // clk.clk

- .reset_n (rst_n) // rst.reset_n

- );

-

- endmodule

-

- DDS.v

- // --------------------------------------------------------------------

- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

- // --------------------------------------------------------------------

- // Module: DDS

- //

- // Author: Step

- //

- // Description: DDS

- //

- // --------------------------------------------------------------------

- // Code Revision History :

- // --------------------------------------------------------------------

- module DDS

- (

- input clk_in, //clock in

- input rst_n_in, //reset, active low

- input dds_en_in, //dds work enable

- input [23:0] f_increment, //frequency increment

- input [23:0] p_increment, //phase increment

- output dac_clk_out, //clock out

- output [9:0] dac_data_out //data out

- );

- reg [23:0] phase_accumulator;

- wire [23:0] phase;

- //wire [9:0] dac_data_out;

- assign dac_clk_out = clk_in;

- //next_phase = phase_accumulator + f_increment;

- always @(posedge clk_in or negedge rst_n_in)

- begin

- if(!rst_n_in) phase_accumulator <= 23'b0;

- else if(dds_en_in) phase_accumulator <= phase_accumulator + f_increment;

- end

- assign phase = phase_accumulator + p_increment; // phase is the high 8 bits

- lookup_table lookup_table_uut

- (

- .phase(phase[23:16]),

- .dac_data_out(dac_data_out)

- );

- endmodule

- /**************************************************

- module: lookup_table

- **************************************************/

- module lookup_table

- (

- input [7:0] phase,

- output reg [9:0] dac_data_out

- );

- wire [5:0] address = phase[5:0];

- wire [1:0] sel = phase[7:6];

- wire [9:0] sine;

- always@(sel or sine)

- case (sel)

- 2'b00 : dac_data_out = {1'b0, sine[9:1]};

- 2'b01 : dac_data_out = {1'b0, sine[9:1]};

- 2'b10 : dac_data_out = {1'b1, 9'h1ff-sine[9:1]};

- 2'b11 : dac_data_out = {1'b1, 9'h1ff-sine[9:1]};

- endcase

- sine_table sine_table_uut

- (

- .sel(sel),

- .address(address),

- .sine(sine)

- );

-

- endmodule

- /**************************************************

- module: sine_table

- **************************************************/

- module sine_table

- (

- input [1:0] sel,

- input [5:0] address,

- output reg [9:0] sine

- );

- reg [5:0] table_addr;

- always @(sel or address)

- case (sel)

- 2'b00: table_addr = address;

- 2'b01: table_addr = 6'h3f - address;

- 2'b10: table_addr = address;

- 2'b11: table_addr = 6'h3f - address;

- endcase

- always @(table_addr)

- case(table_addr)

- 6'h0: sine=10'h000;

- 6'h1: sine=10'h019;

- 6'h2: sine=10'h032;

- 6'h3: sine=10'h04B;

- 6'h4: sine=10'h064;

- 6'h5: sine=10'h07D;

- 6'h6: sine=10'h096;

- 6'h7: sine=10'h0AF;

- 6'h8: sine=10'h0C4;

- 6'h9: sine=10'h0E0;

- 6'ha: sine=10'h0F9;

- 6'hb: sine=10'h111;

- 6'hc: sine=10'h128;

- 6'hd: sine=10'h141;

- 6'he: sine=10'h159;

- 6'hf: sine=10'h170;

- 6'h10: sine=10'h187;

- 6'h11: sine=10'h19F;

- 6'h12: sine=10'h1B5;

- 6'h13: sine=10'h1CC;

- 6'h14: sine=10'h1E2;

- 6'h15: sine=10'h1F8;

- 6'h16: sine=10'h20E;

- 6'h17: sine=10'h223;

- 6'h18: sine=10'h238;

- 6'h19: sine=10'h24D;

- 6'h1a: sine=10'h261;

- 6'h1b: sine=10'h275;

- 6'h1c: sine=10'h289;

- 6'h1d: sine=10'h29C;

- 6'h1e: sine=10'h2AF;

- 6'h1f: sine=10'h2C1;

- 6'h20: sine=10'h2D3;

- 6'h21: sine=10'h2E5;

- 6'h22: sine=10'h2F6;

- 6'h23: sine=10'h307;

- 6'h24: sine=10'h317;

- 6'h25: sine=10'h326;

- 6'h26: sine=10'h336;

- 6'h27: sine=10'h344;

- 6'h28: sine=10'h353;

- 6'h29: sine=10'h360;

- 6'h2a: sine=10'h36D;

- 6'h2b: sine=10'h37A;

- 6'h2c: sine=10'h386;

- 6'h2d: sine=10'h392;

- 6'h2e: sine=10'h39C;

- 6'h2f: sine=10'h3A7;

- 6'h30: sine=10'h3B1;

- 6'h31: sine=10'h3BA;

- 6'h32: sine=10'h3C3;

- 6'h33: sine=10'h3CB;

- 6'h34: sine=10'h3D3;

- 6'h35: sine=10'h3DA;

- 6'h36: sine=10'h3E0;

- 6'h37: sine=10'h3E6;

- 6'h38: sine=10'h3EB;

- 6'h39: sine=10'h3F0;

- 6'h3a: sine=10'h3F3;

- 6'h3b: sine=10'h3F7;

- 6'h3c: sine=10'h3FA;

- 6'h3d: sine=10'h3FC;

- 6'h3e: sine=10'h3FE;

- 6'h3f: sine=10'h3FF;

- endcase

- endmodule

全部资料51hei下载地址:

FIR_Filter.zip

(1.14 MB, 下载次数: 28)

FIR_Filter.zip

(1.14 MB, 下载次数: 28)

|