|

课程名称:数字逻辑电路实验A 第二次试验 实验名称:可编程数字逻辑设计基础 院系:电子科学与工程学院 专业:电子科学与技术(类) 目的和要求: - 了解可编程数字系统设计的流程

- 掌握Quartus软件的使用方法

- 掌握竞争和冒险的基本概念和电路的时延分析方法

实验原理: - 观察并记录实验箱上的FPGA型号,新建一个Project,器件选用实验箱上的FPGA;

由于硬木课堂上的FPGA型号为”Cyclone Ⅳ”,而实验所采用的版本Quartus9.1不支持此型号,所以在新建project时,在Assignment中选择Device,选择其中的Family下拉框,点击“CycloneⅢ”,Available devices列表中选择EP3C5E144C8,点击“OK”即可。 - 用“AND2”和“XOR”器件设计一个1位半加器,并用功能仿真进行验证;

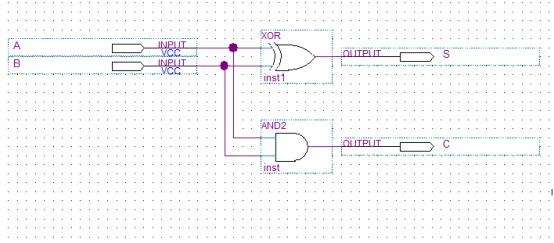

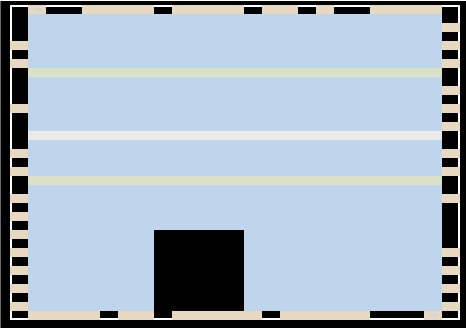

设计方案:①AND2为一个二输入与门,XOR为二输入异或门,因为一位半加器无进位输入量,所以设输入变量为A与B,输出变量为S和C,S为结果,C为进位输出量。 ②根据一位半加器的要求列出真值表如下表所示: ③因为输入量个数较少,直接根据真值表可得S=A’B+AB’,即为A与B的异或; C=AB,所以据此得到此二输出的逻辑函数:S=A’B+AB’,C=AB; ④点击File中的New项,将出现新建文件对话框,选择“Design File/Block Diagram/Schematic File”项,点击“OK”即可打开”Block Editor”,双击原理图空白部分,在name栏中分别搜索imput,output,XOR和AND2得到所需元件,然后利用左侧绘图工具建立原理图,保存在Project的相同文件夹中。如下图所示:

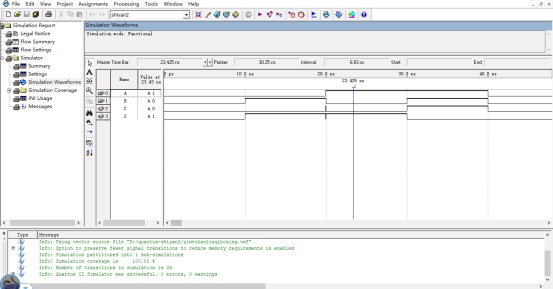

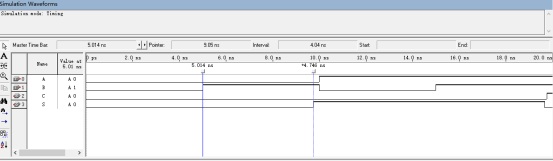

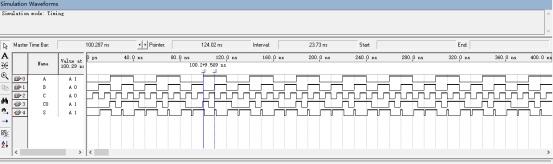

⑤功能验证: 首先点击Project Navigator/files/Device Design Files,选中要编译的“yiweibanjiaqi.bdf”文件,右键将其“Set as Top-level Entity”,先不分配管脚,下面建立输入激励波形文件,按照New/Verification/Debugging Files/Vector Waveform File建立文件后双击Name空白处,按照Insert Node or Bus/Node Finder/list/”>>”的顺序,利用左图的工具将激励波形完成后将其“Save”到Project的文件夹中,注意在完善激励波形的时候用Edit/End time.Grid size设置好截止时间以方便设置周期及后面的时延分析。然后按照“Processing/Simulator Tool/Functional”,然后在Simulator input中指定之前所保存的波形激励文件,按照“Generate Functional Simulator Netlist”生成功能仿真网表文件,点击“Start”进行仿真计算,完成后点击“Report”打开仿真结果波形。仿真结果波形如下:

由上面的输入输出波形与真值表相比对输出结果完全正确,功能验证完成。 - 点击“File”?“Create/Update”“Create Symbol File for Current File”菜单项,将1位半加器封装成元件。新建一个原理图文件,调用2个半加器实现一个1位全加器,并用功能仿真进行验证;

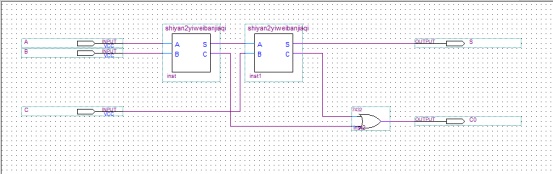

接着上面的功能仿真结束后,直接在当前工程下按照“File/Create/Update/Create Symbol File for Current File”的顺序将一位半加器封装成元件命名为“shiyan2yiweibanjiaqi”,封装即完成. 设计方案:设计一个一位全加器需要三个输入量,此处定义为A,B,C,其中A,B为加数与被加数,C为输入进位量,输出量为S与C0,S为和,C0为输出进位,先根据一位全加器的定义列出真值表如下表所示: 根据以上真值表列出卡诺图如下图所示: ①对S:

根据卡诺图化简后所得的关于输出量S的逻辑函数表达式为:S=A⊕B⊕C; ①对C0: 根据卡诺图化简后所得的关于输出量C0的逻辑函数表达式为:C0=AB+AC; 由上面的逻辑函数表达式确定原理图的绘制过程如下:然后按照之前建立原理图的顺序,即点击File中的New项,将出现新建文件对话框,选择“Design File/Block Diagram/Schematic File”项,点击“OK”即可打开”Block Editor”,双击原理图空白部分,在name栏中搜索”yiweibanjiaqi”即可调出刚刚封装的一位半加器元件,继续搜索相应的“output/input/7432(或门)”,按照上述逻辑函数进行原理图的绘制,绘制后的原理图如下所示:

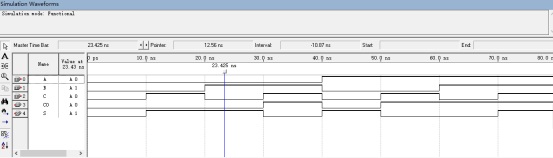

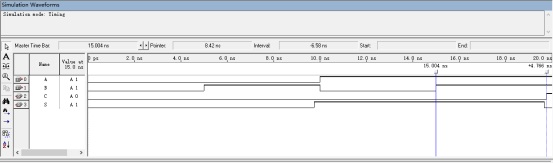

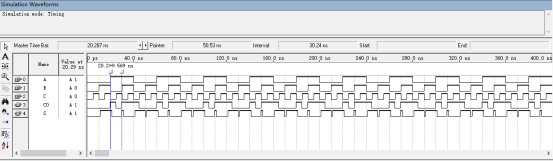

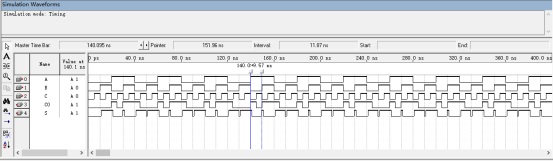

首先点击Project Navigator/files/Device Design Files,选中要编译的“yiweibanjiaqi.bdf”文件,右键将其“Set as Top-level Entity”,先不分配管脚,下面建立输入激励波形文件,按照New/Verification/Debugging Files/Vector Waveform File建立文件后双击Name空白处,按照Insert Node or Bus/Node Finder/list/”>>”的顺序,利用左图的工具将激励波形完成后将其“Save”到Project的文件夹中,注意在完善激励波形的时候用Edit/End time.Grid size设置好截止时间以方便设置周期及后面的时延分析。然后按照“Processing/Simulator Tool/Functional”,然后在Simulator input中指定之前所保存的波形激励文件,按照“Generate Functional Simulator Netlist”生成功能仿真网表文件,点击“Start”进行仿真计算,完成后点击“Report”打开仿真结果波形。仿真结果波形如下:

将仿真的结果波形与真值表相比较,结果一致,功能验证成功完成。 - 将 1 位全加器封装成元件,新建原理图文件,调用 4 个全加器实现一个 4 位行波加法器,用功能仿真进 行验证,用“Tools”“Netlist Viewers”“RTL Viewer”查看电路综合结果;

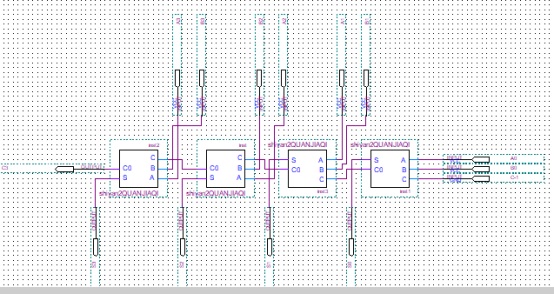

接着上面的功能仿真结束后,直接在当前工程下按照“File/Create/Update/Create Symbol File for Current File”的顺序将一位全加器封装成元件命名为“yiweiquanjiaqi”,封装即完成. 设计方案:设计一个四位行波加法器需要九个输入量,用C-1,A3,A2,A1,A0,B3,B2,B1,B0来表示,其中C-1为低位位进位,此处置零。设计行波加法器采用并行相加串行进位的方式,低位全加器的进位进到高一位的加法器,由于四位行波加法器的情况较多,我们只从原理的角度进行分析,此处不再列出真值表,根据四位行波加法器的工作原理可画出下面的原理图: 然后按照之前建立原理图的顺序,即点击File中的New项,将出现新建文件对话框,选择“Design File/Block Diagram/Schematic File”项,点击“OK”即可打开”Block Editor”,双击原理图空白部分,在name栏中搜索”yiweiquanjiaqi”即可调出刚刚封装的一位全加器元件,继续搜索相应的“output/input”,按照上述工作原理进行原理图的绘制,绘制后的原理图如下所示:

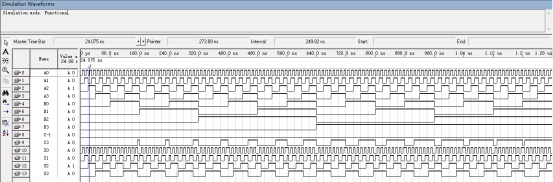

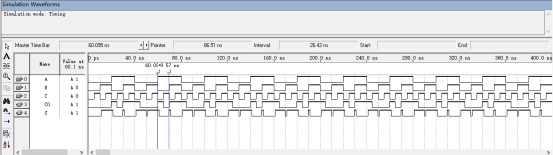

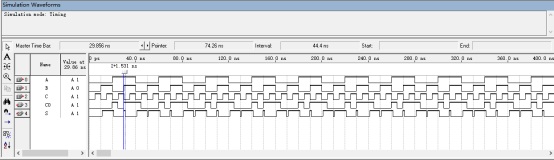

建立保存原理图之后,首先点击Project Navigator/files/Device Design Files,选中要编译的“yiweiquanjiaqi.bdf”文件,右键将其“Set as Top-level Entity”,先不分配管脚,下面建立输入激励波形文件,按照New/Verification/Debugging Files/Vector Waveform File建立文件后双击Name空白处,按照Insert Node or Bus/Node Finder/list/”>>”的顺序,利用左图的工具将激励波形完成后将其“Save”到Project的文件夹中,注意在完善激励波形的时候用Edit/End time.Grid size设置好截止时间以方便设置周期及后面的时延分析。然后按照“Processing/Simulator Tool/Functional”,然后在Simulator input中指定之前所保存的波形激励文件,按照“Generate Functional Simulator Netlist”生成功能仿真网表文件,点击“Start”进行仿真计算,完成后点击“Report”打开仿真结果波形。仿真结果波形如下:

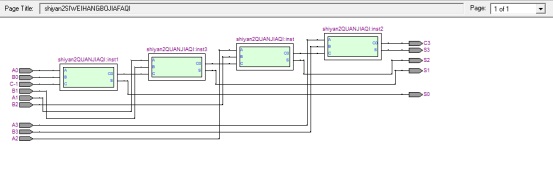

功能验证结果与逻辑值一致,功能验证完成。 接着按照题干要求提示查看电路综合效果,结果如下:

- 适配编译,用“Tools”“Netlist Viewers”“Technology Map Viewer”查看电路 Map 结果;用 “Tools”?“Chip Planner”查看器件适配结果;

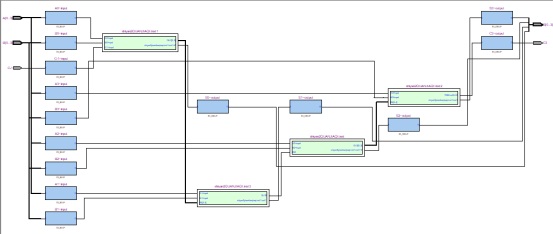

按照题干查看电路Map结果,效果如下:

按照题干查看器件适配结果,效果如下: 、 6.将 4 位全加器下载到实验箱,连接逻辑电平开关进行功能验证(课内验收); 硬木课堂上的FPGA为Cyclone Ⅳ,但是Quartus9.1版本的Device中最新版本FPGA只包含Cyclone Ⅲ,故将FPGA先与电脑连接然后打开电脑设备管理器选择“通用串行总线控制器”,选择其中的“Altera USB-Blaster”,右键选择“更新驱动程序”,根据向导点击“浏览我的计算机以查找驱动程序软件”,找到Quartus安装包中的”drivers”,勾选“包括子文件夹”进行驱动设备的更新即可。 新建project时,在Assignment中选择Device,选择其中的Family下拉框,点击“Cyclone Ⅳ E”,Available devices列表中选择EP4CE6F17C7,点击“OK”即可。按照FPGA上面的管脚参数给四位行波加法器分配引脚,将C-1引脚分配至KEY0处,其余用逻辑电平SW0~SW7控制输入量,输出利用LED0~LED4的亮与不亮来显示输出量,管脚分配完成后,点击“Programmer”,添加硬件为USB-Blaster,点击start,开始逻辑电平的功能验证,已通过课内验收。 - 对 1 位半加器,进行时序仿真,并做时延分析,可参考预备知识相关内容;

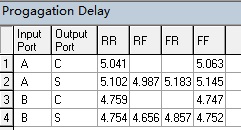

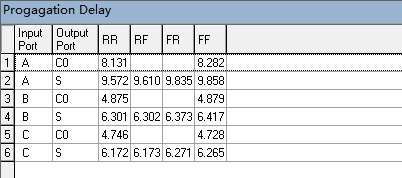

首先点击Project Navigator/files/Device Design Files,选中要编译的“yiweibanjiaqi.bdf”文件,右键将其“Set as Top-level Entity”,然后按照“Processing/Simulator Tool”进入仿真页面,Simulator mode下拉框中选择“Timing”,激励波形文件选择之前建立的“shiyan2yiweibanjiaqi.vmf”文件,start之后选择Report可以查看仿真结果波形。 在查看仿真结果波形之前,我们先查看电路的时延信息,时延信息如下表所示:

其中RR,RF,FR,FF分别表示输入信息变化与输出做出反应之间的时间差,即时延,下面我们查看仿真结果波形,如下图所示:

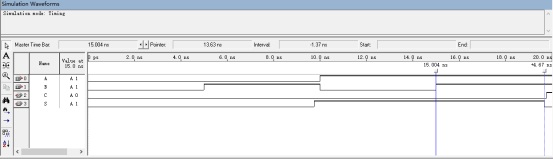

然后通过两个TimeBar来确定时延信息,如图中所示:当B从0变成1时,C也从0变成1,此时时间差为4.766ns,即为B对C的RR,与上表中比较误差为4.766-4.759=0.007ns,误差较小。同理可知,B对S的RF为4.67ns,与表中时延数据相差为0.014ns,误差较小,B对S的RR=4.746ns,与表格中基本一致,说明时间延迟与表中数据基本一致。可直接按照表中时延数据进行电路的分析。 - 对 1 位全加器,进行时序仿真,并做时延分析,要求:a) 测量A第1~4个上升沿到对应的的S输出之间的延迟时间;b) 对输出S的毛刺进行测量和分析;c) 对输出C的毛刺进行测量和分析;d) 对测得的时延结果进行分析。

时延信息如下表所示: a 第一个:时延9.569ns;

第二个:时延9.57ns;

第三个:时延9.569ns;  第四个:时延 9.57ns; 第四个:时延 9.57ns;

b

此处的输出毛刺为1.531ns,此处ABC对应的电平为110,S对应的输出应当为零,但是出现了短暂的毛刺,说明此处存在由于电路延时而出现的竞争冒险情况。 C0的输出如图所示,并未出现明显的毛刺现象。 - 电路中由于输入与输出之间的延时会导致电路出现竞争冒险情况,即在同一时刻,输入与输出的情况不对应,就会导致所设计的产品出现工作不稳定的情况,可以通过逻辑函数的化简来消除竞争冒险情况。

- 对 4 位全加器,进行时序仿真,并做时延分析,要求: a) 测量 Cin=“0”,B=“0111”,A 从“0000”?“0001” 所对应输出 S3的时延; b) 测量 Cin=“0”,B=“0110”,A 从“0000”?“0010” 所对应输出 S3的时延; c) 测量 Cin=“0”,B=“0100”,A 从“0000”?“0100” 所对应输出 S3的时延; d) 测量 Cin=“0”,B=“0000”,A 从“0000”?“1000” 所对应输出 S3的时延; e) 测量 Cin=“1”,B=“0000”,A 从“0000”?“0111” 所对应输出 S3的时延; f) 测量 Cin=“0”,B=“1111”,A 从“0000”?“0001” 所对应输出 Cout的时延; g) 测量 Cin=“0”,B=“1110”,A 从“0000”?“0010” 所对应输出 Cout的时延; h) 测量 Cin=“0”,B=“1100”,A 从“0000”?“0100” 所对应输出 Cout的时延; i) 测量 Cin=“0”,B=“1000”,A 从“0000”?“1000” 所对应输出 Cout的时延; j) 测量 Cin=“1”,B=“1000”,A 从“0000”?“0111” 所对应输出 Cout的时延; k) 对测得的时延结果进行分析

时延为10.785ns; 时延为10.354ns; 时延为9.491ns; 时延为8.8ns; 时延为10.526ns; 时延为10.526ns; 时延为10.008ns; 时延为9.146ns; 时延为8.628ns; 时延为10.354ns;

完整的Word格式文档51黑下载地址:

大学时期的数电入门实验.docx

(365.78 KB, 下载次数: 29)

大学时期的数电入门实验.docx

(365.78 KB, 下载次数: 29)

|