|

|

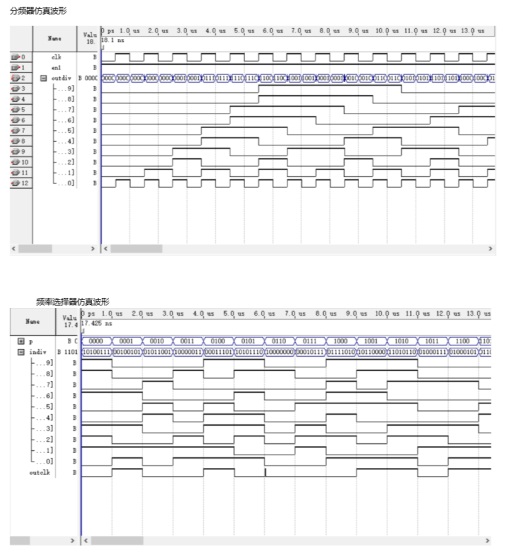

- //******ДЈҝйТ»Јә·ЦЖөЖч*****************//

- /*en1ОӘК№ДЬ¶ЛЈ¬clkОӘКдИлЖөВКЈ¬outdiv(0-9)ОӘКдіцЖөВКЈ¬

- outdiv(0)ОӘІ»ҪшРР·ЦЖөЈ¬outdiv(1)ҪшРР2·ЦЖөЈ¬

- outdiv(2)ҪшРР3·ЦЖөЈ¬outdiv(3)ҪшРР4·ЦЖөЈ¬

- outdiv(4)ҪшРР5·ЦЖөЈ¬outdiv(5)ҪшРР6·ЦЖөЈ¬

- outdiv(6)ҪшРР7·ЦЖөЈ¬outdiv(7)ҪшРР8·ЦЖөЈ¬

- outdiv(8)ҪшРР9·ЦЖөЈ¬outdiv(9)ҪшРР10·ЦЖөЎЈ*/

- library ieee;

- use ieee.std_logic_1164.all;

- entity FPQ is

- port(clk,en1: in std_logic;

- outdiv : out std_logic_vector(9 downto 0));

- end FPQ;

- architecture bh of FPQ is

- begin

- process(en1,clk)

- variable t1 : integer range 0 to 2;

- variable t2 : integer range 0 to 3;

- variable t3 : integer range 0 to 4;

- variable t4 : integer range 0 to 5;

- variable t5 : integer range 0 to 6;

- variable t6 : integer range 0 to 7;

- variable t7 : integer range 0 to 8;

- variable t8 : integer range 0 to 9;

- variable t9 : integer range 0 to 10;

- begin

- outdiv(0) <= clk;

- if clk'event and clk = '1' then

- if en1 = '1' then

- if (t1 >= 2) then t1:=0;outdiv(1)<='0';

- elsif t1<1 then outdiv(1)<='0';

- else outdiv(1) <= '1';

- end if;

- t1:=t1+1;

- if (t2 >= 3) then t2:=0;outdiv(2)<='0';

- elsif t2<2 then outdiv(2)<='0';

- else outdiv(2) <= '1';

- end if;

- t2:=t2+1;

- if (t3 >= 4) then t3:=0;outdiv(3)<='0';

- elsif t3<2 then outdiv(3)<='0';

- else outdiv(3) <= '1';

- end if;

- t3:=t3+1;

- if (t4 >= 5) then t4:=0;outdiv(4)<='0';

- elsif t4<3 then outdiv(4)<='0';

- else outdiv(4) <= '1';

- end if;

- t4:=t4+1;

- if (t5 >= 6) then t5:=0;outdiv(5)<='0';

- elsif t5<3 then outdiv(5)<='0';

- else outdiv(5) <= '1';

- end if;

- t5:=t5+1;

- if (t6 >= 7) then t6:=0;outdiv(6)<='0';

- elsif t6<4 then outdiv(6)<='0';

- else outdiv(6) <= '1';

- end if;

- t6:=t6+1;

- if (t7 >= 8) then t7:=0;outdiv(7)<='0';

- elsif t7<4 then outdiv(7)<='0';

- else outdiv(7) <= '1';

- end if;

- t7:=t7+1;

- if (t8 >= 9) then t8:=0;outdiv(8)<='0';

- elsif t8<5 then outdiv(8)<='0';

- else outdiv(8) <= '1';

- end if;

- t8:=t8+1;

- if (t9 >= 10) then t9:=0;outdiv(9)<='0';

- elsif t9<5 then outdiv(9)<='0';

- else outdiv(9) <= '1';

- end if;

- t9:=t9+1;

- end if;

- end if;

- end process;

- end bh;

-

-

-

-

-

-

-

-

-

-

- //***********ДЈҝй¶юЈәЖөВКСЎФсЖч**************//

- /*P0ЎўP1ЎўP2ЎўP3ОӘЖөВКСЎФсРЕәЕЈ¬indivЈЁ0-9Ј©ОӘ·ЦЖөЖч·ЦЖөЦ®әуөДЖөВКРЕәЕЈ¬

- outclkОӘТӘСЎФсөДЖөВКЎЈ

- өұp(3-0)ОӘ"0000"КұЈ¬outclkОӘindivЈЁ0Ј©Ј»өұp(3-0)ОӘ"0001"КұЈ¬outclkОӘindivЈЁ1Ј©Ј»

- өұp(3-0)ОӘ"0010"КұЈ¬outclkОӘindivЈЁ2Ј©Ј»өұp(3-0)ОӘ"0011"КұЈ¬outclkОӘindivЈЁ3Ј©Ј»

- өұp(3-0)ОӘ"0100"КұЈ¬outclkОӘindivЈЁ4Ј©Ј»өұp(3-0)ОӘ"0101"КұЈ¬outclkОӘindivЈЁ5Ј©Ј»

- өұp(3-0)ОӘ"0110"КұЈ¬outclkОӘindivЈЁ6Ј©Ј»өұp(3-0)ОӘ"0111"КұЈ¬outclkОӘindivЈЁ7Ј©Ј»

- өұp(3-0)ОӘ"1000"КұЈ¬outclkОӘindivЈЁ8Ј©Ј»өұp(3-0)ОӘ"1001"КұЈ¬outclkОӘindivЈЁ9Ј©Ј»

- өұp(3-0)ОӘЖдЛьКұЈ¬outclkОӘindivЈЁ0Ј©ЎЈ*/

- library ieee;

- use ieee.std_logic_1164.all;

- entity PLXZQ is

- port(p: in std_logic_vector(3 downto 0);

- indiv : in std_logic_vector(9 downto 0);

- outclk : out std_logic);

- end PLXZQ;

- architecture bh1 of PLXZQ is

- begin

- process(p,indiv)

- begin

- case p is

- when "0000" => outclk <= indiv(0);

- when "0001" => outclk <= indiv(1);

- when "0010" => outclk <= indiv(2);

- when "0011" => outclk <= indiv(3);

- when "0100" => outclk <= indiv(4);

- when "0101" => outclk <= indiv(5);

- when "0110" => outclk <= indiv(6);

- when "0111" => outclk <= indiv(7);

- when "1000" => outclk <= indiv(8);

- when "1001" => outclk <= indiv(9);

- when others => outclk <= indiv(0);

- end case;

- end process;

- end bh1;

-

-

-

-

-

-

-

-

-

-

-

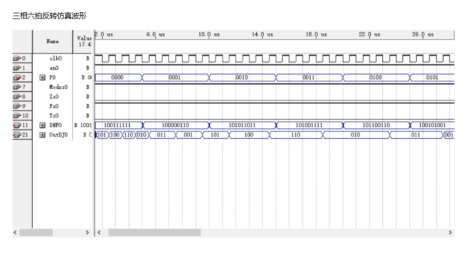

- //***********ДЈҝйИэЈә·ҪПтЛшҙжЖч**************//

- /*ZzЎўFzЎўTzОӘ·ҪПтәНҝӘ№ШРЕәЕЈ¬ModxzОӘБщЕДәНИэЕДСЎФсЗР»»РЕәЕЈ¬

- outctrlОӘКдіцөДҝШЦЖРЕәЕЎЈ

- өұModxzОӘ1КұЈ¬ОӘБщЕДЈ»өұModxzОӘ0КұЈ¬ОӘЛ«ИэЕДЎЈ

- өұTzОӘ1КұЈ¬ОӘНЈЦ№өз»ъЈ¬өұTzОӘ0КұЈ¬ОӘЖф¶Ҝөз»ъЎЈ

- өұZzОӘ1ЎўFzОӘ0КұЈ¬ОӘөз»ъХэЧӘЈ¬

- өұZzОӘ0ЎўFzОӘ1КұЈ¬ОӘөз»ъ·ҙЧӘЈ¬

- өұZzОӘ1ЎўFzОӘ1КұЈ¬ОӘөз»ъНЈЦ№Ј¬

- өұZzОӘ0ЎўFzОӘ0КұЈ¬ОӘөз»ъНЈЦ№ЎЈ

- outctrlЈЁ0Ј©¶ФУҰTzЈ»outctrlЈЁ1Ј©¶ФУҰFzЈ»

- outctrlЈЁ2Ј©¶ФУҰZzЈ»outctrlЈЁ3Ј©¶ФУҰModxzЎЈ*/

- library ieee;

- use ieee.std_logic_1164.all;

- entity FXSCQ is

- port(modxz,zz,fz,tz: in std_logic;

- outctrl: out std_logic_vector(3 downto 0));

- end FXSCQ;

- architecture bh2 of FXSCQ is

- begin

- process(modxz,zz,fz,tz)

- begin

- outctrl(0) <= tz;

- outctrl(1) <= fz;

- outctrl(2) <= zz;

- outctrl(3) <= modxz;

- if zz = '1' and fz = '1' then

- outctrl(0) <= '1';

- elsif zz = '0' and fz = '0' then

- outctrl(0) <= '1';

- end if;

- end process;

- end bh2;

-

-

-

-

-

-

- //***********ДЈҝйЛДЈәЦРСлҝШЦЖЖч**************//

- /*inclkОӘҫӯ№эЖөВКСЎФсЖчСЎФсЦ®әуөДКдИлЖөВКЈ¬

- inctrlОӘҫӯ№э·ҪПтЛшҙжЖчЦ®әуөДКдИлҝШЦЖРЕәЕЈ¬

- outDjОӘИэПаөз»ъөДөДИэПаөзС№Ј¬

- өұinctrlОӘЎ°0100ЎұКұЈ¬өз»ъОӘЛ«ИэПаХэЧӘЈ»

- өұinctrlОӘЎ°0010ЎұКұЈ¬өз»ъОӘЛ«ИэПа·ҙЧӘЈ»

- өұinctrlОӘЎ°1100ЎұКұЈ¬өз»ъОӘөҘБщПаХэЧӘЈ»

- өұinctrlОӘЎ°1010ЎұКұЈ¬өз»ъОӘөҘБщПаХэЧӘЈ»

- өұinctrlОӘЎ°xxx1ЎұКұЈ¬өз»ъНЈЦ№ЎЈ*/

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity CPU is

- port(inclk: in std_logic;

- inctrl: in std_logic_vector(3 downto 0);

- outDJ: out std_logic_vector(2 downto 0));

- end CPU;

- architecture bh3 of CPU is

- signal Tmp : std_logic_vector(2 downto 0);

- begin

- process(inclk,inctrl)

- begin

- if inclk'event and inclk = '1' then

- if inctrl = "1100" then

- if Tmp = 6 then

- Tmp <= "001";

- else

- Tmp <= Tmp+1;

- end if;

- elsif inctrl = "1010" then

- if Tmp = 1 then

- Tmp <= "110";

- else

- Tmp <= Tmp-1;

- end if;

- elsif inctrl = "1000" then

- Tmp <= "000";

- elsif inctrl = "0100" then

- if Tmp = 6 then

- Tmp <= "010";

- else

- Tmp <= Tmp+2;

- end if;

- elsif inctrl = "0010" then

- if Tmp = 2 then

- Tmp <="110";

- else

- Tmp <= Tmp-2;

- end if;

- elsif inctrl = "0000" then

- Tmp <= "000";

- end if;

- end if;

- end process;

- with Tmp select

- outDJ <= "001" when "001",

- "011" when "010",

- "010" when "011",

- "110" when "100",

- "100" when "101",

- "101" when "110",

- "000" when others;

- end bh3;

-

-

-

- //***********ДЈҝйОеЈәТлВлЖч**************//

- /*xykЈЁ3-0Ј©ОӘКдИлРЕәЕЈ¬КдИлКэЦөЈ¬dnfЈЁ8-0Ј©ОӘКдіцҝШЦЖКэВл№ЬРЕәЕЎЈ

- //dnfЈЁ8Ј©ОӘКэВл№ЬөДО»СЎРЕәЕЎЈ

- өұxykОӘЎ°0000ЎұКұЈ¬dnfКдіцОӘЎ°100111111ЎұЈ¬ КэВл№ЬПФКҫЎ®0ЎҜЈ»

- өұxykОӘЎ°0001ЎұКұЈ¬dnfКдіцОӘЎ°100000110ЎұЈ¬ КэВл№ЬПФКҫЎ®1ЎҜЈ»

- өұxykОӘЎ°0010ЎұКұЈ¬dnfКдіцОӘЎ°101011011ЎұЈ¬ КэВл№ЬПФКҫЎ®2ЎҜЈ»

- өұxykОӘЎ°0011ЎұКұЈ¬dnfКдіцОӘЎ°101001111ЎұЈ¬ КэВл№ЬПФКҫЎ®3ЎҜЈ»

- өұxykОӘЎ°0100ЎұКұЈ¬dnfКдіцОӘЎ°101100110ЎұЈ¬ КэВл№ЬПФКҫЎ®4ЎҜЈ»

- өұxykОӘЎ°0101ЎұКұЈ¬dnfКдіцОӘЎ°100101001ЎұЈ¬ КэВл№ЬПФКҫЎ®5ЎҜЈ»

- өұxykОӘЎ°0110ЎұКұЈ¬dnfКдіцОӘЎ°101111101ЎұЈ¬ КэВл№ЬПФКҫЎ®6ЎҜЈ»

- өұxykОӘЎ°0111ЎұКұЈ¬dnfКдіцОӘЎ°100000111ЎұЈ¬ КэВл№ЬПФКҫЎ®7ЎҜЈ»

- өұxykОӘЎ°1000ЎұКұЈ¬dnfКдіцОӘЎ°101111111ЎұЈ¬ КэВл№ЬПФКҫЎ®8ЎҜЈ»

- өұxykОӘЎ°1001ЎұКұЈ¬dnfКдіцОӘЎ°101100111ЎұЈ¬ КэВл№ЬПФКҫЎ®9ЎҜЈ»

- өұxykОӘЖдЛьКұЈ¬dnfКдіцОӘЎ°100111111ЎұЈ¬ КэВл№ЬПФКҫЎ®0ЎҜЎЈ*/

- library ieee;

- use ieee.std_logic_1164.all;

- entity YMQ is

- port(xyk: in std_logic_vector(3 downto 0);

- dnf: out std_logic_vector(8 downto 0));

- end YMQ;

- architecture bh4 of YMQ is

- begin

- process(xyk)

- begin

- case xyk is

- when "0000" => dnf <= "100111111";

- when "0001" => dnf <= "100000110";

- when "0010" => dnf <= "101011011";

- when "0011" => dnf <= "101001111";

- when "0100" => dnf <= "101100110";

- when "0101" => dnf <= "100101001";

- when "0110" => dnf <= "101111101";

- when "0111" => dnf <= "100000111";

- when "1000" => dnf <= "101111111";

- when "1001" => dnf <= "101100111";

- when others => dnf <= "100111111";

- end case;

- end process;

- end bh4;

-

-

-

-

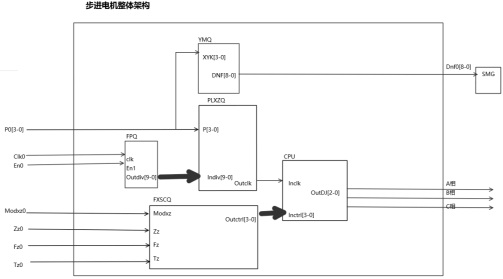

- //********ЧЬМеЈәДЈҝйөДАэ»Ҝ*************//

- library ieee;

- use ieee.std_logic_1164.all;

- entity zong is

- port(clk0,en0,Modxz0,Zz0,Fz0,Tz0 : in std_logic;

- P0 : in std_logic_vector(3 downto 0);

- DNF0 : out std_logic_vector(8 downto 0);

- OutDJ0 : out std_logic_vector(2 downto 0));

- end zong;

- architecture bh0 of zong is

- component FPQ

- port(clk,en1: in std_logic;

- outdiv : out std_logic_vector(9 downto 0));

- end component;

- component PLXZQ

- port(p: in std_logic_vector(3 downto 0);

- indiv : in std_logic_vector(9 downto 0);

- outclk : out std_logic);

- end component;

- component YMQ

- port(xyk: in std_logic_vector(3 downto 0);

- dnf: out std_logic_vector(8 downto 0));

- end component;

- component CPU

- port(inclk: in std_logic;

- inctrl: in std_logic_vector(3 downto 0);

- outDJ: out std_logic_vector(2 downto 0));

- end component;

- component FXSCQ

- port(modxz,zz,fz,tz: in std_logic;

- outctrl: out std_logic_vector(3 downto 0));

- end component;

- signal DX1 :std_logic;

- signal DX2 :std_logic_vector(9 downto 0);

- signal DX3 :std_logic_vector(3 downto 0);

- begin

- U0 : FPQ port map (clk0,en0,DX2);

- U1 : PLXZQ port map (p0,DX2,DX1);

- U2 : YMQ port map (p0,dnf0);

- U3 : CPU port map (DX1,DX3,OutDJ0);

- U4 : FXSCQ port map (Modxz0,Zz0,Fz0,Tz0,DX3);

- end bh0;

|

-

-

ОДөө.doc

684.99 KB, ПВФШҙОКэ: 27, ПВФШ»э·Ц: әЪұТ -5

ЖА·Ц

-

ІйҝҙИ«ІҝЖА·Ц

|

№ЬАнФұQQ:125739409;јјКхҪ»БчQQИә281945664

№ЬАнФұQQ:125739409;јјКхҪ»БчQQИә281945664