在FPGA工程设计中,加法器的身影随处可见,加法器看似简单在实际的应用中很容易出错,尤其是在做定点数加法时往往会遇到没有小数点位置对齐导致错误。加法器主要可分为半加器、全加器;按操作数不同可以分定点数加法器、浮点数加法器,针对有符号无符号数也要设计不同的加法器。学习是个由浅及深循序渐进的过程,一开始就从最简单的半加器开始,这里用最简单的加法器熟悉一下FPGA开发流程,建工程的一些规范及怎样写去仿真。

1.一位半加器: 电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。 是实现两个一位二进制数的加法运算电路。半加器不考虑低位的进位

module halfadder(cout,sum,a,b);

outputcout,sum; //不申明,默认是wire变量

input a,b;

assign{cout,sum}=a+b;//cout为进位,sum为和

endmodul

2.全加器 :是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

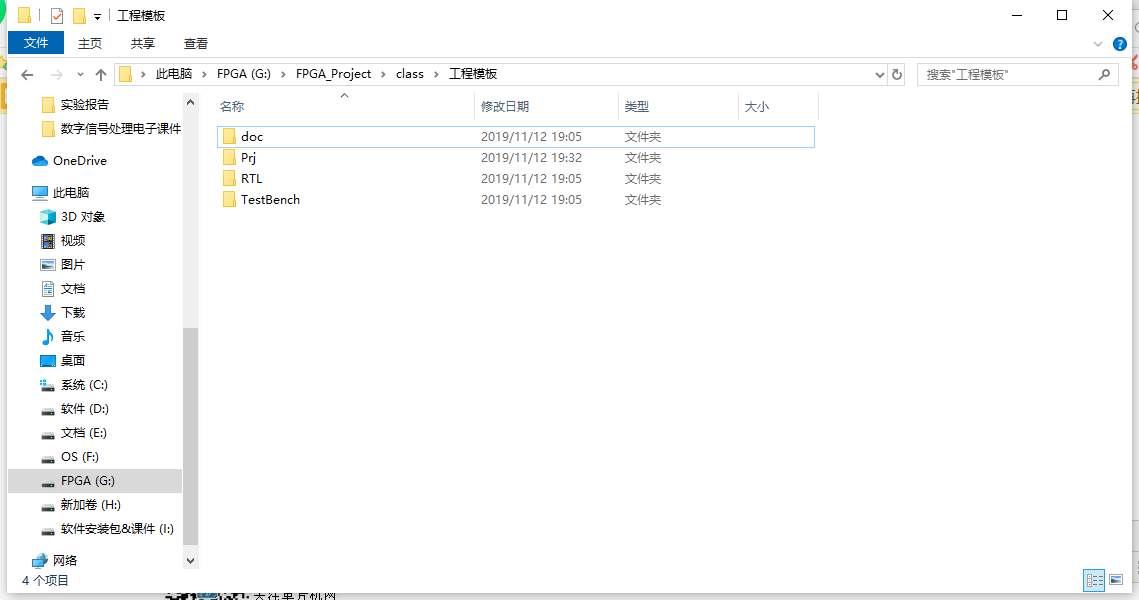

module fulladder(a,b,cin,cout,sum); inputa,b,cin; outputcout,sum; assign{cout,sum}=a+b+cin; endmodule 3.两个半加器构成全加器 module fulladder(x,y,c_in,sum,c_out); inputx; inputy; inputc_in; outputsum; outputc_out; wirea_sum; wirea_out; wireb_out; assignc_out=a_out|b_out; halfadderhalf(x,y,a_sum,a_out); halfadderhalf1(c_in,a_sum,sum,b_out); endmodule 第一步新建一个文件夹 建工程文件夹尽量规范,文件夹下最要包含 doc prj RTL Testbench 文件夹 doc主要放一些工程文档 前期没有可以空着,prj文件夹放工程,及ip核文件,RTL放模块代码.v文件 ,Testbench文件夹放测试激励文件。

工程文件夹模板

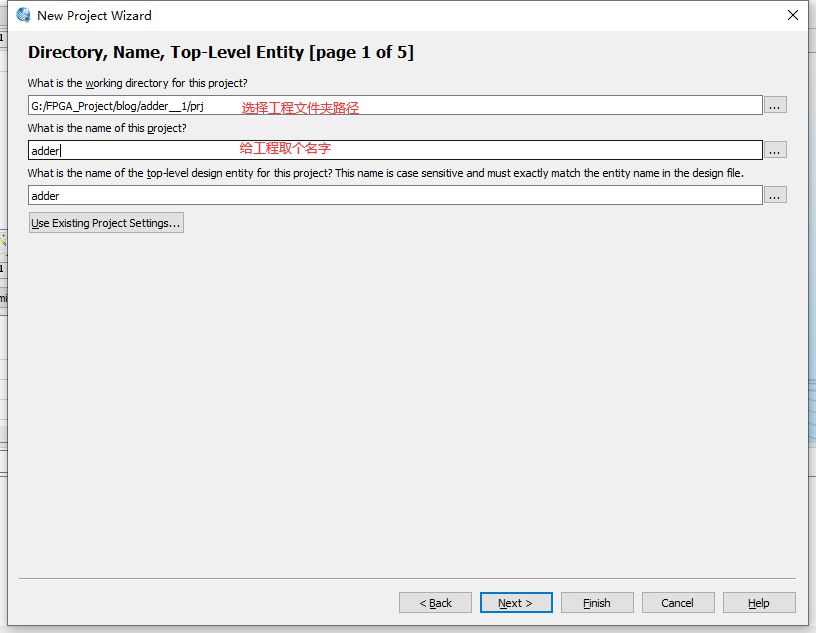

2.打开quartus 软件新建工程,

2.打开quartus 软件新建工程,

选择路径 并给工程命名

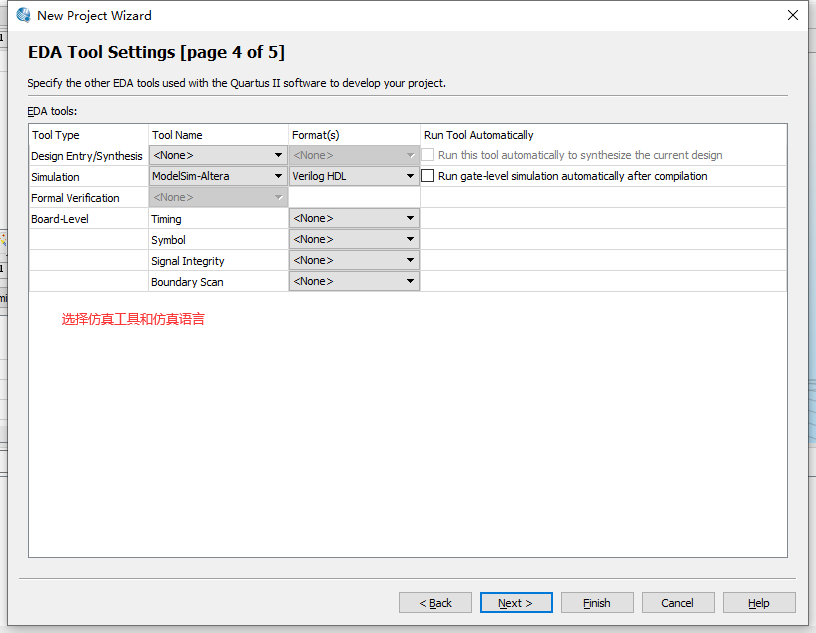

选择仿真工具和语言

选择仿真工具和 仿真语言

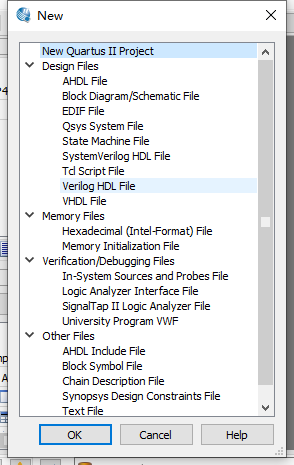

新建.v文件

新建一个verilog文件

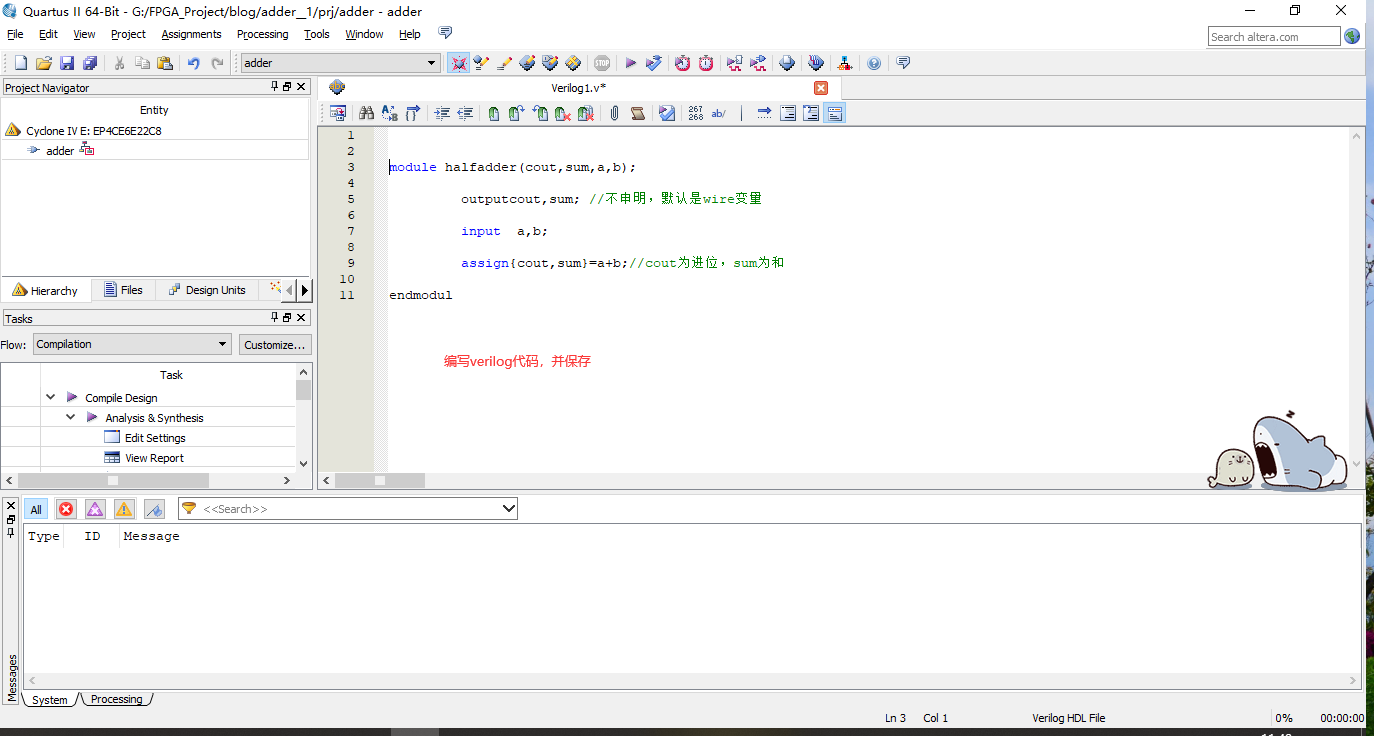

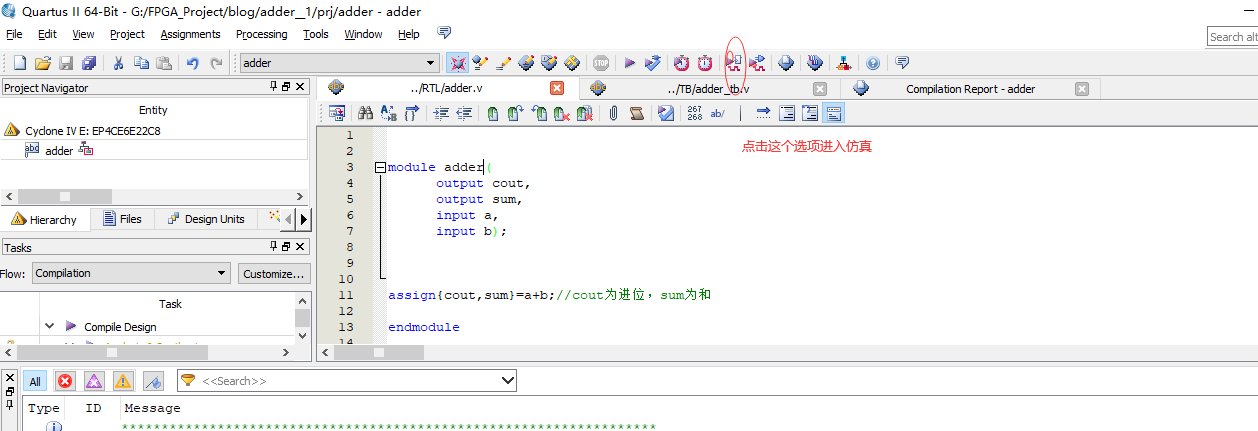

编写代码并保存

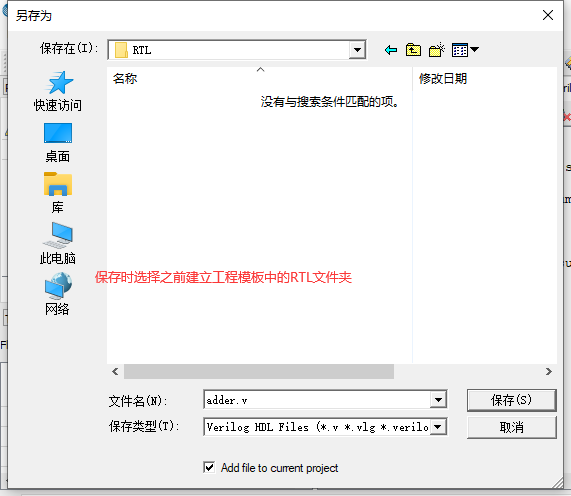

将代码保存到RTL文件夹

再新建一个verilog文件 作为Tb文件 编写tb文件后保存到TB文件下。

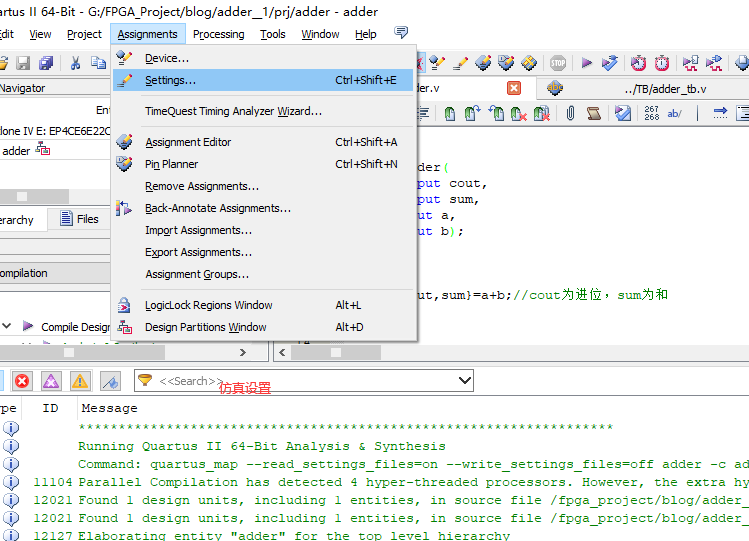

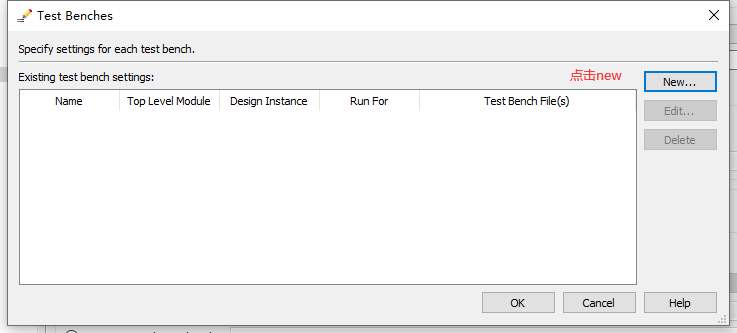

编写完成后需要进行仿真设置。

选择设置菜单

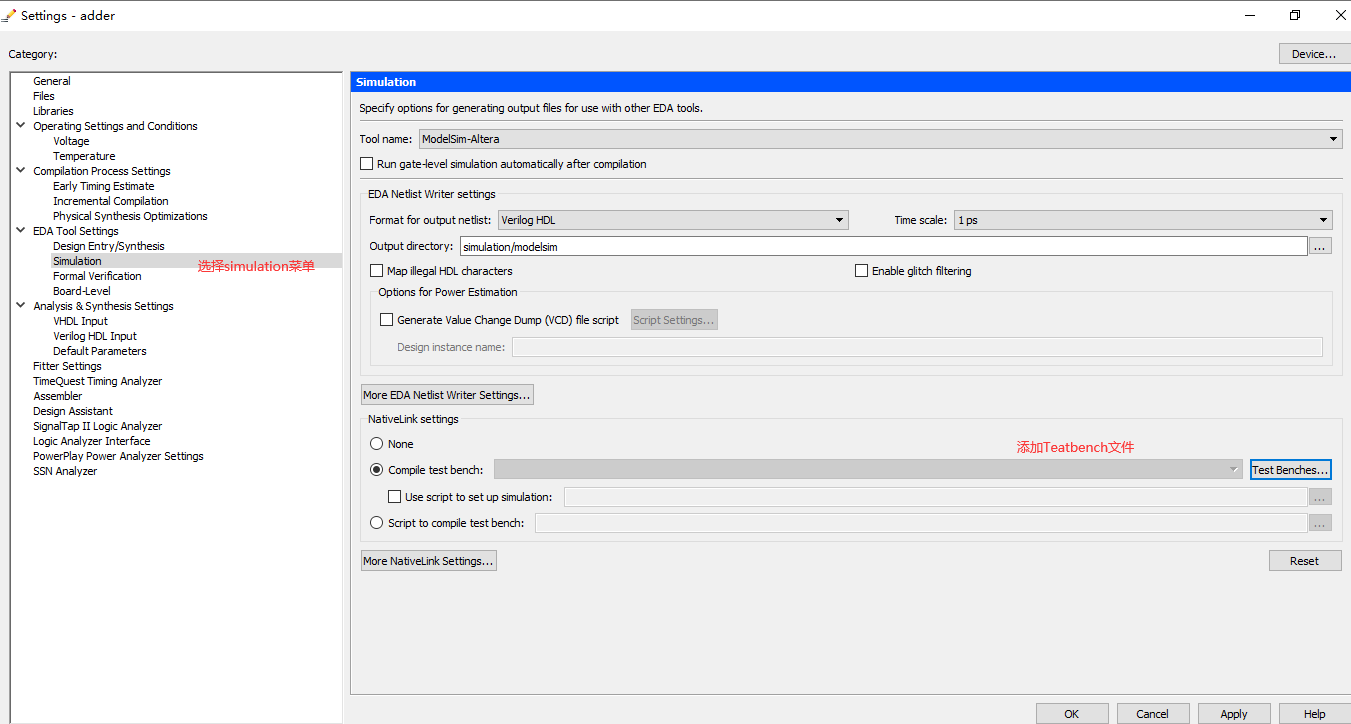

选择simulation设置

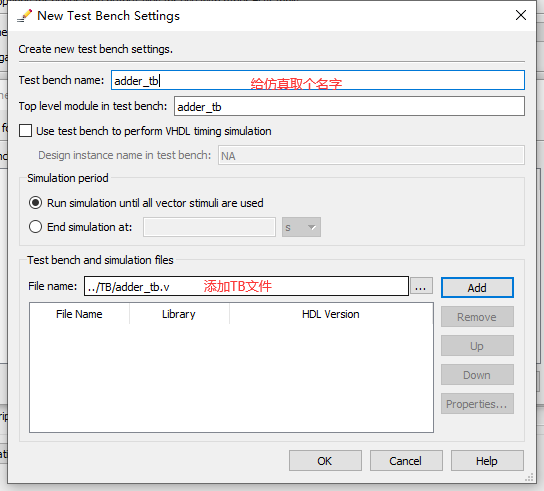

添加TB文件

添加完成后进行仿真

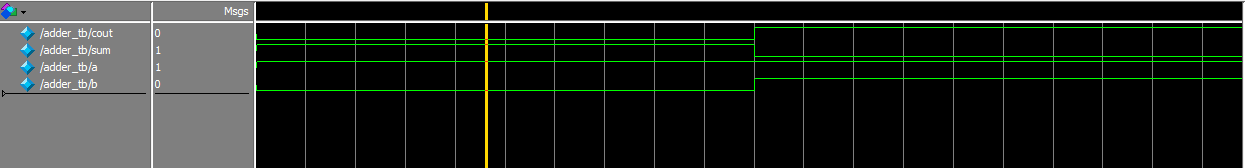

仿真结果

|