|

为了解决在 FPGA 上实现波形可移植性的问题,本文首先提出了一种基于 FPGA 的波形可移植性设计方法。在 FPGA 上实现了抽象层平台的结构化,进而改进了标准的消息格式。最后,本文讨论了连接模型对硬件抽象层的影响,平台的资源消耗及工作效率,并进行抽象层比较多对一的连接模型与一对一的连接模型,得出的结论是,一对一连接模式更合适,FPGA 上的抽象层平台完全解决了波形可移植性这个问题,包括大大降低成本的软件定义开发无线电系统,提高软件无线电系统的可重构性。

软件无线电的概念是由 Joe Mitola 于1992年提出的,目的是提供一个支持多信道、多标准的可重构通信平台。软件无线电的主要思想是构建一个开放、标准化、模块化的通用硬件平台,通过加载不同的波形实现不同的通信模式和功能。波形的可移植性可以降低系统开发成本,有效地提高平台的可重构性,因此波形的可移植性一直是软件无线电系统开发者追求的目标。 随着高速数字信号处理技术的发展,FPGA 在软件无线电系统中得到了广泛的应用。 文献[1]中提出的软件通信体系结构(SCA) ,使用CORBA 中间件有效地解决了通用处理器(GPP)上的波形可移植性问题,但 CORBA 是一种适用于 GPP 的技术,目前在 FPGA 上的应用较少。 目前,FPGA 的波形可移植性问题已成为国内外研究的热点。 为了解决软件无线电波形在 FPGA 上的可移植性问题,提出了软件无线电波形可移植性的软件体系结构,以满足软件无线电波形可移植性的要求。该结构的核心思想是在波形和硬件平台之间建立一个抽象层平台。 Pal 为波形提供了一个标准的、即时的执行期函式库,屏蔽了硬件的差异,从而实现了波形的可移植性。 2. 背景和相关工作

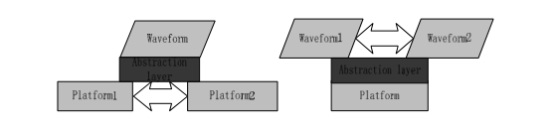

波形可移植性可以定义为将同一波形从一个平台移植到另一个平台的能力,而平台的可重构性对应于 SDR 平台承载不同波形的能力,如图1所示。 从图1可以很容易地得出这样的结论: 如果在平台和波形之间可以实现 PAL 制,从而消除了平台和波形之间的耦合,不仅可以实现波形的可移植性,而且可以实现平台的可重构性。 Pal 为波形提供了标准的执行期函式库,执行期函式库指的是周围的执行环境,包括三个方面: 1)调用和控制组件; 2)提供本地服务和3)标准的通信环境。图1. a)可移植性概念图; b)可重构性概念图 基于这一思想,硬件抽象层层连接(HAL-C)的概念在参考文献[2]中被提出。 定义了波形和平台之间的通信接口原型,标准化了波形和平台之间的通信环境,但是由于上述通信环境只是波形执行期函式库的一部分,因此,硬件抽象层层的连接只是部分解决了波形在 FPGA 上的可移植性问题。 2005年5月下旬,JPO 发布了专用硬件处理器组件可移植性扩展(Extension for component portability for Specialized Hardware Processors,SHP)-Change Proposal 289(CP289)[3] ,并提出了容器的概念。波形可移植性可以通过实现一个提供即时运行时的容器来实现在 FPGA 上实现波形环境。 这个想法很好,但是如何设计容器结构和如何提供一个标准的执行期函式库仍然是一个问题,CP289不能解决这个问题。 目前相关的研究集中在如何实现硬件抽象层层连接上,Eric 为 DSP 提出了一种 PAL 结构,但这种结构并不适合 FPGA。 3.1. 结构 Fpga 的 PAL 制式结构如图2所示。 Pal 制式由互连模块、消息解析模块、消息打包模块、设备 IO 驱动程序的消息接收模块、设备 IO 驱动程序的消息发送模块和本地服务模块组成。 每个 FPGA 芯片都有一个平台抽象。 图2. 平台抽象层结构 设备 IO 驱动程序的消息接收模块从物理信道接收消息,不同的物理信道对应于设备 IO 驱动程序的不同消息接收模块。 设备 IO 驱动程序的消息发送模块向物理信道发送消息,不同的物理信道对应设备 IO 驱动程序的不同消息发送模块。 消息解析模块解析从设备 IO 驱动程序接收的消息,并将解析后的消息提交到互连模块。 消息封装模块封装从互连模块接收的消息,并将已封装的消息提交到设备 IO 驱动程序的消息发送模块。 互连模块控制和维护可能在同一芯片或不同芯片上的不同组件之间的通信,分发由消息解析模块提交的数据消息,并根据消息解析模块提交的控制消息调用正确的组件接口来控制组件。 本地服务模块提供重置服务、时钟服务和本地存储服务。 组件与互连模块之间的接口采用标准的开放核心协议(OCP)接口,组件可以统一使用 PAL 提供的通信环境和本地服务,PAL 也可以统一调用和控制组件。基于所有这些,组件和平台之间的耦合被解耦,因此成为组件具有轻便性。 由于波形由多个元件组成,所以波形具有可移植性。 3.2. 消息格式 为了实现不同 FPGA 芯片之间的互连和互通,采用统一的报文格式是需要的。 参考文献[9]中定义了用于在 SHP 之间传输消息的标准消息格式,如图3所示 图三.标准讯息格式 消息 IU 位用于共享内存的数据接收器和数据源,不适用于不共享内存的处理器。 逻辑目的地(LD)用于将消息路由到目的地数据接收器。每个目标数据接收器都与一个逻辑目的地相关联。 长度用于表示整个信息。 有效负载是消息的有效负载。 标准消息格式存在两个不足。 首先,标准消息格式不区分不同的消息类型。 不仅需要不同组件之间的数据报文通信,而且还需要控制报文通信。 此外,请求消息和响应消息必须加以区分。其次,标准消息格式的通信地址设计降低了组件的重用能力。 如果仅仅使用逻辑目的地来区分 FPGA 芯片上不同组件的不同数据接收接口,同一 FPGA 芯片上所有组件的所有数据接收接口的逻辑目的地必须是不同的,但是组件开发人员只能确保所开发组件的数据接收接口的逻辑目的地是不同的,而不能保证所开发组件的数据接收接口的逻辑目的地与其他开发人员所开发组件的数据接口的逻辑目的地是不同的。 因此,当重用组件时,一个数据接收器接口的逻辑目的地可能与其他接口相同,组件重用失败。 仅使用逻辑目的地指示通信地址将降低组件的重用能力。 为了弥补标准消息格式的不足,本文设计了新的请求消息格式和响应消息格式的标准消息格式,如图4所示。 在请求消息中,目标地址用于指示目标处理器的地址。 Source Address 用于指示源处理器的地址。 目标 LD 用于指示目标组件的地址。 Message Type 用于指示消息是请求消息或响应消息。 响应标志用于指示消息是否需要响应消息。 源 LD 用于指示源组件的地址。 命令用于指示组件数据接口或组件控制接口的地址。 “参数列表”用于指示命令的参数列表。 在响应消息中,“回复状态”用于指示是否发生任何异常。 响应消息中的其他字段与请求消息中的字段相同。 在新的请求消息格式和响应消息格式中,通信地址由处理器地址、组件地址和接口地址表示。 与图3所示的旧的通信地址格式相比,新的通信地址格式具有两大优势。 首先,属于一个组件的接口的寻址独立于属于其他组件的接口的寻址,从而提高了组件的重用能力。 其次,原有的通信地址在消息路由方面导致了设备驱动程序开发与 PAL 制开发的耦合,而新的分段式通信地址使耦合度降低。 设备驱动程序开发人员只需密切关注组件的地址,而 PAL 制式开发人员只需密切关注组件的地址和接口地址,因此降低了开发的复杂性。 图4.请求 / 响应消息格式 3.3. 连接模式

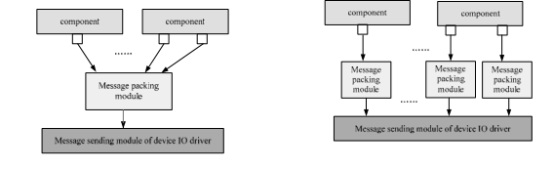

组件接口与消息封装模块之间的连接模型是 PAL 设计中的一个重要问题,它直接影响到 PAL 的资源消耗和工作效率。 有两种不同的连接模型。 一种是多对一连接模型,即所有需要与其他处理器上的其他组件进行通信的接口都连接到同一个消息封装模块,如图5所示。 另一种是一对一的连接模型,不同的接口对应不同的消息封装模块,如图5所示。 图5. a)多对一连接模式 b)一对一连接模式 与一对一连接模式相比,多对一连接模式存在两个不足。 首先,多对一连接模型需要两级缓冲区,因此存储资源消耗较大,处理时延较长;。 在多对一连接模型中,组件接口和消息封装模块之间需要一个缓冲区,以便在多个接口同时需要发送消息时对消息进行缓冲,而消息封装模块也需要一个缓冲区对消息进行缓冲,因此需要两级缓冲区。一对一连接模型只需要一级缓冲区,因为该模型不需要组件接口和消息封装模块之间的缓冲区消息。 其次,由于许多组件接口使用相同的消息打包模块,消息打包模块需要建立一个通信地址表来记录每个接口的地址。 每次在打包消息时,消息打包模块都需要查找地址表以获得正确的接口地址,所以处理延迟会增加。 此外,表查找在 FPGA 上的实现非常复杂。一对一连接模型不需要地址表。 与多对一连接模型相比,一对一连接模型也存在不足。 主要缺点是一对一连接模型需要很多消息打包模块,而多对一连接模型只需要一个。 许多消息打包模块会增加逻辑资源的消耗,但是一对一连接模型中每个消息打包模块的逻辑资源消耗很小,因为消息打包工作很容易。 综合考虑两种不同的连接模型的优点和缺点,一对一的连接模型更为合适。 4. 结论 本文结合现场可编程门阵列(FPGA)的特点和实际应用的需要,首先设计了 PAL 的结构,然后根据标准消息格式的不足,设计了一种新的消息格式来弥补这一不足,最后分析了两种不同的连接模型,得出一对一的连接模型更为合适的结论。 在 FPGA 上实现 PAL 制,完全解决了上述问题。针对软件无线电系统在波形可移植性方面存在的问题,提出了一种软件无线电系统可移植性的解决方案。 另外,PAL 制的结构也适合 DSP,只是实现方式有所不同。

|