基于FPGA的信号发生器,四种波形可调,频率相位可调,(1-999999hz)(幅度+-5V)正弦 三角 方波 锯齿这里使用了某宝的高速的DA模块。所以是在数据发送的时候是并行发送的,至于输出-+5是模块自身集成了放大器和减法器使得移动到-+5

源程序如下:

- `timescale 1ns / 1ps

- //////////////////////////////////////////////////////////////////////////////////

- // Company:

- // Engineer:

- //

- // Create Date: 15:17:29 05/31/2019

- // Design Name:

- // Module Name: FV

- // Project Name:

- // Target Devices:

- // Tool versions:

- // Description:

- //

- // Dependencies:

- //

- // Revision:

- // Revision 0.01 - File Created

- // Additional Comments:

- //

- //////////////////////////////////////////////////////////////////////////////////

- module FV(

- Clk,

- Rst_n,

- k6,

- k5,

- k4,

- k3,

- FV_word

- );

- input Clk;

- input Rst_n;

- input k6;

- input k5;

- input k4;

- input k3;

- output [7:0]FV_word;

-

- reg[3:0]ge,shi;

- /*----------按键模块实例化-------*/

- //k5 个位 +

- wire key_flag, key_state;

- key_filter key_filter0(

- .Clk(Clk),

- .Rst_n(Rst_n),

- .key_in(k5),

- .key_flag(key_flag),

- .key_state(key_state)

- );

- //k6 个位 -

- wire key_flag1, key_state1;

- key_filter key_filter1(

- .Clk(Clk),

- .Rst_n(Rst_n),

- .key_in(k6),

- .key_flag(key_flag1),

- .key_state(key_state1)

- );

- always@(posedge Clk or negedge Rst_n)begin

- if(!Rst_n)

- ge <= 4'd1;

- else if(key_flag && (!key_state))begin

- if((shi!=0))begin

- if(ge==4'd10)begin

- ge <=ge;

- end

- else begin

- ge <= ge + 1'b1;

- end

- end

- else if(ge==4'd10)begin

- ge <=ge;

- end

- else begin

- ge <= ge + 1'b1;

- end

- end

- else if(key_flag1 && (!key_state1))begin

- if((shi!=0))begin

- if(ge==4'd1)begin

- ge <= ge;

- end

- else begin

- ge <= ge - 1'b1;

- end

- end

- else if(ge==4'd1)begin

- ge <= ge;

- end

- else begin

- ge <= ge - 1'b1;

- end

- end

- else

- ge <= ge;

- end

-

- //k4

- wire key_flag0, key_state0;

- key_filter key_filter2(

- .Clk(Clk),

- .Rst_n(Rst_n),

- .key_in(k3),

- .key_flag(key_flag0),

- .key_state(key_state0)

- );

- wire key_flag2, key_state2;

- key_filter key_filter3(

- .Clk(Clk),

- .Rst_n(Rst_n),

- .key_in(k4),

- .key_flag(key_flag2),

- .key_state(key_state2)

- );

-

- always@(posedge Clk or negedge Rst_n)begin

- if(!Rst_n)

- shi <= 4'd0;

- else if(key_flag0 && (!key_state0))begin

- if(shi==4'd9)begin

- shi <=shi;

- end

- else begin

- shi <= shi + 1'b1;

- end

- end

- else if(key_flag2 && (!key_state2))begin

- if(shi==4'd0)begin

- shi <=shi;

- end

- else begin

- shi <= shi - 1'b1;

- end

- end

- else

- shi <= shi;

- end

- /*----------幅度控制-------*/

- assign FV_word=ge*5+shi*21'd10;

- endmodule

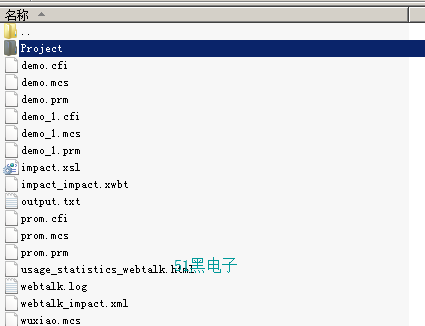

所有资料51hei提供下载:

FPGADDS调幅.7z

(4.22 MB, 下载次数: 75)

FPGADDS调幅.7z

(4.22 MB, 下载次数: 75)

|