|

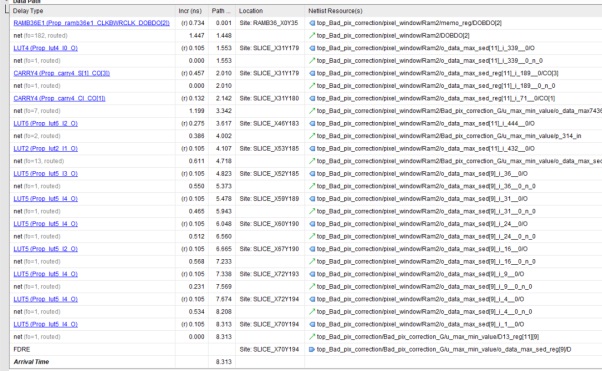

1.ФӯАн ҙ«НіөДЕЕРт·ҪКҪКЗБҪБҪЦ®јдЛіРтҪшРРұИҪПЈ¬¶шИ«ІўРРЛг·ЁКЗ»щУЪРтБРЦРЛжТвБҪёцКэҪшРРұИҪПЈ¬ЛщТФ»бПыәДұИҪП¶аөДұИҪПЖчЎЈХвХэЪ№КНБЛFPGAјјЗЙАпГж»э»»ИЎЛЩ¶ИөДЛјПлЎЈ

ФӯАнИзПВЈә

ЈЁ1Ј©өЪТ»ёцКұЦУЦЬЖЪЈ¬Ҫ«ЖдЦРТ»ёцКэҫЭәНЖдЛыКэҫЭФЪТ»ёцЦЬЖЪЦРұИҪПЎЈ

ЈЁ2Ј©өЪ¶юёцКұЦУЦЬЖЪЈ¬Ҫ«ГҝёцКэҫЭәНЖдЛыКэҫЭұИҪПәуөДҪб№ыҪшРРАЫјУЎЈ

ЈЁ3Ј©өЪИэёцКұЦУЦЬЖЪЈ¬Ҫ«ГҝёцКэҫЭёщҫЭЧФјәөДөГ·ЦёіЦөёшРВөДКэЧйЎЈ 2.УЕИұөг 2.1УЕөг ІўРРұИҪПЕЕРт·ҪКҪФЪКөКұРФЙПУРГчПФөДУЕКЖЈ¬Ц»РиТӘИэёцКұЦУЦЬЖЪҫНҝЙТФНкіЙЕЕРтЎЈ 2.2Иұөг УЙУЪІўРРұИҪППыәДFPGAөДLUTЧКФҙЈ¬¶шЗТФЪөЪ¶юёцҪЧ¶ОРиТӘҙуБҝөДјУ·ЁЖчј¶БӘЈ¬ҝјВЗөҪВ·ҫ¶СУіЩЎўҪЁБўәНұЈіЦКұјдөДSlackТФј°КұЦУөДJitterЈ¬Т»ёцКұЦУЦЬЖЪөД¶аёцјУ·ЁЖчј¶БӘ»бІъЙъОКМв

ҙъВлөДҝЙТЖЦІРФУРЛщЗ·ИұЈ¬ұИИзРтБРҙуРЎёДұдЈ¬ФЪөЪ¶юәНөЪИэҪЧ¶ОҫНРиТӘИПОӘРЮёД¶аҙҰҙъВлЎЈ 3.ҙ«НіөДЕЕРтАэіМ ИзПВНјЛщКҫЈ¬І»ҪцРиТӘ¶аёцұИҪПЖчЈ¬¶шЗТКұРтВ·ҫ¶№эіӨЈ¬ФміЙІјПЯөДКэҫЭВ·ҫ¶№эіӨЈ¬ІъЙъҪЁБўКұјдОҘАэЎЈ

ҙУПВГжөДtimingұЁёжЦРҝЙТФГчПФөДҝҙіцЈ¬ёГКэҫЭ№эіӨЎЈ

ТІҝЙТФҙУРҫЖ¬ІјПЯөДЗйҝцЙПГчПФҝҙіцЎЈ

4.И«ІўРРұИҪПАэіМ

module sort_paralell(clk, rst, in0, in1, in2, in3, out0, out1, out2, out3);

input clk;

input rst;

input [7:0] in0, in1, in2, in3;//КдИлөД4ёцРиТӘұИҪПөДКэЧЦ

reg [7:0] out_temp[3:0];//КдіцКэҫЭ·ЕИлҙЛКэЧйЦР

output [7:0] out0, out1, out2, out3;//КдіцөДұИҪПәуөДҪб№ы

reg [7:0] out0, out1, out2, out3;

//ПВГж¶ЁТеөДұдБҝУГУЪҙжҙўұИҪПҪб№ыЈ¬Изin0 > in1,Фтa0 <= 1,·сФтa0 <= 0;

reg a0, a1, a2;

reg b0, b1, b2;

reg c0, c1, c2;

reg d0, d1, d2;

reg add_start; //ёГұдБҝөДЧчУГКЗЕР¶ПұИҪПКЗ·сҪбКшЈ¬ұИҪПҪбКшәуёіЦөОӘ1Ј¬ҪшИлПајУДЈҝй

reg assignm_start; //ёГұдБҝЧчУГФЪУЪЕР¶ППајУДЈҝйЦҙРРКЗ·сҪбКшЈ¬ҪбКшәуёіЦөОӘ1Ј¬ҪшИлПВТ»ёцКдіцДЈҝй

//ПВГж¶ЁТеөДұдБҝУГУЪҙжҙўЙПКцЦРјдұдБҝАЫјУҪб№ыЈ¬ЈЁ9ёц1О»2ҪшЦЖКэПајУЧо¶а4О»Ј©2өДЈЁ0,1,2,3Ј©ҙО·ҪөДАЫјУЈ¬ДЗГҙ4ёц1О»өД2ҪшЦЖКэПајУЧо¶а3О»Ј¬2өДЈЁ0,1,2Ј©өДАЫјУ

reg out_start;

//reg [3:0] mid0, mid1, mid2, mid3, mid4, mid5, mid6, mid7, mid8, mid9;

reg [2:0] mid0, mid1, mid2, mid3;//4 input numbers

//ЕЕРтЛг·ЁФЪFPGAДЪҪшРРЈ¬КөПЦ№эіМЦчТӘУРТФПВјёёцІҪЦиЈә

//1ЎўөЪТ»ёцclkЈ¬КэҫЭөДИ«ұИҪПіМРтЈ¬4ёцКэҫЭЕЕРтЈ¬КдИлКэҫЭОӘin0~in3;

//2ЎўөЪ¶юёцclkЈ¬ұИҪПЦөАЫјУЈ¬mid0,mid1,mid2,mid3;

//3ЎўөЪИэёцclkЈ¬°СКдИлЦөёіёшПа¶ФУҰөДЕЕРтҝХјдЈ»

//4ЎўөЪЛДёцclkЈ¬°СЕЕРтҪб№ыКдіцЈ»

//ІўРРұИҪПДЈҝйЈЁөЪТ»ёцКұЦУЈ©

always @ (posedge clk)

begin

if(rst)

begin

{a0, a1, a2} <= 3'b0000_0000_0;

{b0, b1, b2} <= 3'b0000_0000_0;

{c0, c1, c2} <= 3'b0000_0000_0;

{d0, d1, d2} <= 3'b0000_0000_0;

{mid0, mid1, mid2, mid3} <=

30'b0000_0000_0000_0000_0000_0000_0000_0000_0000_0000;

out0 <= 0; out1 <= 0; out2 <= 0; out3 <= 0;

add_start <= 0;

assignm_start <= 0;

out_start <= 0;

end

else

begin

if(in0 > in1) a0 <= 1'b1; //in0әНЛщУРіэЧФјәНвөДЖдЛыКэҫЭұИҪПЈ¬ҙуУЪФтұкЦҫЦГ1

else a0 <= 1'b0;

if(in0 > in2) a1 <= 1'b1;

else a1 <= 1'b0;

if(in0 > in3) a2 <= 1'b1;

else a2 <= 1'b0;

if(in1 > in0) b0 <= 1'b1;//in1әНЛщУРіэЧФјәНвөДКэҫЭұИҪПЈ¬ҙуУЪұкЦҫО»ЦГ1Ј¬·сФтОӘ0

else b0 <= 1'b0;

if(in1 > in2) b1 <= 1'b1;

else b1 <= 1'b0;

if(in1 > in3) b2 <= 1'b1;

else b2 <= 1'b0;

if(in2 > in0) c0 <= 1'b1;

else c0 <= 1'b0;

if(in2 > in1) c1 <= 1'b1;

else c1 <= 1'b0;

if(in2 > in3) c2 <= 1'b1;

else c2 <= 1'b0;

if(in3 > in0) d0 <= 1'b1;

else d0 <= 1'b0;

if(in3 > in1) d1 <= 1'b1;

else d1 <= 1'b0;

if(in3 > in2) d2 <= 1'b1;

else d2 <= 1'b0;

add_start <= 1; //ұИҪПҪбКшұкЦҫЈ¬ПајУҝӘКјұкЦҫ

end

end

//ПајУДЈҝйЈ¬midЈЁiЈ©өДЦөҙъұнЧЕinЈЁiЈ©ЛщФЪКдіцКэЧйЦРөДО»ЦГЈ¬ЈЁөЪ¶юёцКұЦУЈ©

always @ (posedge clk)

begin

if(add_start == 1)

begin

mid0 <= a0 + a1 + a2; //ұкЦҫО»ПајУЈ¬ЛщөГҪб№ыҫНКЗЖдЛщФЪО»ЦГ

mid1 <= b0 + b1 + b2;

mid2 <= c0 + c1 + c2;

mid3 <= d0 + d1 + d2;

end

assignm_start <= 1;//ПајУҪбКшЈ¬ёіЦөҝӘКјұкЦҫ

end

//КдіцДЈҝйЈ¬Ҫ«ЕЕРтәГөДКэҫЭ·ЕИлКдіцКэЧйЦРЈЁөЪИэёцКұЦУЈ©

always @ (posedge clk)

begin

if(assignm_start == 1)

begin

out_temp[mid0] <= in0;

out_temp[mid1] <= in1;

out_temp[mid2] <= in2;

out_temp[mid3] <= in3;

out_start <= 1;//ёіЦөҪбКшЈ¬КдіцҝӘКјұкЦҫО»

end

end

always @ (posedge clk)

begin

if(out_start == 1)

begin

out0 <= out_temp[0];

out1 <= out_temp[1];

out2 <= out_temp[2];

out3 <= out_temp[3];

end

end

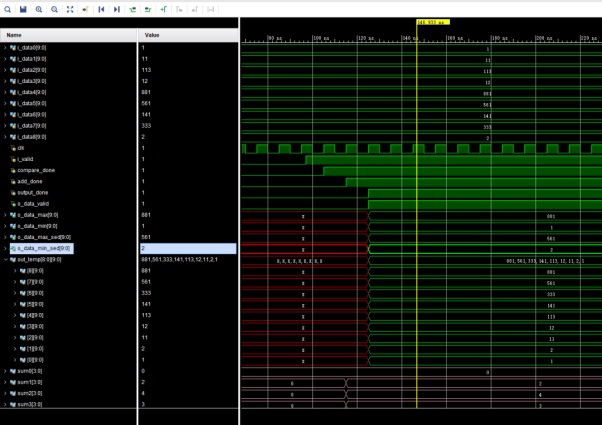

endmodule ЙПКцҙъВлҪц№©ІОҝјЈ¬ПВНј·ВХжҪб№ыОӘ9ёцКэҫЭҪшРРЕЕРтөДКдіцҪб№ыЎЈ

ҝЙТФҝҙөҪЦ»РиТӘЛДёцКұЦУЦЬЖЪҫНҝЙТФөГөҪЕЕРтҪб№ыЎЈ

ТФЙПөДWordёсКҪОДөө51әЪПВФШөШЦ·Јә |

№ЬАнФұQQ:125739409;јјКхҪ»БчQQИә281945664

№ЬАнФұQQ:125739409;јјКхҪ»БчQQИә281945664