③ 用EDA上的8只八段数码管分两屏分别显示年、月、日和时、分、秒,即在一定时间段内显示年、月、日(如20080101),然后在另一时间段内显示时、分、秒(如00123625),两个时间段能自动倒换。

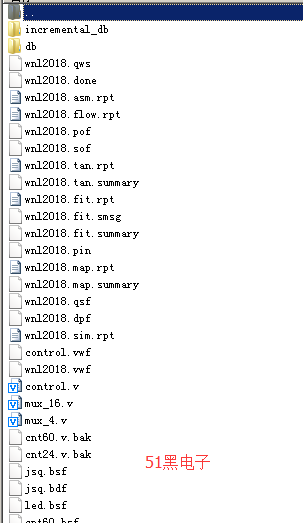

用verilogHDL语言该设计中总体包括显示部分、计时部分、控制部分、校时部分、年月日部分以及分频功能再加上自己的创新。然后调试出来,下载到箱验证。

模块(control),校时选择模块(mux_4)和显示选择模块(mux_16)还有奇数月份报时模块(led),分频模块(fenping);奇月报时模块为创新模块,它当在月份为奇数的时候灯光全亮,偶数的时候全灭。

当k=0时,开关j1,j2,j3校秒时分然后将信号分别送到jsq模块的jm(校秒)、jf(校分)、js(校时)。当k=1时,开关j1,j2,j3校年月日然后将信号分别送到wnl2018模块的jr(校日)、jy(校月)、jn(校年)。

clrn是异步清除输入端,低电平有效;clk是时钟输入端,上升沿有效;jm、jf和js分别是校秒、校分、校时输入端;qm[7..0]、qf[7..0]、qs[7..0]分别是年、月、日的输出端;cout是进位。

clk是1秒时钟输入端,k1和k2是控制输入端,当k1k2=00或11时是自动显示模式,控制数码显示器用8秒钟时间显示年、月、日,另外8秒时钟时间显示时、分、秒;当k1k2=01时,仅显示年、月、日,同时用j1,j2,和j3校秒、校分、校时;当k1k2=10时,仅显示年、月、日,同时用j1、j2和j3校日、校月和校年;k是控制输出端。

clrn是异步清除输入端,低电平有效;clk是时钟输入端,上升沿有效;jn、jy和jr分别是校年、校月、校日输入端;qn[15..0]、qy[7..0]、qr[7..0]分别是年、月、日的输出端。

首先,新建一个工程,把编写的程序模块放入进去,再把六十计数器和二十四计数器的分别生成原件符号,然后进行原理图编辑,再连接好24小时计数器的设计同时生成原件符号。最后把各元器件组合起来。编译,仿真,锁定引脚,下载无误后再调试看看能不能实现任务里面要求的功能。

把程序下载后试验箱上能够正确实现年、月、日和时、分、秒的显示和切换。也能通过调节K1和K2来调节年月日和日期的切换,新加的led灯也能实现奇数全亮偶数全灭的效果。

虽然花了很多时间去做,不过我不仅学会如何做万年历,而且更熟练的运用QuartusII9.0软件,对EDA技术有更深入的认识。在做完基本要求之后还创新了一个功能。虽然我创新的思路很简单,但是实际操作中还是遇到了很多困难,比如说自己编写的程序无法实现预期的要求。然后我就去百度和结合自己的程序继续编写代码,有时实在写不出来,我就跑去问老师。在这次中学到了很多很多东西,也增加了自己的思考能力和动手能力。从一开始开题选题,然后再着手设计框图,再到网上查阅相关资料,确定电路图到最终制作成型,每一步都有自己努力的付出。刚开始我做的并不成功,不能显示万年历的结果。但是我相信没有人是一下子就可以做出来的,在成功之前的付出往往是巨大的。于是我对编写的程序进行了认真检查和反复更改,终于我成功的实现了所需的全部功能。这次使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论

分频器模块

module fenping(clk,clk_HZ);

input clk;

output reg clk_HZ;

reg[24:0] counter;

always @(posedge clk)

begin

counter = counter + 1;

if(counter==5000000) counter = 'b0;

else if(counter<=2500000) clk_HZ = 'b0;

else clk_HZ = 'b1;

end

Endmodule

控制模块

module control(clk,k1,k2,k);

input clk,k1,k2;

output reg k;

reg [3:0] qc;

reg rc;

always @(posedge clk)

begin qc=qc+1;

if(qc<8) rc = 0;

else rc = 1;

case ({k1,k2})

0:k = rc;

1:k = 0;

2:k = 1;

3:k = rc;

endcase

end

endmodule

校时选择模块

module mux_4(k,jm,jf,js,jr,jy,jn,j1,j2,j3);

input k,j1,j2,j3;

output reg jm,jf,js,jr,jy,jn;

always

begin

if(k==0) {jm,jf,js}={j1,j2,j3};

else {jr,jy,jn} = {j1,j2,j3};

end

endmodule

显示选择模块

module mux_16(k,qm,qf,qs,qr,qy,qn,q);

input k;

input[7:0] qm,qf,qs,qr,qy;

input[15:0] qn;

output reg[31:0] q;

always

begin

if(k==0) begin

q[31:24] = 0;

q[23:0] = {qs,qf,qm}; end

else q={qn,qy,qr};

end

endmodule

年月日模块

module wnl2018(clrn,clk,jn,jy,jr,qn,qy,qr);

input clrn,clk,jn,jy,jr;

output [15:0] qn;

output [7:0] qy,qr;

reg [15:0] qn;

reg[7:0] qy,qr;

reg clkn,clky;

reg [7:0] date;

reg clkn1,clkn2,clkn3;

initial begin clkn1 = 1;clkn2 = 1;clkn3 = 1;end//初始化年脉冲

initial begin qn = 'h2000;qy = 1;qr = 1;end//初始化年,月,日时间

always @(posedge (clk^jr) or negedge clrn)//日计数模块

begin

if(~clrn) qr = 1;

else begin

if(qr==date) qr = 1;

else qr=qr+1;

if(qr[3:0] == 'ha) begin

qr[3:0] = 0;qr[7:4] = qr[7:4] + 1;end

if(qr==date) clky = 1;

else clky = 0;end

end

always @(posedge clky^jy or negedge clrn)//月计数模块

begin

if(~clrn) qy = 1;

else begin

if(qy=='h12) qy = 1;

else qy=qy+1;

if(qy[3:0] == 'ha) begin

qy[3:0] = 0;qy[7:4] = qy[7:4] + 1;end

if(qy=='h12) clkn = 1;

else clkn = 0;end

end

always

begin

case(qy)

'h01: date = 'h31;

'h02: begin

if((qn/4==0)&(qn/100!=0)|(qn/400==0)) date = 'h29;

else date = 'h28;end

'h03: date = 'h31;

'h04: date = 'h30;

'h05: date = 'h31;

'h06: date = 'h30;

'h07: date = 'h31;

'h08: date = 'h31;

'h09: date = 'h30;

'h10: date = 'h31;

'h11: date = 'h30;

'h12: date = 'h31;

default: date = 'h30;

endcase

end

//年计数模块

always @(posedge (clkn^jn) or negedge clrn)

begin

if(~clrn) qn[3:0] = 0;

else begin if(qn[3:0]==9) qn[3:0] = 0;

else qn[3:0] = qn[3:0] + 1;

if(qn[3:0] == 9) clkn1 = 0;

else clkn1 = 1;end

end

always @(posedge clkn1 or negedge clrn)

begin

if(~clrn) qn[7:4] = 0;

else begin if(qn[7:4]==9) qn[7:4] = 0;

else qn[7:4] = qn[7:4] + 1;

if(qn[7:4]==9) clkn2 = 0;

else clkn2 = 1;end

end

always @(posedge clkn2 or negedge clrn)

begin

if(~clrn) qn[11:8] = 0;

else begin if(qn[11:8] == 9) qn[11:8] = 0;

else qn[11:8] = qn[11:8] + 1;

if(qn[7:4] == 9) clkn3 = 0;

else clkn3 = 1;end

end

always @(posedge clkn3 or negedge clrn)

begin

if(~clrn) qn[15:12] = 2;

else if(qn[15:12]==9) qn[15:12] = 0;

else qn[15:12] = qn[15:12] + 1;

end

endmodule

Led灯模块

module led(months,qledout);

input [7:0]months;

output reg [11:0] qledout;

always

begin

if(months%2)

begin

qledout = 'b111111111111;

end

else qledout = 'b000000000000;

end

endmodule

六十进制计数器模块

module cnt60(clk,clrn,j,q,cout);

input clk,clrn,j;

output reg[7:0] q;

output reg cout;

always @(posedge clk^j or negedge clrn)

begin

if(~clrn) q = 0;

else begin

if(q=='h59) q= 0;

else q=q+1;

if(q[3:0]=='ha) begin

q[3:0] = 0; q[7:4]=q[7:4] + 1;end

if(q=='h59) cout = 1;

else cout = 0; end

end

endmodule

二十四进制计数器模块

module cnt24(clk,clrn,j,q,cout);

input clk,clrn,j;

output reg [7:0] q;

output reg cout;

always @(posedge clk^j or negedge clrn)

begin

if(~clrn) q = 0;

else begin

if(q=='h23) q= 0;

else q = q+1;

if(q[3:0] == 'ha) begin

q[3:0] = 0;q[7:4] = q[7:4] + 1;end

if(q == 'h23) cout=1;

else cout = 0;end

end

Endmodule

全部资料51hei下载地址:

数字日历.zip

(1.21 MB, 下载次数: 92)

数字日历.zip

(1.21 MB, 下载次数: 92)

数字日历.doc

(202 KB, 下载次数: 44)

数字日历.doc

(202 KB, 下载次数: 44)