КЌЪБжгЪЙФмЕФЪЎНјжЦМЦЪ§ЦїЕФЩшМЦЃЌQuartus II 9.0 ШэМўПЊЗЂЃЌбЇЯАЪЙгУQuartus II 9.0ШэМўЃЌеЦЮеVHDLЮФБОУшЪіКЭдРэЭМУшЪіЕФRTLМЖУшЪіЗНЗЈЃЌеЦЮеМЦЪ§ЦїЕФУшЪіЗНЗЈЁЃЛљгк74390ЕФЪЎНјжЦМЦЪ§ЦїЕФЩшМЦЃЌКЌЪБжгЪЙФмЕФ2ЮЛЪЎНјжЦМЦЪ§ЦїЕФЩшМЦКЭКЌЪБжгЪЙФмЕФ60НјжЦМЦЪ§ЦїЕФЩшМЦЁЃ

1ЁЂеЦЮеРћгУQuartus II 9.0 ШэМўПЊЗЂЪ§зжЕчТЗЕФЛљБОСїГЬвдМАеЦЮеQuartus IIШэМўЕФЯъЯИВйзїЁЃ 2ЁЂеЦЮеЪЙгУVHDLдРэЭМЩшМЦНјааМЏГЩЕчТЗЯЕЭГЩшМЦЕФЪЕЯжЗНЗЈЁЃ

Жў ЪЕбщЧАЕФзМБИ 1ЁЂДђПЊМЦЫуЛњЕчдДЃЌдЫааQuartus IIШэМўЁЃ 2ЁЂЙЄГЬЮФМўашвЊБЃДцдкDХЬЙЄзїЮФМўМажаЃЌБОЩшМЦашвЊБЃДц3ИіЙЄГЬЃЌЧыЮЊЦфЩшЖЈ3ИіЖРСЂЕФЮФМўМаЁЃБОДЮЪЕбщЙЄзїЮФМўМаЮЊexp3ЃЌдкexp3ЯТдйНЈ3ИіЮФМўМаCNT10ЁЂCNTD10ЁЂCNT60ЃЌЗжБ№НЋЪЎНјжЦМЦЪ§ЦїЁЂЫЋЪЎНјжЦМЦЪ§ЦїЁЂ30НјжЦМЦЪ§ЦїЕФЙЄГЬБЃДцдкЖдгІЮФМўМажаЁЃ

Ш§ ЪЕбщвЊЧѓ бЇЯАЪЙгУQuartus II 9.0ШэМўЃЌеЦЮеVHDLЮФБОУшЪіКЭдРэЭМУшЪіЕФRTLМЖУшЪіЗНЗЈЃЌеЦЮеМЦЪ§ЦїЕФУшЪіЗНЗЈЁЃ

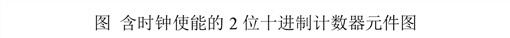

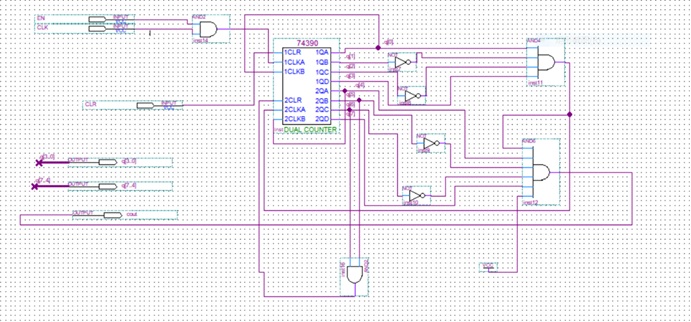

ЫФ ЪЕбщФкШн ЃЈвЛЃЉЛљгк74390ЕФЪЎНјжЦМЦЪ§ЦїЕФЩшМЦ 1ЁЂЪЎНјжЦМЦЪ§ЦїЕФЩшМЦдРэЃЌВЩгУ74390зїЮЊЪЎНјжЦМЦЪ§ЦїЃЌзЂвт74390ЕФЙЄзїдРэЁЃ

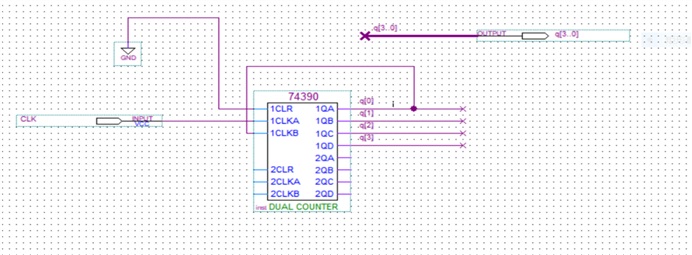

зЂвтЃКЭМжаДжЯпq[3..0]ДњБэзмЯпЃЌЯИЯпq[0]-q[3]ДњБэзмЯпжаЕФЕЅИљЯпЁЃгвМќЕуЛїДж/ЯИЯпЃЌбЁдёPropertiesЃЌПЩЮЊСЌНгЯпУќУћЁЃдкЭМЩЯПДЃЌq[0]-q[3]гыq[3..0]ЪЧЖЯПЊЕФЃЌОзлКЯКѓЃЌДЫСНВПЗжЛсБЛEDAЙЄОпздЖЏСЌЩЯЁЃвђДЫЃЌЯрЭЌУћГЦЕФЯпЛсдкзлКЯЪБздЖЏСЌНгЩЯЁЃ 2ЁЂНЈСЂЙЄГЬCNT10ЃЌНЈСЂдРэЭМЮФМўCNT10ЃЌЬэМг74390дЊМўЃЌЭъГЩЪЎНјжЦМЦЪ§ЦїЕФЩшМЦЗНАИЁЃЖдЪЎНјжЦМЦЪ§ЦїЕФЩшМЦЗНАИНјааЪБађЗТецЃЌНЋЗТецВЈаЮаДШыЪЕбщБЈИцЁЃ ЃЈЖўЃЉКЌЪБжгЪЙФмЕФ2ЮЛЪЎНјжЦМЦЪ§ЦїЕФЩшМЦ 1ЁЂКЌЪБжгЪЙФмЕФ2ЮЛЪЎНјжЦМЦЪ§ЦїЕФЩшМЦдРэЭМ

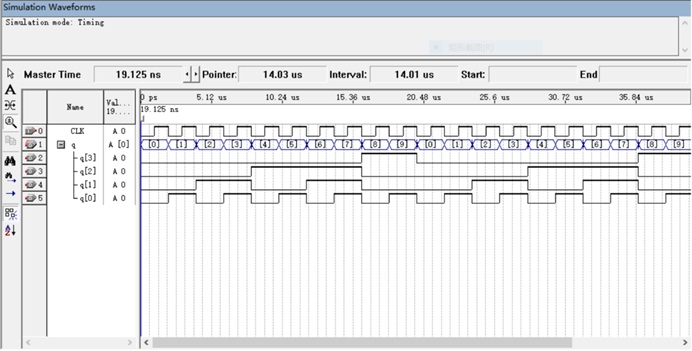

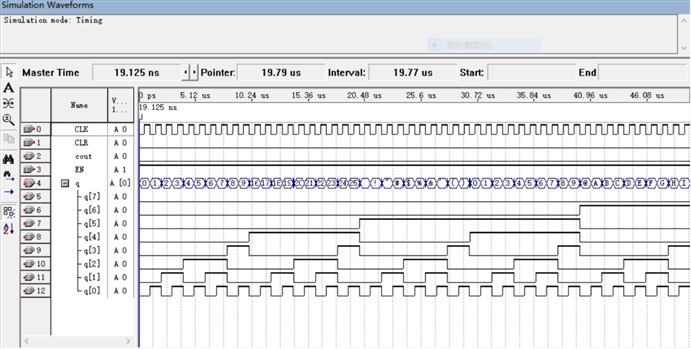

2ЁЂНЈСЂЙЄГЬCNTD10ЃЌНЈСЂдРэЭМЮФМўCNTD10ЃЌЭъГЩКЌЪБжгЪЙФмЕФ2ЮЛЪЎНјжЦМЦЪ§ЦїЕФЩшМЦЗНАИЁЃВЂЖдИУЗНАИНјааЪБађЗТецЃЌНЋЗТецВЈаЮаДШыЪЕбщБЈИцЁЃ ЃЈШ§ЃЉКЌЪБжгЪЙФмЕФ60НјжЦМЦЪ§ЦїЕФЩшМЦ 1ЁЂВЮПМКЌЪБжгЪЙФмЕФ2ЮЛЪЎНјжЦМЦЪ§ЦїЕФЩшМЦдРэЭМЃЌЖддРэЭМНјаааоИФЃЌЭъГЩ60НјжЦМЦЪ§ЦїЕФЩшМЦЗНАИЁЃ 2ЁЂНЈСЂЙЄГЬCNT60ЃЌНЈСЂдРэЭМЮФМўCNT60ЃЌЭъГЩ60НјжЦМЦЪ§ЦїЕФЩшМЦЗНАИЃЌВЂНјааЪБађЗТецЃЌНЋЗТецВЈаЮаДШыЪЕбщБЈИцЁЃ ЫМПМЃК60НјжЦШчКЮЪЕЯжЃПЕБТњзуНјЮЛЬѕМўЪБЃЌМЦЪ§ЧхРэШчКЮЪЕЯжЃП Юх ЪЕбщНиЭМЙ§ГЬ ЪЎНјжЦМЦЪ§ЦїдРэЭМ

ЪЎНјжЦМЦЪ§ЦїЪБађЗТецВЈаЮЭМ

КЌЪБжгЪЙФмЕФ2ЮЛЪЎНјжЦМЦЪ§Цї

КЌЪБжгЪЙФмЕФ2ЮЛЪЎНјжЦМЦЪ§ЦїЪБађЗТецВЈаЮЭМ

КЌЪБжгЪЙФмЕФ60НјжЦМЦЪ§ЦїдРэЭМ

КЌЪБжгЪЙФмЕФ60НјжЦМЦЪ§ЦїЪБађЗТецВЈаЮЭМ

зЪСЯ:

EXP3.zip

(1001.04 KB, ЯТдиДЮЪ§: 10)

EXP3.zip

(1001.04 KB, ЯТдиДЮЪ§: 10)

ЪЕбщ КЌЪБжгЪЙФмЕФЪЎНјжЦМЦЪ§ЦїЕФЩшМЦ.docx

(470.32 KB, ЯТдиДЮЪ§: 5)

ЪЕбщ КЌЪБжгЪЙФмЕФЪЎНјжЦМЦЪ§ЦїЕФЩшМЦ.docx

(470.32 KB, ЯТдиДЮЪ§: 5)

|

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664