包含硬件PCB硬件设计和FPGA的Verilog代码的编写,下图为主要功能框图。FPGA作为处理单元,实现了包括电流和电压的采集、千兆以太网通讯、SD卡本地存储和串口通讯等。已经打PCB板实际验证和Verilog代码在硬件上的实际测试,测试部分包含:千兆网通讯收发测试、AD采集的数据验证、SD卡存储验证、RTC实时时钟读取和RTC的RAM突发读取等。

PCB设计采用的是AD软件,Verilog程序通过quartus II软件编写。现由硬件和软件两个方面简单介绍。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

一、硬件设计

下图分别为硬件的正面和反面,纯手工焊。综合考虑千兆以太网中的高速数据线的差分阻抗100MΩ、数字电源和模拟电源的划分等,PCB主要采用四层板的设计方案。顶层和底层为信号走线层;第二层为完整的地层,分为数字地(DGND)和模拟地(AGND),为顶层的信号层和电位电流模拟量的采集提供参考;第三层为电源层,本层提供较为完整的3.3V电源平面和模拟地平面,还有1.2V和2.5V的电源平面。

其中硬件设计中最要小心的是千兆以太网的设计和电流采集部分。千兆网部分采用的是ETL8211EG芯片,支持千兆以太网,要实现千兆网络,要保证查分阻抗100Ω,就需要考虑蛇形走线和线宽线距、参考层等因素。电流采集部分要考虑模拟地的划分和电流的放大倍数、高精度电阻等,这里我选的是INA240A系列,包含20、50、100、200四种增益可以选择。数模转换是8通道,每通道16位,支持并行的200SPS的AD7606芯片。SD卡就是最常见的Micro SD Card,买的闪迪的16G的卡。RTC是常见的DS1302。考虑版面问题,数码管只留了一个。硬件下载AD源文件下载链接:https://download.csdn.net/download/qq_39521541/15110220

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

AD中的三维图如下:

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

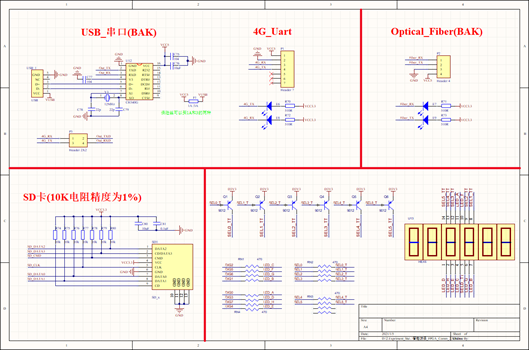

各模块的原理图如下,这是初版 的原理图,实际的硬件在此基础上进行了修改,但是变化不大,就不再截图了。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)[存储通讯和显示电路]( ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)[存储通讯和显示电路]( ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

二、软件程序编写

在以上硬件的基础上编写了程序,总程序5000余行。实现了AD7606电压和电流数据的采集和RTC的时间和内部RAM突发读写,然后并行的存储和通过千兆以太网与串口发送到电脑上。

程序的顶层模块设计如下图:

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

通过电脑上的网络助手同时采集到的串口数据、千兆以太网数据和用Winhex查看的SD卡内存储的数据如下图,数据完全一致。串口数据为什么也用网络助手显示呢,因为我板子上的串口上可以插上一个网络模块,这样串口数据也可以通过无线发送到电脑了,当然硬件上也有有线的串口端子,也进行了验证,不再截图赘述。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

程序主要难点在于逻辑与时序的处理,程序中进行了一些时序的操作。为了方便我理清思路也进行了主要的时序图的绘制,如下图所示,画时序图的软件可以在这里下载https://download.csdn.net/download/qq_39521541/14951291,破解版很好用。 ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

程序的模块结构如下图所示,其中4G其实就是串口,为了进行跨时钟域和SD的闪存,用了双口FIFO、双口RAM、单口RAM、ROM等IP核。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

接下来是编译后的资源占用情况和编译信息,从图中可以看出基本不存在警告,其实现存的三个警告,完全不影响结果,而且知道警告存在的原因即可。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

时序约束部分截图如下,时钟主要约束了50M的系统时钟、25M的SD卡时钟和125M的千兆网时钟。

) )

最后的最后附上总的程序源码:https://download.csdn.net/download/qq_39521541/15110143

感谢大家的批评指正

|