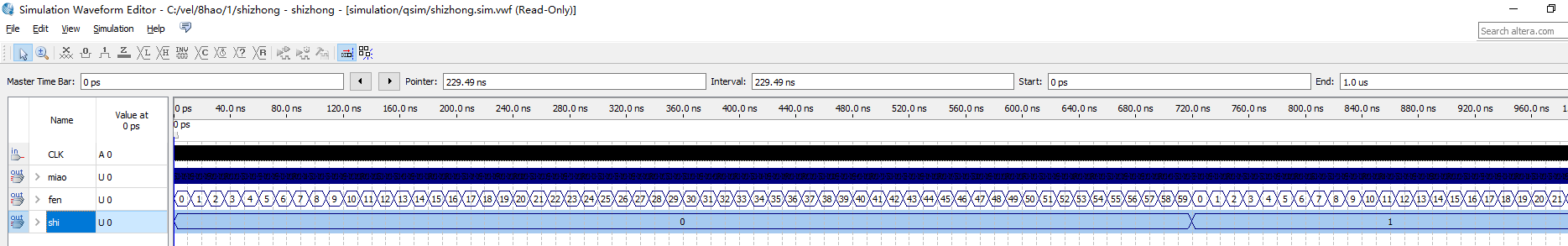

这是之前设计所编写的Verilog数字时钟。

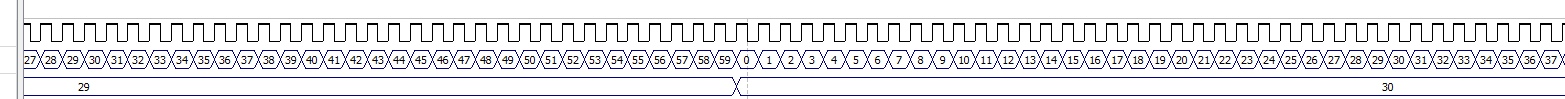

这个设计中,秒进分和分进时部分都采用了一个进位位符号jw,首先每来一个时钟高电平就使秒部分工作,而当秒满了60后,jw就变为1然后用来触发下一部分的工作,同样分部分也是如此。

秒进分

分进秒

总览

程序部分

module shizhong(input CLK,

output reg[5:0] miao,fen,shi);

reg JW,jw;

always @(posedge CLK )

begin

case(miao)

6'B111011:begin miao=0;JW=1;end

default:begin miao=miao+1;JW=0;end

endcase

end

always @(posedge JW )

begin

case(fen)

6'B111011:begin fen=0;jw=1;end

default:begin fen=fen+1;jw=0;end

endcase

end

always @(posedge jw )

begin

case(shi)

6'B000001:begin shi=0;end

default:begin shi=shi+1;end

endcase

end

endmodule

|