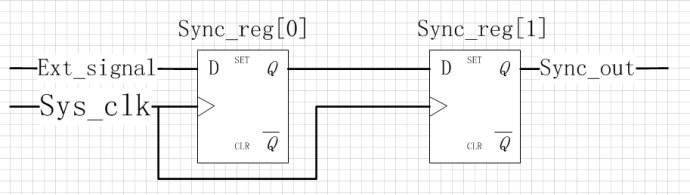

在跨时钟域中,需要对信号同步才能保证系统的稳定。同步的电路设计比较简单,只需通过2个触发器后输出就能达到同步的目的,同时,为了减少亚稳态发生的概率也可通过3个触发器即可完成。

对应的Verilog代码:

module sync(

sys_clk,

ext_singal,

sync_out

);

input sys_clk;

input ext_singal;

output sync_out;

reg sync_out;

reg [1:0] sync_reg;

always @(posedge sys_clk)

begin

sync_reg <= {sync_reg[0],ext_singal};

stnc_out <= sync_reg[1];

end

endmodule

对应的电路图如下:

|