|

|

1、使用条件:阻塞赋值与非阻塞赋值只用于过程赋值语句中,也就是用在always语句和initial语句中,在assign语句中一律用“=”,例如:assign cin = ain + bin,因为本语句为数据流描述方式。

2、赋值对象:

阻塞赋值与非阻塞赋值的赋值对象只能是变量型数据类型,如reg, integer等,一般是reg型

3、区别

阻塞赋值语句:顺序执行,在下一条语句执行之前,上一条语句必须执行完毕。

非阻塞赋值语句:不会阻塞同一个快语句中的其他语句的执行,即各种非阻塞语句同时执行。

例如

例1、module test (i_clk, i_din, o_out1, o_out2);

input i_clk, i_din;

output reg o_out1, o_out2;

always @ (posedge i_clk)

begin

o_out1 = i_din; //语句1

o_out2 = o_out1; //语句2

end

endmodule

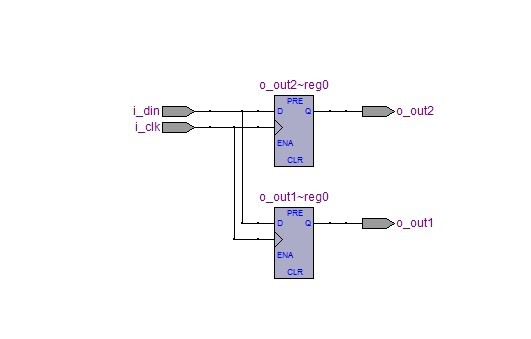

该例子中,先执行语句1,当语句1执行完毕后,再来执行语句2,故执行完毕后

o_out1 = i_din

o_out2 = i_din

于是该电路的RTL图为

例2module test (i_clk, i_din, o_out1, o_out2);

input i_clk, i_din;

output reg o_out1, o_out2;

always @ (posedge i_clk)

begin

o_out1 <= i_din; //语句1

o_out2 <= o_out1; //语句2

end

endmodule

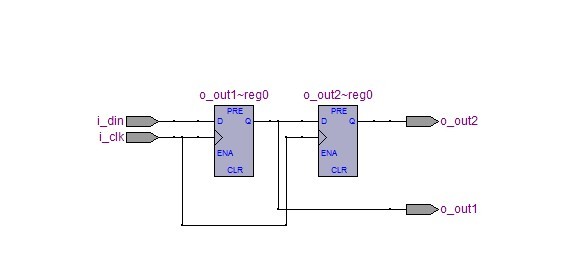

该例子中,语句1和语句2同时执行,故执行完毕后

o_out1 = i_din

o_out2 = 前一时刻的 o_out1

故RTL图为

4、常用规则

1)、当描述时序逻辑时,用非阻塞语句,即“<=”;

2)、当描述组合逻辑时,用阻塞语句,即“=”;

3)、当在一个always模块中,同时描述组合逻辑与时序逻辑时,用非阻塞语句,即“<=”;

4)、在同一个always模块中,不要混合使用阻塞和非阻塞语句。

|

评分

-

查看全部评分

|