|

摘 要 直接数字频率合成(Direct Digital Synthesis,DDS)是20世纪60年代末出现的第三代频率合成技术,该技术从相位概念出发,以时域采样定理为基础,在时域中进行频率合成,它以可编程逻辑器件(CPLD)作为控制及数据处理的核心,可将波形数据用D/A转换器快速恢复。基于CPLD和DDS技术的函数发生器可以实现信号波形的多样化,同时大大提高输出信号的带宽。 整个设计采用MAX+ plus II开发平台,VHDL编程实现,基于可编程逻辑器件CPLD设计多波形信号发生器。用VHDL编程实现,其设计过程简单,极易修改,可移植性强。系统以CPLD为核心,采用直接数字合成技术,辅以必要的模拟电路,构成一个波形稳定,精度较高的函数信号发生器。系统的特色在于除晶体振荡器和A/D转换外,全部集成在一片CPLD芯片上,使系统大大简化。它可输出频率、幅度可调的正弦波、三角波、方波。另外由于CPLD具有可编程重置特性,因而可以方便地更换波形数据,且简单易行,带来极大方便。 关键词:信号发生器设计;三相;VHDL;CPLD;MAX+ plus II ABSTRACT Direct digital frequency synthesize(DDFS) is a recently and rapidly developed technology which features high frequency resolution.This paper briefly introduces the basic principle of DDS. The basic principle and performance of CPLD chip.Then it mainly describes how to use CPLD chip to design a function generator of high accuracy.The principle of three-phase multi-signal generator based on CPLD and DDS technology is introduced.Based on these,the modules of CPLD design are given. The multi-wave signal generator is designed based on program-mable logical component CPLD.The VHDL programming realization and the MAX+ plus II development platform. Besides the crystal oscillator and the A/D transformation,the entire system completely integrates on the CPLD chip.The multi-wave signal generator may output the sine-wave,the triangle-wave,the square-wave.Then downloaded under the situation which the entire system hardware connects do not change,and finally output the special profile which user needs.The multi-wave signal generator generates wave which the conventional function signal generators can’t make.Moreover because of the programmable reset feature of the CPLD,the generator can change the wave data conveniently and practice easily.The whole design realizes by the VHDL programmer.Its design process has simple feature,easy modification and high transportation. Keywords:Signal Generator Design;Three-phase;VHDL;CPLD;MAX+ plus II 目 录 1 引 言 1

2基于CPLD的三相多波形函数发生器设计 3

2.1 波形发生器系统的设计方法及其技术指标 3

2.1.1设计方式概述 3

2.1.2 三相函数多波形发生器技术指标 5

2.1.3三相波形发生器设计方法概述 5

2.2 设计方案 6

2.2.1 三相函数发生器设计原理 6

2.2.2 多波形发生器的各个波形模块设计方式简介 9

2.3 调试部分 12

2.3.1 CPLD在使用中遇到的问题 12

2.3.2 控制电路的调试 13

2.3.3 DAC电路的调试 13

2.3.4 程序的调试 13

2.3.5 硬件电路的调试 13

结 论 15

参考文献 16

附录1 三相多波形函数发生器各模块的程序 17

附录2 元件介绍 23

1 DAC0832 23

2 LM324 24

3 PM7128SLC84-15芯片 25

附录3电路原理图 26

附录4 英文资料及译文 27

1英文资料 27

2英文译文 36

致 谢 43

1 引 言 现代电子技术的核心技术是EDA(Electronic Design Automation)。EDA技术就是依赖强大的电子计算机在EDA开发平台上,对硬件描述语言HDL(Hardware Description Language)系统逻辑描述手段完成的设计文件,自动的完成逻辑编译、逻辑化简、逻辑分割、逻辑综合、结构综合(布局布线),以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。EDA技术使得设计者的工作仅限于利用软件的方式,即利用硬件描述语言和EDA软件来完成对系统硬件功能的实现。 EDA使得电子技术领域各学科的界限更加模糊,更加护为包容:模拟与数字、软件与硬件、系统与器件、行为与结构、ASIC(Application Specific Integrated Circuit,专用集成电路)与FPGA(Field Programmable Gate Array)等。 EDA技术在21世纪得到的很大进步,例如更大规模的FPGA和CPLD(Complex Programmable Logic Device)器件的不断推出;软硬件IP核(Intellectual Property)在电子行业的产业领域、技术领域和设计应用领域得到进一步的确认;系统级、行为验证级硬件描述语言(System C)的出现,使复杂电子系统和验证趋于简单。 硬件描述语言VHDL[全名是VHSIC(Very High Speed Integrated Circuit) Hardware Description Language]是EDA技术的重要组成部分,由美国国防部发起创建,由IEEE (The Institute of Electrical and Electronics Engineers)进一步发展并发布,是硬件描述语言的业界标准之一。 VHDL语言具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大简化了硬件设计任务,提高了设计效率和可靠性。 VHDL具有与具体硬件电路无关和与设计平台无关的特性,并且具有良好的电路行为描述和系统描述的能力,VHDL支持各种模式的设计方法:自顶向下与自顶向上或混合方法,在面对当今电子产品生命周期缩短,需要多次重新设计以融入最新技术、改变工艺等方面,VHDL具有良好的适应性。 向器件作编程或适配习惯上叫做下载,这要通过下载软件平台或者下载电缆实现。这是设计过程中的重要步骤,可以利用MAX+PLUSⅡ软件在计算机上完成设计并下载到目标器件中。EDA工具软件大致可以分为5个模块:设计输入编辑器,仿真器,HDL综合器,适配器,下载器等。 Direct Digital Synthesis(DDS)是20世纪60年代末出现的第三代频率合成技术。该技术从相位概念出发,以时域采样定理为基础,在时域中进行频率合成,它以可编程逻辑器件(CPLD)作为控制及数据处理的核心,将存于Flash ROM的波形数据用D/A转换器快速恢复。DDS频率转换速度快,频率分辨率高,并在频率转换时可保持相位的连续,因而易于实现多种调制功能。DDS是全数字化技术,其幅度、相位、频率均可实现程控,并可通过更换波形数据灵活实现任意波形。此外,DDS易于单片集成,体积小,价格低,功耗小,因此DDS技术近年来得到了飞速发展,其应用也越来越广泛。基于CPLD和DDS技术的函数发生器可以实现信号波形的多样化,而且方便可靠,简单经济,系统易于扩展,同时可大大提高输出信号的带宽。 CPLD为连续式互连结构,器件引脚到内部逻辑单元,以及各逻辑单元之间,是通过全局互连总线中的多路选择器或交叉矩阵选通构成信号通路。其主要特点是内部时间延时与器件逻辑结构等无关,各模块之间提供了具有固定时延的快速互连通道,因此可以预测时间延时,容易消除竞争冒险等现象,便于各种逻辑电路设计。 本文的DDS系统以CPLD为核心,采用直接数字合成技术,辅以必要的模拟电路,构成一个波形稳定,精度较高的函数信号发生器。本系统的特色在于CPLD中集成了大部分电路,使系统大大简化,除输出所需的正弦波、方波、三角波,还可进行波形存储,三种波形之间的相位差均为120°,是三相的CPLD系统。 DDS的理论依据是奈奎斯特抽样定理。根据该定理,对于一个周期正弦波连续信号,可以沿其相位轴方向,以等量的相位间隔对其进行相位/幅度抽样,得到一个周期性的正弦信号的离散相位的幅度序列,并且对模拟幅度进行量化,量化后的幅值采用相应的二进制数据编码。这样就把一个周期的正弦波连续信号转换成为一系列离散的二进制数字量,然后通过一定的手段固化在只读存储器ROM 中,每个存储单元的地址即是相位取样地址,存储单元的内容是已经量化了的正弦波幅值。这样的一个只读存储器就构成了一个与2π周期内相位取样相对应的正弦函数表,因它存储的是一个周期的正弦波波形幅值,因此又称其为正弦波形存储器。此时,正弦波形信号的相位与时间成线性关系。根据这一基本关系,在一定频率的时钟信号作用下,通过一个线性的计数时序发生器所产生的取样地址对已得到的正弦波波形存储器进行扫描,进而周期性地读取波形存储器中的数据,其输出通过数模转换器及低通滤波器就可以合成一个完整的、具有一定频率的正弦波信号。DDS电路一般包括系统时钟、相位累加器、相位调制器、ROM 查找表、D/A转换器和低通滤波器(LPF)。 基于CPLD和DDS技术的函数发生器可以实现信号波形的多样化,而且方便可靠,简单经济,系统易于扩展,同时可大大提高输出信号的带宽。

2基于CPLD的三相多波形函数发生器设计 2.1 波形发生器系统的设计方法及其技术指标 2.1.1设计方式概述

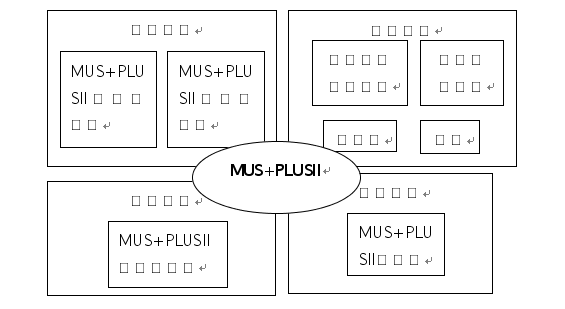

在电子工程设计与测试中,常常需要一些具有特殊要求的信号,要求其波形产生多,频率方便可调。通常的信号产生器难以满足要求,市场上出售的任意信号产生器价格昂贵。在老师指导下,结合实际要求,我设计了一种基于CPLD的三相多波形函数发生器,能输出正弦波、三角波、方波等波形信号,波形信号之间的相位差均为120˚。 复杂可编程逻辑器件CPLD器件可以代替许多分立元器件,从而大大降低了电路板的复杂程度。对于CPLD器件的设计一般可以分为设计输入、设计实现和器件编程三个设计步骤以及相应的功能仿真、时序仿真和器件测试三个设计验证过程。 设计输入有多种方式,目前最常用的有电路图和硬件描述语言两种,对于简单的设计,可采用原理图的方式设计,对于复杂的设计可使用原理图或硬件描述语言(Verilog, AHDL, VHDL语言),或者两者混用,采用层次化设计方法,分模块层次地进行描述。 原理图设计方法主要是按照数字系统的功能采用具体的逻辑器件组合来实现的把这些由具体器件实现逻辑功能的电路图输入到软件当中。这种设计方法比较直观。 硬件描述语言设计方法主要把数字系统的逻辑功能用硬件语言来描述,采用VHDL语言描述的数字系统大致有三种;其一称为行为描述,它用几个包含着若干顺序语句的进程描述输入与输出之间的转换关系;其二是数据流描述,用一系列的并发信号赋值语句描述输入与输出之间的关系;其三为结构描述方式,是通过元件之间的互联关系描述输出电路的结构。无论是原理图输入还是描述语言输入都各有其优点,原理图设计适合于对器件比较熟悉,元件之间的互联清楚,并且需要的设计比较简单的情况,而对于器件不熟悉,设计复杂的情况来说,使用硬件描述语言要方便一些。 设计实现:设计实现是指从设计输入文件到熔丝图文件(CPLD)的编译过程。在该过程中,编译软件自动地对设计文件进行综合、优化,并针对所选中的器件进行映射、布局、布线、产生相应的熔丝图或位流数据文件,在此过程中,由于编译软件给系统管脚的分配是比较杂乱的,为了电路板布线的方便,用户可以对输入/输出管脚进行管脚锁定。 器件编程:器件编程就是将熔丝图文件或位流数据文件下载到相应的CPLD器件中,并与CPLD器件的管脚相对应,所用的软件是ALTARE公司提供的CPLDDN4,这是ALTARE公司CPLD系列的专用下载软件。 设计校验:对应于设计输入、设计实现和器件编程,设计验证分为了功能仿真、时序仿真、器件测试三个部分。功能仿真验证设计的逻辑功能,在设计输入过程中,对部分功能或整个设计均可进行仿真;时序仿真是在设计实现以后,针对器件的布局、布线方案进行时延仿真,分析定时关系:器件测试是在器件编程后,通过实验或借助测试工具,测试器件最终的功能和性能指标。 在设计中系统的接口电路、信号源的大多数逻辑控制都在CPLD中实现。 在该流程中仿真是重点。仿真又可分为功能仿真(前仿真)与时序仿真(后仿真)。根据电路设计编制仿真文件,在文件被综合前进行仿真,可验证电路功能;在保证电路已实现设计的功能后,进行综合并对综合的结果进行时序仿真,可验证电路的时序是否满足要求。当电路的前仿真与后仿真都满足要求,则电路的设计是成功的。然后设置器件类型并进行引脚锁定,再对文件进行适合于所加配置的逻辑综合;通过后即完成设计。最后结合系统中的其它部分进行连调,如发现问题可修改设计。 本设计中使用了ALTERA公司提供的配套软件MAX+PLUSII进行文件的输入、编译和下载。MAX+PLUSII的软件设计主要由设计输入、项目编译、项目校验和器件编程等四部分构成。 图2.1-1 CPLD设计流程图

图2.1-2 MUS+PLUSⅡ设计的主要组成部分 2.1.2 三相函数多波形发生器技术指标

三种波形之间的相位差均为120°,可以同时输出,具有三相的功能。对以下三种波形的频率均要求:产生的频率都可以预置;输出的信号幅值能在100mv~3V的范围内调整。 对正弦波信号的要求为:信号频率范围:20Hz-20kHz之间可调,步长为10Hz; 非线性失真系数≤3%。 对方波信号的要求是:信号频率范围:20Hz-20kHz;上升和下降时间<1μs; 对三角波信号的要求为:信号频率范围:20Hz-20kHz之间可调。 2.1.3三相波形发生器设计方法概述

Direct Digital Synthesis(DDS)是20世纪60年代末出现的第三代频率合成技术。用DDS技术来设计制作一个基于CPLD的三相多波形函数发生器,并使它能输出正弦波、三角波、方波等波形信号源,三种波形的相位差为120˚。 波形发生器中的CPLD芯片是DDS的控制及数据处理的核心,电路系统主要由时钟信号发生器、波形数据产生器和A/D转换电路组成。波形数据产生器由数控分频器、三角波产生模块、正弦波产生模块、方波产生模块等构成。在时钟信号发生器作用下,波形数据产生器生成频率可变的波形数据数字信号,由 A/D转换电路放大处理后输出最终所需要的波形信号。 各个模块的实现主要采用MAX+ plus II开发平台,由VHDL编程实现。先完成外围电路的焊接之后,用CPLD的专属下载软件把编写完的程序烧录入CPLD芯片,再对整个波形发生器进行调试,使其达到预期的效果。 2.2 设计方案

2.2.1 三相函数发生器设计原理

DDS制作的三相波形发生器主要由标准参考频率源、相位累加器、波形存储器、数模转换器、低通平滑滤波器构成。在时钟脉冲的控制下,频率控制字K由相位累加器得到相应的相码,相码寻址波形存储器进行相码——幅码变换输出不同的幅度编码,再经过数模变换器得到相应的阶梯波,最后经低通滤波器对阶梯波进行平滑,即得到由频率控制字决定的连续变化的输出波形。其中,参考频率源一般是一个高稳定的晶体振荡器,其输出信号用于DDS中各部件同步工作。因此,DDS输出的合成信号的频率稳定度与晶体振荡器是一样的。 DDS系统核心是N位相位累加器。相位累加器的结构一般N位字长的二进制加法器与一个由时钟触发的N位二进制相位累加寄存器级联构成,加法器的一个输入端与相位寄存器的输出端相连,另一个输入端是外部的频率控制字K。在每一个参考时钟脉冲输入时,把频率字累加一次,并把相加后的结果送至累加寄存器的数据输出端。由于相位累加器的输出连接在波形存储器的地址线上。因此其输出的改变就相当于进行查表。系统中的参考时钟通常是一个高稳定性的晶体振动器,用来作为系统时钟同步整个系统的各组成部分。在系统时钟脉冲的作用下,相位累加器不停地累加.也即不停地查表,不停地把波形重新合成出来,当相位累加器累加满时就会产生一次溢出,完成一个周期性的动作,这个周期就是DDS合成信号的一个频率周期,累加器的溢出频率就是DDS输出的信号频率。。滤波器则进一步平滑D/A转换器输出的近似所需波形的锯齿阶梯波.同时滤出不必要的杂波。 图2.2-1 DDS的原理图 图2.2-2 相位累加器的结构示意图 若频率控制字设为M,相位累加器为N位,参考时钟频率fс,则输出频率为Mfс/2a(a=N)。DDS的输出频率下限对应于频率控制字M=0的情形,即输出频率为f。=0。根据Nyquist采样定理,DDS的输出上限频率为时钟频率的一半,即f。=½fс。但由于实际输出低通滤波器的非理想特性,可实现的频率上限为-2/5fo。即若参考频率为 ,DDS的输出频率范围是0—2/5fc。由于DDS的模块化结构,其输出波形由波形查找表中的数据来决定,因此,只需改变查找表中的数据,即可以方便地利用DDS产生出正弦波之外的其他波形,如余弦波、方波、三角波。锯齿波甚至调频、调相波以及带限的噪声信号。 三相分时复用原理:分时复用的原理是各路信号只占用同一信道的不同时间间隙进行信号传输。具体到本电路就是利用对正弦表寻址的高速度,使一个正弦表在不同时间段查寻不同相的正弦波的幅值,以达到减少正弦表所占用的CPLD资源的目的。 电路的具体实现:三路在相位上互差120。的地址数据并行输入通过一个三选一的选择器来进行选择,选择器的控制端接三进制的计数器。如,计数器为0时,输出的是A相的地址。计数器为1时,输出的是B相的地址.计数器为2时,输出的是C相的地址。因此只要使输入的三相地址周期性变化,就实现了并行输入的三相地址数据在时间上形成了连续,也就实现了三相地址数据的合成。这样就可以利用一个正弦表来得到三相的正弦值,把正弦表减少到没有采样分时复用时的1/3。数据的分离:通过分时复用,使得通过查寻一个正弦表得到在相位上互差的三相正弦波的幅值,但是由于输入的三相地址在时间上是连续的,即对ROM表寻址的地址只有一路,因此,虽然得到了三相正弦波的幅值,可是他们是按ADDRESS中各相之间的关系混合在一起的,因此,必需对所得到的幅值进行分离。才能得到三相正弦波。由波形ADDRESS中各相地址的相互关系可知,分离数据只要把分时复用的合成部分反接即可。

参数选择:相位累加器的字长决定了频率分辨率.设计中取N=16。由于CPLD中硬件资源(主要是存储器EAB容量)所限,需对相位累加器输出的16位相位进行截断,这里取16位相位的前l0位进入相位,幅度转换电路,即A=10,输出数字幅度序列定位10位(D=10)。 图2.2-3 正弦波波形数据产生模块 这样确定的基本参数如下: (1)时钟频率和输出带宽根据已知的外部时钟源的频率fс=12MHz.那么本系统最高输出频率位2/5fo=4.8 MHz。 (2)频率范围由于要求输出的信号频率范围比较大.因此在12MHz时钟源引入CPLD后,在相位累加器之前增加了一个时钟分频器,可实现10、100、1000、10000次分频。根据输出信号的频率和精度要求,选择不同的分频比将50MHz时钟频率降低,再作位相位累加器和波形产生电路的参考时钟。 相位/幅度变换用CPLD实现相位/幅度变换电路是设计的一个难点。根据DDS原理,将不同波形的量化数据存储于波形查找表中,即可完成多波形发生的功能。ROM 的功能在本方案选用的Altera公司生产的CPLD芯片中实现,因此在实际设计中,要充分考虑表格数据的优化问题。根据上面的参数选择,取相位累加器字长M=16,截取前10位有效位,输出幅度序列定位l0位。这样直接实现正弦波形存储需要210xl0bitROM。正弦查找表可调用Maxplux2软件中的“lpm_rom”宏模块实现。 CPLD器件选择ALTERA公司的——EPM7128S84-15。它有128个宏单元、2500个等效逻辑门、15ns的速度、PLCC84封装形式。除电源引脚、地线引脚、全局控制引脚和JTAG引脚外,共提供了64个可用I/O脚,这些引脚可以任意配置为输入、输出和双向方式。该器件的特点如下: l是 一 种高性能的CM0SE EPROM器件。 l器 件 可通过JTAG接口实现在线编程。 l内 置 JTAG BST电路。 l可 编 程宏单元触发器具有专用清除、置位、时钟和时钟使能控制。 l 可 配 置的扩展乘积项分配,允许向每个宏单元提供多达32个乘积项。 EPM7128S器件是通过4个引脚的JTAG接口进行在线编程(ISP)的。ISP允许快速、有效地在设计开发过程中重复编程。JTAG(Joint Test Action Group)是欧洲的JETAG组织提出的边界扫描标准,即IEEE1149. 1标准。该标准提供了板级和芯片级的测试,所有JTAG测试功能仅需一条四线或五线的接口及相应的软件即能完成,利用JTAG能测试电路板的连接情况以及电路板的正确性。JTAG的接口信号为: lTCK (Test Clock):用于控制状态机及传递数据。 lTMS( Test Mode Select):选择边界扫描模式,控制状态机测试操作。 lDI ( Test Data Input):在TCK的一升沿,接受串行数据。 lTDO( Test Data Output):在TCK的下降沿,输出串行数据。 我们采用的是并口下载电缆ByteBlaster,它可以对MAX7000S系列进行在线编程。该下载电缆具有以下几个部分:与PC机并行口相连的25针插头、与PCB板插座相连的10针插头以及25针到10针的变换电路。可用于实现波形相位、幅度变换查找表(ROM)结构。DDS主要分为相位累加器、相位/幅度转换单元(含ROM)、数模变换器以及低通滤波等几个部分。 相位累加器和相位/幅度转换单元用CPLD实现,再将输出外接至DAC器件,最后通过低通滤波器即可得到所需波形。 图2.2-4 CPLD的外围电路连接图 2.2.2 多波形发生器的各个波形模块设计方式简介 数控分频器:数控分频器的功能是在输入端输入不同数据时,对输入时钟产生不同的分频比,输出不同频率的时钟,以改变输出信号的频率。设计时利用并行预置数的减法计数器实现,他的工作原理是:减法计数器在并行预置数的基础上,在时钟的作用下进行减计数,当计数值为零时产生溢出信号,加载预置数据,并且将溢出信号作为分频器的输出信号,实现分频信号输出。其分频系数N为预置数的值。为了得到占空比为50 的矩形时钟信号,将输出再进行二分频。由此,该分频器的总分频系数为2N。 三角波波形数据产生模块:该模块可设计一个可逆计数器实现。设计时设置一变量作为工作状态标志,在此变量为全0时,当检测到时钟的上升沿时进行加同一个数操作,为全1时,进行减同一个数操作。由于A/D转换采用8位的DAC0832芯片,且设64个时钟为一个三角波周期,则输出Q每次加8/减8。 正弦波波形数据产生模块:用加法计数器和译码电路完成。首先对幅度为1的正弦波的一个周期分为64个采样点,根据正弦波的函数关系计算得到每一点对应的幅度值,然后量化为8位二进制数据,最大值为255,最小值为0,以此得到正弦波波表。加法计数器生成译码电路的64个输入值,译码电路查波表输出。无论是相位累加器波形合成法还是基于RAM查询的波形合成法,都可以表示为合成信号的幅度与时间或是相位的关系,信号的幅度坐标存放在波形存储器中,通过地址发生器读取波形数据,完成数字波形。 方波波形数据产生模块:设计一个比较器,经过低通滤波器后的正弦波通过它后才能产生方波。通过交替送出全0和全1,并给以32个时钟延时实现,64个时钟为一个周期。 数据选择器:用CASE语句设计完成。在CORTROL的控制下选择输出一种波形数据输出,同时完成两种波形的线性组合。波形组合是将波形每一时刻的数值相加,为了不超出DAC0832的输出范围,做相应的除2操作。 首先由控制寄存器将外部控制器送入的数据转换为频率和幅度控制字;然后再由分频器根据频率控制字进行分频并将输出作为寻址计数器的时钟;寻址计数器的寻址空间为360字节,可对ROM中的查找表进行寻址;而通过模360加法器可以产生120o的相位差。 控制寄存器的设计:控制寄存器设计主要是将外部控制器输入的数据转换为频率和幅度控制字。 分频比可变的分频器模块设计:该设计主要是根据频率控制字决定分频倍数,从而输出与频率控制字相对应的频率时钟,此模块的输出可作为寻址计数器的时钟。 寻址计数器:主要用于产生对ROM寻址输出波形数据的寻址信号,寻址空间为360字节。 模360加法器设计:此模块用来产生120°的相移,以形成三相相差为120°的输出波形。由于寻址空间为360字节,故在输出寻址数大于360时,须对360取模。 查找表ROM设计:此模块主要用于存储各种波形数据,以便通过寻址计数器寻址输出并经D/ A转换来输出各种波形,其中包括正弦波、三角波、方波。 CPLD幅度控制字经D/A转换输出后,可作为查找表输出DAC的参考电压,该参考电压可通过改变幅度控制字来进行改变,从而改变输出信号的幅度。 图2.2-5 CPLD的内部结构设计框图 A/D转换采用了8位的DAC0832芯片。波形的产生是采用直接数字频率合成技术DDFS按照不同频率要求以频率控制字n为步进对相位增量进行累加,以累加相位值作为地址码读取存放于ROM内的波形数据,经D/A转换和幅度控制,再滤波即可得到波形。输出波形频率与寻址脉冲频率成正比,因此改变脉冲频率就可以改变输出波形频率。D/A转换电路的电路连接图主要由DAC0832和 LM324构成,附加了一些电容和电阻增加了其稳定性,它先通过DAC0832信号对信号进行数模转换,恢复为模拟信号后再由LM324构成的放大电路进行放大处理,使波形发生器达到预期的效果。 图2.2-6 DAC0832外围连接图 逻辑时序仿真:利用MAX+PLUXⅡ进行系统仿真。在时序波形中,clk为系统的时钟,这里设定仿真的时钟为200ns(晶振为12Mhz);freqin为频率字输入,它可以在1-1024取任意值,这里取freqin=l(即相位累加增量∆θ=360˚ /1024=0.35˚), 则f。 = 4.88kHz;pha-seina、phaseinb、phaseinc分别为三相互差120˚的相位字的输入, 取值分别为:phaseina=0、phaseinb=341、phaseinc=683;romadddr_a、romadddr_b、ro-madddr c分别为三相分时复用电路中的A相、B相和C相的相位值(三相互差),romadddr_abc为合成一路后的相位值。 为了便于在同一波形中可以同时看清输出数据中的各项,对仿真波形进行截取,为约3.5us-8.6US时的时序波形,ddsout_abc为查得 E弦表所得的三相混合数据,ddsout_a、ddsout_b、ddsout_c分别为数据分离后A相、B相和C相的相位对应的幅度值,由三相正弦波幅度之间的相互关系和变化趋势得知.输出的数据是正确的。由于DDS技术是从相位概念出发,根据确定的相位的有效字长组合,会产生相位截断误差。本设计的相位误差计算:每相正弦信号输出延时了2个系统时钟周期,即At=2Tc。因此相位误差为:∆θ=2π*f。*∆T,则∆θ=0.7˚。(这里设频率字M=1,字长N=10)。 整个系统除晶体振荡器和A/D转换外,全部集成在一片CPLD芯片上。它可输出三相频率、幅度可调的正弦波、三角波、方波。任意波形模块可由用户自行编辑所需波形数据,下载到CPLD芯片上,在不改变整个系统硬件连接的情况下,输出用户所需的波形。另外由于CPLD具有可编程重置特性,因而可以方便地更换波形数据,且简单易行,带来极大方便。 图2.2-7 波形仿真图 2.3 调试部分

2.3.1 CPLD在使用中遇到的问题

CPLD芯片提供了很多个电源引脚,为了减少芯片内部的干扰,尽量在每个电源引脚处加一个退藕电容,一般一个芯片周围不少于6个电容。 CPLD如果不能下载,可能有多种问题,先检查芯片的各个接地脚和电源脚是否全部连接正确,然后看四个JTAG引脚是否连接正确,可在下载时观测四个引脚上的信号。 对于不使用的全局变量,最好连接到地线。在编译的时候可能会出现所用的门数不多,但是编译通不过的情况,可以把逻辑综合的选项重新设置一下。 在逻辑综合的时候最好选择设计环境中对于特定的芯片所提供的综合条件,以免造成不必要的麻烦。 2.3.2 控制电路的调试

对控制电路进行时序仿真,在仿真图中几乎总会出现我们所不需要的毛刺,这些毛刺有时会给系统带来致命的影响,我们必须采取措施消除这样的毛刺。由于毛刺一般出现在信号发生电平转换的时刻,也即输出信号的建立时间内,而在输出信号的保持时间内不大会出现。因此,若带有毛刺的信号持续时间较长,我们可在输出信号的持续时间内用一定宽度的高电平脉冲选通一个与门来获得该信号,此时毛刺自然已被消除。高电平脉冲可由软件控制锁存器来得到。若带有毛刺的信号保持时间较短,可利用D触发器的D输入端对毛刺不敏感的特点,在输出信号的保持时间内用触发器读取输出信号,此时毛刺自然也已被消除,触发器的时钟沿可由软件控制地址译码器来得到。 另外 ,在某些情况下,需要对信号进行一定的延时,以完成特定的功能。利用D触发器可在时钟的控制下对信号进行比较精确的延时,这种方法的最小延时是半个时钟周期。延时也是消除毛刺的手段之一。 2.3.3 DAC电路的调试

DAC电路将RAM查找表输出的离散的数字信号变换为连续的模拟信号。所选的芯片为DAC0832,它的分辨率为12bits,建立时间为1us,差分电流输出。输出电流在2-20mA内可调。由于电流无法直接测量,所以在DAC0832的输出端和地之间接有一个20欧的电阻,可将输出的电流转换为电压来测,过程如下:首先向DAC输入全1的数据,测得输出端11脚的电压为0.4V;12脚为0.04 V;再向DAC输入全0的数据,测得输出端管11脚的电压为0.04 V;12脚为0.4V;说明DAC电路工作正常。 2.3.4 程序的调试

设计中使用了ALTERA公司提供的配套软件MAX+PLUSII进行文件的输入、编译和下载。MAX+PLUSII的软件设计主要由设计输入、项目编译、项目校验和器件编程等四部分构成。 2.3.5 硬件电路的调试

在硬件电路调试中,要注意焊接的艺术和元件的布局,让整体显得美观。不能出现漏焊、错焊等现象。在烧录入程序之后,对电路进行测试,看电路是否能达到预期的功能。如果不能,则要进行程序的调试,并检测电路连接、元件使用等方面的问题,努力排除故障,让系统功能实现。 结 论 论文中基于CPLD的波形信号发生器方面进行了设计,建立了包含三角波、正弦波、方波等三类信号的波形库,为波形的选择提供了较好的操作平台;把DDS技术与CPLD技术相结合来设计三相波形发生器,使三种信号的输出相位差均为120o。对电路数字部分完成了分步功能仿真和波形仿真,努力改善数字波形发生器的基带信号带宽,实现电路的集成化,采用双RAM双通道使设计出的数字波形发生器有更大的适用范围。本设计能应用到教学和科研试验中。 在分析了DDS及CPLD技术的基础上,设计了一种基于CPLD的三相数字波形发生器。利用CPLD开发工具对电路进行了设计和仿真,从分离器件到系统分布,每一步都经过了严格的波形仿真验证,以确保功能正常。 本文结合任意波形发生器的发展状况,对直接数字波形合成技术的理论、设计方法、电路实现以及信号的调理电路进行了深入的研究,归纳起来主要做了如下几方面的工作:1、采用CPLD自行设计了直接数字合成技术芯片,通过了实验验证;2、设计了内调幅电路;3、设计调试信号调理电路;4、编写了实验机主程序,波形数据输出程序。 从整体上看来,仪器所实现的指标基本上满足课题要求,但同时也存在着不足和需要进一步改进的工作,主要体现在:1、调频及任意波频率电路需要进一步改进,采用高位的锁相环器件;2、软件和硬件电路设计工作没有全部完成;3、由于技术限制,希望以后能使波形输出频率上一个更高台阶。 但是,也存在着某些不足。比如:当时由于开发周期和技术水平等原因,DDS技术均采用了国外成型的集成芯片,不仅代价高,而且许多性能没有充分利用,调幅波性能也不够高。 通过毕业课题设计,掌握了直接波形合成技术的原理及设计要领,学习了并掌握可编程逻辑器件电路的设计,掌握了MAX+PLUSII软件、CPLD元件等的应用,受益匪浅,为我今后的工作和学习奠定了坚实的基础。

参考文献 [1]沈明山.EDA技术及可编程器件应用时训[M].北京:科学出版社.2003

[2]付慧生.复杂可编程逻辑器件与应用设计[M].北京:中国矿业大学出版社.2003

[3]李国洪,沈明山等.可编程器件EDA技术与实践[M].北京:机械工业出版社.2004

[4]陈赜.CPLD/FPGA与ASIC设计实践教程[M].北京:科学出版社.2004

[5]蔡明生.电子设计[M].北京:高等教育出版社.2003

[6]李东升.电子设计自动化与IC设计[M].北京:高等教育出版社.2004

[7]李洋.EDA技术实用教程[M].北京:机械工业出版社.2005

[8]张秀娟,陈新华等.EDA设计与仿真实践[M].北京:机械工业出版社.2004

[9]尹常永.EDA技术与数字系统设计[M].陕西:西安电子科技大学出版社.2003

[10]潭会生,张昌凡等.EDA技术与应用(第二版)[M].陕西:西安电子科技大学出版社.2004

[11]王祖强.电子实际自动化(EDA)技术实验教程[M].山东:山东大学出版社.2003

[12]朱正伟.EDA技术及应用[M].北京:清华大学出版社.2004

[13]刘艳萍,高振斌等.EDA实用技术及应用[M].北京:国防工业出版社.2005

[14]焦素敏.EDA应用技术[M].北京:清华大学出版社.2004

[15]潘松,黄继业等.EDA技术与VHDL[M].北京:清华大学出版社.2003

[16]孔冬莲.基于CPLD的函数信号发生器[J].湖北鄂州.沙祥高等师范专科学院学报. 2006,(5).15-18

[17]郭海青.基于CPLD的多波形函数信号发生器设计[J].现代电子技术.2006,(17).70-72

[18] Wu Tao,Wang Jian Hua et al. Application study of DSP and CPLD technology on the star sensor[J].Journal of Harbin Institute of Technology(New Series),Vo1.13,No.3,2006.289-293

[19]任绪科,赵俊渭等. 基于CPLD和单片机的任意波形发生器设计[J].电子产品世界.2005,(1).118-119

[20] 尹佳喜,尹仕.CPLD的三相多波形函数发生器设计[J].国外电子元器件.2006,

(4).23-25

附录1 三相多波形函数发生器各模块的程序 LIBRARY ieee ; -----初值模块

use ieee.std_logic_1164.all;

entity chuzhi is

port(a:in std_logic_vector(3 downto 0);

q:out integer range 0 to 312);

end chuzhi;

architecture chu_arc of chuzhi is

begin

process(a)

begin

case a is

when"0001"=>q<=313;

when"0010"=>q<=156;

when"0011"=>q<=104;

when"0100"=>q<=78;

when"0101"=>q<=63;

when"0110"=>q<=52;

when"0111"=>q<=45;

when"1000"=>q<=39;

when"1001"=>q<=35;

when"1010"=>q<=31;

when others=>null;

end case;

end process;

end chu_arc;

LIBRARY ieee ; ----分频模块

use ieee.std_logic_1164.all;

entity fana is

port(a:in integer range 0 to 312;

clk:in std_logic;

q:out std_logic);

end fana;

architecture fan_arc of fana is

begin

process(clk)

variable b,d:std_logic;

variable c:integer range 0 to 312;

begin

if clk'event and clk='1'then

if b='0'then

c:=a-1;

b:='1';

else

if c=1 then

b:='0';

d:=not d;

else

c:=c-1;

end if;

end if;

end if;

q<=d;

end process;

end fan_arc;

LIBRARY ieee; -----方波模块

use ieee.std_logic_1164.all;

entity square is

port(clk,clr:in std_logic;

q:out integer range 0 to 255);

end square;

architecture sq_arc of square is

signal a:bit;

begin

process(clk,clr)

variable cnt:integer;

begin

if clr='0'then

a<='0';

elsif clk'event and clk='1'then

if cnt<7 then

cnt:=cnt+1;

else

cnt:=0;

a<=not a;

end if;

end if;

end process;

process(clk,a)

begin

if clk'event and clk='1'then

if a='1'then

q<=255;

else

q<=0;

end if;

end if;

end process;

end sq_arc;

LIBRARY ieee;------三角波模块

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity delta is

port(clk,reset:in std_logic;

q:out std_logic_vector(7 downto 0));

end delta;

architecture delta_arc of delta is

begin

process(clk,reset)

variable tmp:std_logic_vector(7 downto 0);

variable a:std_logic;

begin

if reset='0' then

tmp:="00000000";

elsif clk'event and clk='1' then

if a='0'then

if tmp="11111000"then

tmp:="11111111";

a:='1';

else

tmp:=tmp+8;

end if;

else

if tmp="00000111"then

tmp:="00000000";

a:='0';

else

tmp:=tmp-8;

end if;

end if;

end if;

q<=tmp;

end process;

end delta_arc;

LIBRARY ieee; ------正弦波模块

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity delta is

port(clk,reset:in std_logic;

q:out std_logic_vector(7 downto 0));

end delta;

architecture delta_arc of delta is

begin

process(clk,reset)

variable tmp:std_logic_vector(7 downto 0);

variable a:std_logic;

begin

if reset='0' then

tmp:="00000000";

elsif clk'event and clk='1' then

if a='0'then

if tmp="11111000"then

tmp:="11111111";

a:='1';

else

tmp:=tmp+8;

end if;

else

if tmp="00000111"then

tmp:="00000000";

a:='0';

else

tmp:=tmp-8;

end if;

end if;

end if;

q<=tmp;

end process;

end delta_arc;

LIBRARY ieee;------控制模块

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity chpro31 is

port(dlt,sqr,sin:in std_logic;

dlta,sqra,sina:in std_logic_vector(7 downto 0);

q:out std_logic_vector(7 downto 0));

end chpro31;

architecture ch_arc of chpro31 is

begin

process(dlt,dlta,sqr,sqra,sin,sina)

variable tmp:std_logic_vector(2 downto 0);

variable a,b:std_logic_vector(9 downto 0);

variable c,d,e:std_logic_vector(9 downto 0);

begin

tmp:=dlt&sqr&sin;

case tmp is

when "100"=>q<=dlta;

when "010"=>q<=sqra;

when "001"=>q<=sina;

when "110"=>a:="00"&dlta+sqra;

q<=a(8 downto 1);

when "101"=>a:="00"&dlta+sina;

q<=a(8 downto 1);

when "011"=>a:="00"&sqra+sina;

q<=a(8 downto 1);

when "111"=>a:="00"&dlta+sqra;

b:=a+sina;

c:="00"&b(9 downto 2);

d:="0000"&a(9 downto 4);

e:="000000"&a(9 downto 6);

a:=c+d;

b:=a+e;

q<=b(7 downto 0);

when others=>null;

end case;

end process;

end ch_arc;

附录2 元件介绍 1 DAC0832

DAC0832 是一种相当普遍且成本较低的数/模转换器,该器件是一个8位D/A转换器,其转换时间为1s,工作电压为+5V~+15V,基准电压为±10V,它将一个8位的二进制数转换成模拟电压,可产生256种不同的电压值,由于其内部有两个8位寄存器和一个8位D/A转换器,故可进行两级缓冲操作,使操作有很大的灵活性(本设计中采用的是单缓冲方式). DAC0832具有以下主要特性:①满足TTL电平规范的逻辑输入;②分辨率为8位; ③建立时间为1us;④功耗20mw;⑤是电流型输出型D/A转换器,在应用时外接运放使之成为电压型输出。DAC0832的片选地址为7FFFH,当P27有效时,若P0口向其送的数据为00H,则U 的输出电压为0V;若P0口向其送的数据为0FFH时,则的输出电压为-5V.故当输出电压为0V时,Vo:-5V.当输出电压为-5V时,可得:Vo =+5V,所以输出波形的电压变化范围为-5V ~+5V.连接硬件电路时将两级寄存器的控制信号并接输入数据,在控制信号作用下直接送入DAC寄存器中。经D/A转换和幅度控制,再滤波即可得到波形。 图1 DAC0832内部结构如图所示 图2 DAC0832 2 LM324

LM324四运放是美国national公司的产品。LM324是四运放集成电路,它采用14脚双列直插塑料封装。它的内部包含四组形式完全相同的运算放大器, 除电源共用外,四组运放相互独立。每一组运算放大器可用图1所示的符号来表示,它有5个引出脚,其中“+”、“-”为两个信号输入端,“V+”、“V-”为正、负电源端,“Vo”为输出端。两个信号输入端中,Vi-(-)为反相输入端,表示运放输出端Vo的信号与该输入端的位相反;Vi+(+)为同相输入端,表示运放输出端Vo的信号与该输入端的相位相同。 由于LM324四运放电路具有电源电压范围宽,静态功耗小,可单电源使用,价格低廉等优点,因此被广泛应用在各种电路中。 在本系统中,LM324被作为放大器和滤波器来使用。它可以选出各个不同频段的信号,指示出信号幅度的大小,对信号进行放大后再输出,提供给使用者需要的波形信号。 图3 LM324管脚图 3 PM7128SLC84-15芯片

EPM7128S84-15是CPLD芯片,有128个宏单元、2500个等效逻辑门、15ns的速度、PLCC84封装形式。除电源引脚、地线引脚、全局控制引脚和JTAG引脚外,共提供了64个可用I/O脚,这些引脚可以任意配置为输入、输出和双向方式。该器件的特点如下: l是 一 种高性能的CM0SE EPROM器件。 l器 件 可通过JTAG接口实现在线编程。 l内 置JTAG BST电路。 l可 编 程宏单元触发器具有专用清除、置位、时钟和时钟使能控制。 l 可 配 置的扩展乘积项分配,允许向每个宏单元提供多达32个乘积项。

图4EPM7128SLC84-15

附录3电路原理图 附录4 英文资料及译文 1英文资料 (From DIGITAL DESIGN principles & practices ,John F. Wakerly) Language Overview What is VHDL? VHDL is a programming language that has been designed and optimized for describing the behavior of digital systems. VHDL has many features appropriate for describing the behavior of electronic components ranging from simple logic gates to complete microprocessors and custom chips. Features of VHDL allow electrical aspects of circuit behavior (such as rise and fall times of signals, delays through gates, and functional operation) to be precisely described. The resulting VHDL simulation models can then be used as building blocks in larger circuits (using schematics, block diagrams or system-level VHDL descriptions) for the purpose of simulation. VHDL is also a general-purpose programming language: just as high-level programming languages allow complex design concepts to be expressed as computer programs, VHDL allows the behavior of complex electronic circuits to be captured into a design system for automatic circuit synthesis or for system simulation. Like Pascal, C and C++, VHDL includes features useful for structured design techniques, and offers a rich set of control and data representation features. Unlike these other programming languages, VHDL provides features allowing concurrent events to be described. This is important because the hardware described using VHDL is inherently concurrent in its operation. One of the most important applications of VHDL is to capture the performance specification for a circuit, in the form of what is commonly referred to as a test bench. Test benches are VHDL descriptions of circuit stimuli and corresponding expected outputs that verify the behavior of a circuit over time. Test benches should be an integral part of any VHDL project and should be created in tandem with other descriptions of the circuit. A standard language One of the most compelling reasons for you to become experienced with and knowledgeable in VHDL is its adoption as a standard in the electronic design community. Using a standard language such as VHDL virtually guarantees that you will not have to throw away and recapture design concepts simply because the design entry method you have chosen is not supported in a newer generation of design tools. Using a standard language also means that you are more likely to be able to take advantage of the most up-to-date design tools and that you will have access to a knowledge base of thousands of other engineers, many of whom are solving problems similar to your own. A brief history of VHDL VHDL, which stands for VHSIC (Very High Speed Integrated Circuit) Hardware Description Language, was developed in the early 1980s as a spin-off of a high-speed integrated circuit research project funded by the U.S. Department of Defense. During the VHSIC program, researchers were confronted with the daunting task of describing circuits of enormous scale (for their time) and of managing very large circuit design problems that involved multiple teams of engineers. With only gate-level design tools available, it soon became clear that better, more structured design methods and tools would be needed. To meet this challenge, a team of engineers from three companies ?IBM, Texas Instruments and Intermetrics ?were contracted by the Department of Defense to complete the specification and implementation of a new, language-based design description method. The first publicly available version of VHDL, version 7.2, was released in 1985. In 1986, the Institute of Electrical and Electronics Engineers, Inc. (IEEE) was presented with a proposal to standardize the language, which it did in 1987 after substantial enhancements and modifications were made by a team of commercial, government and academic representatives. The resulting standard, IEEE 1076-1987, is the basis for virtually every simulation and synthesi product sold today. An enhanced and updated version of the language, IEEE 1076-1993, was released in 1994, and VHDL tool vendors have been responding by adding these new language features to their products. Although IEEE Standard 1076 defines the complete VHDL language, there are aspects of the language that make it difficult to write completely portable design descriptions (descriptions that can be simulated identically using different vendors?tools). The problem stems from the fact that VHDL supports many abstract data types, but it does not address the simple problem of characterizing different signal strengths or commonly used simulation conditions such as unknowns and high-impedance. Soon after IEEE 1076-1987 was adopted, simulator companies began enhancing VHDL with new, non-standard types to allow their customers to accurately simulate complex electronic circuits. This caused problems because design descriptions entered into one simulator were often incompatible with other simulation environments. VHDL was quickly becoming a nonstandard. To get around the problem of nonstandard data types, another standard was developed by an IEEE committee. This standard, numbered 1164, defines a standard package (a VHDL feature that allows commonly used declarations to be collected into an external library) containing definitions for a standard nine-valued data type. This standard data type is called std_logic, and the IEEE 1164 package is often referred to as the Standard Logic package. The IEEE 1076-1987 and IEEE 1164 standards together form the complete VHDL standard in widest use today. (IEEE 1076-1993 is slowly working its way into the VHDL mainstream, but it does not add significant new features for synthesis users.) Standard 1076.3(often called the Numeric Standard or Synthesis Standard) defines standard packages and interpretations for VHDL data types as they relate to actual hardware. This standard, which was released at the end of 1995, is intended to replace the many custom (nonstandard) packages that vendors of synthesis tools have created and distributed with their products. IEEE Standard 1076.3 does for synthesis users what IEEE 1164 did for simulation users: increase the power of Standard 1076, while at the same time ensuring compatibility between different vendors?tools. The 1076.3 standard includes, among other things: 1) A documented hardware interpretation of values belonging to the bit and boolean types defined by IEEE Standard 1076, as well as interpretations of the std_ulogic type defined by IEEE Standard 1164. 2) A function that provides "don&care" or "wild card" testing of values based on the std_ulogic type. This is of particular use for synthesis, since it is often helpful to express logic in terms of "don抰 care" values. 3) Definitions for standard signed and unsigned arithmetic data types, along with arithmetic, shift, and type conversion operations for those types. The annotation of timing information to a simulation model is an important aspect of accurate digital simulation. The VHDL 1076 standard describes a variety of language features that can be used for timing annotation. However, it does not describe a standard method for expressing timing data outside of the timing model itself. The ability to separate the behavioral description of a simulation model from the timing specifications is important for many reasons. One of the major strengths of Verilog HDL (VHDL抯 closest rival) is the fact that Verilog HDL includes a feature specifically intended for timing annotation. This feature, the Standard Delay Format, or SDF, allows timing data to be expressed in a tabular form and included into the Verilog timing model at the time of simulation. The IEEE 1076.4 standard, published by the IEEE in late 1995, adds this capability to VHDL as a standard package. A primary impetus behind this standard effort (which was dubbed VITAL, for VHDL Initiative Toward ASIC Libraries) was to make it easier for ASIC vendors and others to generate timing models applicable to both VHDL and Verilog HDL. For this reason, the underlying data formats of IEEE 1076.4 and Verilog SDF are quite similar. When should you use VHDL? Why choose to use VHDL for your design efforts? There are many likely reasons. If you ask most VHDL tool vendors this question, the first answer you will get is, "It will improve your productivity." But just what does this mean? Can you really expect to get your projects done faster using VHDL than by using your existing design methods? The answer is yes, but probably not the first time you use it, and only if you apply VHDL in a structured manner. VHDL (like a structured software design language) is most beneficial when you use a structured, top-down approach to design. Real increases in productivity will come later, when you have climbed higher on the VHDL learning curve and have accumulated a library of reusable VHDL components. Productivity increases will also occur when you begin to use VHDL to enhance communication between team members and when you take advantage of the more powerful tools for simulation and design verification that are available. In addition, VHDL allows you to design at a more abstract level. Instead of focusing on a gate-level implementation, you can address the behavioral function of the design. How will VHDL increase your productivity? By making it easy to build and use libraries of commonly-used VHDL modules. VHDL makes design reuse feel natural. As you discover the benefits of reusable code, you will soon find yourself thinking of ways to write your VHDL statements in ways that make them general purpose. Writing portable code will become an automatic reflex. Another important reason to use VHDL is the rapid pace of development in electronic design automation (EDA) tools and in target technologies. Using a standard language such as VHDL can greatly improve your chances of moving into more advanced tools (for example, from a basic low-cost simulator to a more advanced one) without having to re-enter your circuit descriptions. Your ability to retarget circuits to new types of device targets (for example, ASICs, FPGAs, and complex PLDs) will also be improved by using a standard design entry method. Most of the VHDL features that are needed to support sequential-circuit design, in particular, processes, were already introduced in section 4.7 and were used in the VHDL sections in chapter 5. This section introduces just a couple more features and gives simple examples of how they are used .Larger examples appear in the VHDL sections of chapter 8. feedback sequential circuits A VHDL process and the simulator’s event-list mechanism for tracking signal changes form the sequential circuits may change state in response to input changes , and these state changes are manifested by changes propagating in a feedback loop until the feedback loop stabilizes. In simulation, this is manifested by the simulator putting signal changes on the event list and scheduling processes to return in “delta time” and propagating these signal changes until to no more signal changes are scheduled. Table 7-36 dataflow VHDL for an S-R latch. Table 7-36 is a VHDL program for an S-R latch, the architecture contains two concurrent assignment statements. Each of which gives rise to a process, as discussed in section 4.7.9, these processes interact to create the simple latching behavior of a S-R latch. The VHDL simulation is faithful enough to handle the case where both S and R are asserted simultaneously. The most interesting result in simulation occurs if you negate S and R simultaneously. Recall from the box from the page 536 that a real S-R latch may oscillate or go into a metastable state in this simulation. The simulation will potentially loop forever as each execution of one assignment statement triggers another execution of the other. After some number of repetitions, a well-designed simulator will discover the problem----delta time keeps advancing while simulated time does not----and halt the simulation. WHAT DO ‘U’ WANT It would be nice if the S-R latch model in table 7-36 produced a ‘u’ output whenever S and R were negated simultaneously, but it’s not that good. However, the languages is powerful enough that experienced VHDL designers can easily write a model with that behavior. Such a model would make use of VHDL’s time-modeling facilities, which we haven’t discussed, to model the latch’s “recovery time” (see box in page 537) and force a ‘u’ output if a second input change occurred too soon. It’s even possible to model a maximum assumed metastability resolution time in this way. Table 7-37 behavioral VHDL for a positive-edge-triggered D flip-flop Mote that if a circuit has the possibility of entering a metatable state, there’s no guarantee that the simulation will detect it, especially in larger designs. The best way to avoid metasbgability problems in a system design is to clearly identify and protect its asynchronous boundaries, as discussed in section clocked circuits

In practice, the majority of digital designs that are modeled using VHDL are clocked, synchronous systems using edge-triggered flip-flops. In addition to what we’ve already learned about VHDL, there’s just one more feature needed to describe edge-triggered behavior. The event attribute attached to a signal name to yield a value of type Boolean that is true if an event on the signal caused the encompassing process to run in the current simulation cycle, and false otherwise. Using the event attribute, we can model the behavior of a positive-edge-triggered D flip-flop with asynchronous clear as shown in table 7-37. here, the asynchronous clear input CLR overrides any behavior on the clock input CLK and is therefore checked first, in the “if” clause. If CLR is negated, then the “elsif” clause is checked, and its statements are executed on the rising edge of CLK. Note that “CL’event” is true for any change on CLK, and “CLK=’1’” is checked to limit triggering to just the rising edge of CLK. There are many other ways to construct processes or statements with edge-triggered behavior; table 7-38 shows two more ways to describe a D flip-flop ( without a CLR input ). Table 7-38 two more ways to describe a positive-edge-triggered D flip-flop. In the test bench for a clocked circuit, one of things you need to do is generate a system clock signal. This can be done quite easily with a loop inside a process, as shown in table 7-39 for a 100MHz clock with a 60% duty cycle. *****SYNTHESIS STUFF***** You may be wondering, how does a synthesis tool convert the edge-triggered behavior described in table 7-37 or 7-38 into an efficient flip-flop realization? Most tools recognize only a few predetermined ways of expressing edge-triggered behavior and map those into predetermined flip-flop components in the target technology. The synopsis synthesis engine used in the xinlinx foundation series 1.5 software recognize the”clk’event and clk=’1’” expression that we use in this book. Even with that as a given, VHDL has many different ways ashenden, author of the designer’s guide to VHDL (morgan Kaufmann, 1996) ran these statements and one other, with some modification, through several different synthesis tools. Only one of them was able to synthesize three out of the four forms, most could handle only two. So, you need to follow the method that is prescribed by the tool you use. Table 7-39 clock process within a test bench. reference The problem of metastability has been around for a long time. Greek philosophers wrote about the problem of indecision thousands of years ago. A group of modem philosophers named Devon sang about metastability in the title song of their Freedom of choice album. And the u.s. congress still can’t decide how to “save” social security. Scan capability was first deployed in latches. Not flip-flop, in IBM IC designs decades ago. Edward J.McCluskey has a very good discussion of this and other scan methods in logic design principles (prentice hall, 1986). Most ASICs and MSI-,PLD- and FPGA-based designs use the sequential circuit types described in this chapter. However , there are other types that are use in both older discrete designs (going all the way back to vacuum-tube logic ) and as well as in modem, custom VLSI designs. For example, clocked synchronous state machines are a special case of a more general class of pulse-mode circuits, Such circuits have one or more pulse inputs such that (a) only one pulse occurs at a time; (b) non-pulse inputs are stable when a pulse occurs; (c) only pulses can cause state changes; and (d) a pulse clock is the single pulse input, and a “pulse” is the triggering edge of the clock. However, it is also possible to build circuits with multiple pulse inputs. These possibilities are discussed very thoroughly in McCluskey’s logic Design Principle (prentice hall, 1986). A particularly important type of pulse-mode circuit that is discussed by McCluskey and others is the two-phase latch machine. The rationale for a two phase clocking approach in VLSI circuits is discussed by Carver Mead and Lynn Conway in introduction to VLSI systems (Addison-Wesley, 1980). There machines essentially eliminate the essential hazards present in edge-triggered flip-flops by using pairs of latches that are enabled by no overlapping clocks. Methods for reducing both completely and incompletely specified state tables are described in advanced logic design texts, including McCluskey’s 1986 book. A more mathematical discussion of these methods and other “theoretical” topics in sequential machine design appears in switching and finite automata theory, second edition, by Zvi Kohavi (McFGraw-hall, 1978). As we showed in this chapter, improperly constructed state diagrams may idle an ambiguous description of next-state behavior. The “if-then-else” structures in HDLs like ABEL and VHDL can eliminate these ambiguities, but they were not first to do so. Algorithmic-state-machine (ASM) notation. A flowchart-like equivalent of nested if-then-else statement, has been around for over 25 years. So-called ASM charts were pioneered at Hewlett-Packard Laboratories by Thomas E. Osborne and were pioneered by Osborne’s colleague Christopher R. Clare in a book, designing logic systems using ASM charts (McGraw-hill ,1973).Design and synthesis methods using ASM charts subsequently found a home in many digital design texts. Including the art of digital design by F.P.Prosser and D.E.Winkel (prentice hall, 1987, second edition ), and digital design by M.Morris Mano (prentice hall, 1984), as well as in the fist two editions of the book you’re just reading. Another notation for describing state machines is an extension of “traditional” state-diagram notation called the mnemonic documented state (MDS) diagram. It was developed by William I.Fletcher in an engineering approach to digital design (prentice-hall. 1980). ASM charts and MDS diagrams have now been largely replaced by HDLs and their compilers. Many CAD environments for digital design include a graphical state diagram entry tool. Unfortunately, these typically support only traditional state diagrams, making it very easy for a designer to create an ambiguous descriptions of next-state behavior. As a result, my personal recommendation is that you stay away from state-diagram editors and instead use an HDL to describe your state machines. We mentioned the importance of synchronizing sequences in connections with state-machine test vectors. There’s actually a very well developed but almost forgotten theory and practice of synchronizing sequences and somewhat less powerful “homing experiment” described by Frederick C.Hennie in Finite-state Models for logical machines (Wiley, 1968) Unless you’ve got this old classic on your bookshelf and know how to apply its teachings, please just remember to provide a reset input in every state machine that you design! 2英文译文 语言概观 VHDL是什么? VHDL是一种已经被为描述成为传统的行为设计最佳化的规划语言。 因为描述范围从简单的逻辑门到的电子成份的行为完成微处理器和习惯规定, VHDL 让许多特征适当。VHDL的特征允许线路行为 ( 像是上升而且落下时代的信号,延迟过门, 和功能的操作) 的电气特性精确地被描述。然后在那产生的VHDL 模拟模型为了模拟能在较大的线路 ( 使用图表, 区段图表或系统级的 VHDL 描述) 中被当作建电气区段使用。 VHDL 也是一种泛用型的规划语言:正如高阶层的规划语言允许复杂的要表示成电脑程式的设计观念, VHDL 允许复杂电子的线路行为对于自动的线路综合或系统模拟进入一个设计系统之内被捕获. 像巴斯卡, C 和 C++, VHDL 包括对结构化设计技术是有用的, 而且提供一富有组的控制和数据表现特征的特征。这些不像其他的规划语言, VHDL 提供特征允许协同的要描述的事件。因为被描述固有地使用 VHDL 的硬件在它的操作方面是协同的,所以这很重要。 VHDL 的最重要申请之一是为一个线路是以被普遍称为一张测试长椅子的东西形式。测试长椅子是线路 stimuli 和随着时间的过去查证线路的行为对应的预期输出的 VHDL 描述。测试长椅子应该是一个任何 VHDL 计画的整体部份并且应该在和其他线路的描述前后纵排的马车中被产生。 一种标准的语言 你的最无法抗拒的理由之一是变成的经验和聪明的在 VHDL 中是如电子的设计一个标准社区的它采用。使用一种标准的语言,像是VHDL事实上保证,只是因为你已经选择的设计进入方法不被在比较新的世代设计工具中支援,你将不必丢弃,而且取回设计观念。使用一种标准的语言也意味你更可能能够利用最新设计工具而且你将会有机会接近一个数以千计其他的工程师的知识库, 他们当中的一些人正在解决问题的多数类似你自己的。 VHDL 的简短历史 在1980年代早期内代表 VHSIC( 最高速集成电路) 硬件描述语言的 VHDL 被发展如被美国国防部部门赞助的高速集成电路研究计画的一个附带利益。在 VHSIC 计划的时候,研究员面对描述巨大尺寸 ( 对于他们的时间) 的线路使人畏缩工作并且管理非常大的线路设计牵涉了许多工程师团队的问题。由于唯一的门级设计可得的工具, 它很快变成清楚更,比较结构化设计方法和工具会是需要的。 为了要迎接这一挑战, 一些来自IBM ,德克萨斯工具和 Intermetrics三家公司的工程师被国防部雇佣完成一个新的规格和以语言为基础的设计描述方法。第一 VHDL,7.2 版的公众可得版本,在 1985到1986年被出版,美国电气电子工程师协会(IEEE) 与一份提议一起呈现标准化语言,它在提高和修正被做的重要部份之后在 1987 年做被一组由商业的,政府和学院的代表组成的成员定义产生了IEEE 1076-1987标准, 事实上这是今天出售的每个模拟综合产品的基础的语言, IEEE 1076-1993 的一个增强型版本,在1994年出版,而且VHDL工具厂商把这些新的语言特征加入他们的产品以做回应。 虽然 IEEE的1076标准定义了完整的VHDL语言, 但是使写完全手提式的设计描述的语言方面是困难的( 能同一地被模拟使用不同的厂商描述硬件工具)。问题起源于 VHDL 支持许多摘要数据类型,但是它不如未知数和高阻抗向如此的不同信号力量或普遍使用过的模拟所表示简单问题的特色为条件的运行。 在 IEEE 1076-1987 是采用不久后,模拟器公司开始用新又非标准提高 VHDL 类型允许他们的客户正确地模拟合成物电子线路。因为设计参与一个模拟器时常的描述对其他的模拟环境不匹配,所以这引起了问题. VHDL 正在很快地变成一种非标准的标准。 为了要解决非标准数据类型的问题, 另外的标准被一个 IEEE 委员会发展了。这一个标准,1164 号, 定义一个标准的程序包(允许要收集的普遍使用过的公告进入类似一间外部的图书馆之内的一个VHDL特征) 包含定义为一个标准的的数据类型。这种标准的数据类型叫做std_logic,而且IEEE 1164 数据包时常被称为标准的逻辑包。 IEEE 1076-1987和IEEE.1164标准一起在今天广泛的使用中形成了完整的 VHDL 标准。 (IEEE 1076-1993 慢慢地使它的设计方法进 VHDL 主流之内,但是它不为综合使用者增加重要的新特征。) 当VHDL与真实的硬件有关的时候,标准 1076.3( 时常认为数值的标准或综合是标准) 为 VHDL 数据类型定义标准了程序包解释。这一个在 1995 底被发布的标准预计代替许多习惯 ( 非标准的) 包装综合工具的厂商已经产生而且应用的产品。 IEEE的 1076.3标准为使用IEEE 1164综合模拟使用者做什么: 增加标准 1076 的功能, 增强在不同的厂商之间的兼容性。标准的 1076.3 包括, 在其他的事物之中: 1)标准的价值被证明的硬件解释属于IEEE 标准的1076, 连同被 IEEE 定义的 std_ulogic 类型的解释定义的 boolean 类型1164。 2) 一张提供以std_ulogic为基础的通行证。这对综合是有特别使用的, 因为它时常是有帮助的价值表达逻辑。 3)为标准的定义签署并且不签署算术数据类型,连同算术,变化和类型转变行动一起对于那些类型。 时间安排数据的注解对一个模拟模型是一个正确数据的重要方面模拟。VHDL 1076 标准描述多种语言能作为时间安排注解的特征。然而,它为在时间安排模型本身的外部表达时间安排数据不描述一个标准的方法。 区隔模拟模型的动作描述和时间安排规格的能力的许多理由是重要的。Verilog 高密度( VHDL抯最靠近的对手) 的主要力量之一是Verilog 高密度为时间安排注解明确地包括一个特征想要的事实。这一个特征,标准的延迟格式,或 SDF, 允许时间安排数据在一种制成表的形式中被表达而且在模拟的时候进入 Verilog 时间安排模型之内。 IEEE 1076.4 标准, 在1995后期中由IEEE 出版,把这一个能力加入一个标准的程序包。VHDL在这个标准的努力 (被配音重要的, 为VHDL 向ASIC图书馆的率先) 后面的一种主要的动力是让 ASIC厂商和其它使它变成更容易产生时间安排模型适用于VHDL 和Verilog高密度芯片。因为这一个理由, IEEE 1076.4 和Verilog 抯SDF 的在下面数据格式相当相似。 你应该使用 VHDL? 为什么选择使用 VHDL 作为你的设计? 有许多有可能的理由。如果你问大多数的 VHDL工具厂商这一个问题,你将会拿的第一个答案是“资讯科技将会改善你的生产力”。 但是究竟这意谓什么呢? 你能真的期待拿完成了快速的使用 VHDL 为你设计而超过使用你的现有设计方法? 答案是的肯定,但是或许不是你使用它第一目的,而且只有当如果你以结构化样子应用 VHDL。当你使用结构化又由上而下的方式设计的时候,VHDL( 像一种结构化软件设计语言) 是最有益的。生产力的真正增加稍后将会受到的影响,当你已经在 VHDL上更高地攀登学习曲线而且已经累积一间可以再度使用 VHDL 成份的图书馆的时候。 当你开始使用VHDL 提高生产力的时候,生产力增加也将会发生在队成员之间的沟通而且当你为模拟和设计可得的确认利用比较有力的工具时候。除此之外, VHDL允许你在一个较多的抽象水平设计。代替把重心集中在门级的落实,你能向设计的动作功能发表演说。 VHDL将会如何增加你的生产力? 借VHDL建立并且使用图书馆数据是容易普遍的。VHDL组件使设计重复使用让你觉得自然。就如你发现可以再度使用密码的利益,你将会很快找你自己方法思考使他们成为一般用途的方法。你对VHDL 陈述,写手提式的密码将会变成一个自动的反射。 使用 VHDL 的另外重要的理由是电子设计自动化 (EDA) 的工具和在目标技术方面的发展速度很快。使用一种标准的语言,像是 VHDL 能有效改善你无需再进入你的线路描述的更先进的工具 ( 举例来说,从一个基本的廉价模拟器到一个更先进的) 机会。也再对准对装置目标 ( 举例来说ASICs , FPGAs 和合成物 PLDs) 的新类型的线路让你由能力将会使用标准的设计进入方法改良。 VHDL时序电路设计特征: VHDL的大部分特征是为它支持时序电路而设计的,特别地,对“进程”,我们已经在4.7节里介绍过了,我们还将在第五章的VHDL部分利用它。本部分介绍一些其他的特征并给出一些如何利用的例子。更大得更全面的例子将在第八章的VHDL部分给出。 反馈时序电路: 一个VHDL进程和跟踪信号变化的模拟事件列表机制构成了在VHDL中处理反馈时序电路的基础。别忘了,反馈时序电路会随着输入信号的变化产生变化,而这些状态的变化在一个反馈环中用状态图显示出来,除非反馈环稳定下来。在模拟中,这将用在事件列表中的模拟输入信号的变化来显示,而且,预定的进程会在δ时间段后返回,并且传播这些变化直到不再有变化信号出现。 表7-36就是一个用VHDL语言编写的S-R锁存器的程序,其结构体包括两个并发语句,每一句都可以引发一个进程,如同在4.7.9种讨论的一样。这些进程互相地产生一个简单的S-R锁存器的功能行为。 VHDL仿真器足够真实地处理当S-R同时变化的情况。会有很多的有趣的仿真结果在现在仿真过程中,只要你同时启动S和R。回忆在536页上的图,那是一个真正的S-R锁存器,在上述情况下会引起振荡或进入不可测状态。这个状态将会潜在永久地锁定。每个语句的执行将会启动另一个语句的执行,经过一些重复,一个设计得非常好的仿真器就将显示问题——在仿真时间到来时,δ延迟保持在先——并停止仿真。 看起来,表7-36所显示的S-R锁存器在S和R同时复位时会产生一个‘U’输出似乎很好,但事实上并非一定如此美妙。别忘了,对一个VHDL的编程者而言,语言是足够强大的,以至可以轻松地描述一个具备某行为的模型,这个模型将利用VHDL的时间模型,这部分我们还没有探讨,在输出变化太快的情况下,还未对所存器模型的复位时间和产生‘U’输出进行模拟。 记住,如果一个电路有可能进入不定状态,就不能保证仿真器能检测到,尤其是在大型的设计中,一个系统的设计最好地避免不定态的方式是仔细辨认并保护它的不同步边沿,就如同在8.9部分讨论的那样。 表7-37 ****‘U’想要什么**** 7.12.2 时钟电路 在实际设计时,用VHDL语言进行模拟的大多数数字设计是时序的、用边沿触发器的同步系统。除了我们所学的VHDL特征,还有一个特征需要描述边沿触发器的行为,而“事件属性”可以被连接到一个信号,来产生一种布尔代数值,如果信号引发的事件能引起一个进程去执行当前的模拟循环,那么就对了,否则,就是错误的。 用“事件属性”,我们能模拟一个动态边沿D触发器的行为,如同在表7-37中描述的那样。 这里,同步清零CLR比时钟电路的其他任何行为都优先,因此在设计语句时,最先被检测,如果满足IF条件,那么就检测ELSIF语句,在CLK的边沿时,状态语句将被执行,记住,“CLK’EVENT”对CLK的任何变化都起作用,但“CLK=1”表示只在CLK上升沿才起作用,还有一些其他方式来构建具有触发器行为的进程和状态。表7-38显示了两种方式来描述一个D触发器(没有CLR输入)。 表7-38 在一个时钟电路的测试平台有一件你需要做的事是产生一个系统时钟信号,这可以轻松地完成,靠的是在一个进程中用一个循环。图表7-39所示,其为一个100MHz的而且有60%是零值的循环时钟信号。 综合工具 你可能想知道一个分析工具是如何实现将表7-37或表7-38中的边沿触发器行为变成一个高效的触发器行为的?大多数工具仅辨识少许稳定的描述触发行为的方式,而且在面向对象技术中把他们作为一个触发器元件。 在XILINX基本系列1。5版本软件中的综合分析工具能辨识“CLK’EVENT”和“CLK=1”的描述。也就是我们书中所描述的。除了给出的描述VHDL有许多不同的方式描述同一个功能,如在表7-38中所示。《VHDL读者指南》的作者Peter ashden(morgan kanfmann,1996)描述过这些内容,并通过某些修改,在不同的工具中运行过。仅仅一种能综合四种格式中的三种,大多数只能处理两个。因此,你需要去学习你所用工具适合的描述方法。 参考:

表7-39 不定现象长期存在,而且很久以前就有。古希腊哲学家们在几千年前就描述过不定现象。一些现代哲学家在他们所谓自由相册的标题中称Devo sang为不定现象。美国国会今天仍然不能决定如何去拯救社会安全。 在锁存器中IBM集成电路设计首要注重的是扫描功能,不是触发器,埃德华J.Mc克拉斯科列FPGA的设计利用了这章中描述时序电路类型。然而,还有其他类型也被应用在其它旧式的分离的设计中(如果完全回到真空管逻辑时代)同样,在现代的传统VLSI设计中也用到。举个例子,同步时序状态机是通常的几种脉冲模式电路的一个特殊例子。这种电路拥有一个或多个脉冲输入,或某个时刻只有一个脉冲或是一个脉冲在多数状态变化时产生或仅仅有脉冲才产生状态变化或当一个脉冲产生时,非脉冲输入是稳定的。在同步时许状态机中,一个脉冲是指一个时钟的触发边沿,然而用多脉冲输入也可以设计电路,不仅是用通用边沿触发器甚至用存储器元件也能设计,这些可能性在Mc克拉斯克的《逻辑设计原理》中有很好地描述。 一种脉冲电路中特别重要的类型在Mc克拉斯克的书中也被讨论到,其他的是二相锁存机。一种在VLSI中可行的二相锁存方式在卡瓦米德和宁·康威合著的书《VLSI系统导论》(1980年,爱迪生-为斯里出版社)有讨论过。 这些状态机基本上减少了在边沿触发器中的潜在危险,方式是用一对待非重叠时钟的有使能端的锁存器来实现。 在高级逻辑是教材中讨论过专业或半专业的状态图的化简方法,包括Mc克拉斯克1986年写的书,更多的数学上的关于这些方式的讨论和其他时序机的理论上的观点在《开关转换及有限自动化理论》(1978,第二版)中有过描述,如同在本章中讨论的,不正常的状态图会产生一个模糊的次态行为的描述。“IF-THEN-ELSE”是VHDL中的结构,如ABEL和VHDL能减少这种模糊。但它们不是最先完成这任务的。“数字状态机”(ASM)标注即一种与“IF-THEN-ELSE”等同的流图式的描述方法。在25年前就出现过,因此,ASM图在Hewlett-Packard实验室被首先开发,发明者是托马斯•E•奥本,继而由奥本的大学同学克里斯特法R克拉尔的书《用状态机设计逻辑系统》中被深入地发展了。 用ASM图设计和综合的方法很快在各种教材中出现,包括F.P波拉萨和D.E维克尔的书《数字设计艺术》及M.莫瑞斯马洛德《数字设计》,同样在你正在读的书的前两版中也写入了。 另外一个需要说明的关于描述状态机的是传统状态图的扩展,被称为MDS图,他由威廉.I.法拉奇在书《数字设计的工程方法》中发明。ASM图和MDS图现在绝大部分被HDL语言和他们的编译器代替。 许多数字设计适合各种CAD环境,包括电路图设计工具,不幸地是,这些环境只支持传统的状态图,是一个设计者很容易设计一个产生次态模糊行为的设计。因此,我个人建议是,你最好远离状态图设计而坚持用HDL来设计你的状态机。 我们这里提过同步时序与状态机测试矢量结合的重要性,确实,有一种关于同步时序的发展很完备但又几乎被忘记的理论和实践,其稍逊于“家庭实验室”,这被傅立德瑞克C亨利在书《逻辑机的有限状态模式》(1968年出版)中讲述过。 除非在你的书架上有这本经典的书,而且知道如何利用它,请要记住在你设计的每个状态机的输入端加一个复位输入。

致 谢 首先我要感谢指导我的闫舒静老师,在我的课题设计和论文撰写期间,他给予了悉心的指导。在选题、方案的优选及软硬件的实现方面,闫老师不仅给予了宝贵的意见,而且进行了耐心的启迪,这样不但开阔了我的视野,还大大激发了我的积极性。同时,闫老师治学严谨、精益求精、待人谦和,给我树立了做人、治学的榜样,对我今后的学习和工作都将产生长期的影响。在此,谨向闫老师致以最诚挚的谢意! 同时还要感谢实验室的其他老师:李广辉老师、刘老师等,他们在我做设计期间给予了无私的帮助和指导!

同时还要感谢帮助过我的同学们,在本次论文课题的实验过程中,得到了张华夏、田永贵、李睿涛等同学的帮助,在这里像他们表示深深的谢意!

另外还要感谢所有关心和帮助过我的朋友们!

|