本帖最后由 WeTiGY 于 2016-11-25 23:26 编辑

实验四 七段数码管显示电路一、实验目的 实现十六进制计数显示。 二、硬件需求 EDA/SOPC实验箱一台。 三、实验原理 七段数码管分共阳极与共阴极两种。共阳极数码管其工作特点是,当笔段电极接低电平,公共阳极接高电平时,相应笔段可以发光。共阴极数码管则与之相反,它是将发光二极管的阴极短接后作为公共阴极,当驱动信号为高电平、公共阴极接低电平时,才能发光。图2-13为共阳极数码管和共阴极数码管的内部结构图。

图2-13 共阳极数码管和共阴极数码管的内部结构图 用七段数码管除了可以显示0~9的阿拉伯数字外,还可以显示一些英语字母。下表是常见的字母与7段显示关系(共阴极数码管)。 | file:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image003.gif 段 字母 | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | |

四、实验内容 file:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image004.giffile:///C:/Users/ADMINI~1/AppData/Local/Temp/msohtmlclip1/01/clip_image004.gif编写一个0~F轮换显示的电路(注意:选用实验箱中的共阳数码管DP1A,FPGA上P25引脚连接50MHz时钟。实验时为了便于观察,要将50MHz时钟经过分频得到1Hz时钟)。第一个为分频模块:

- module divider_module

- (

- CLK,f_Out

- );

- input CLK;

- output f_Out;

-

- parameter T1s=26'd50_000_000;

- reg [25:0]Count1;

-

- always @ ( posedge CLK )

- if( Count1 == T1s)

- Count1 <= 26'd0;

- else

- Count1 <= Count1 + 1'b1;

-

- reg rf_Out;

- always @ ( posedge CLK )

- if( Count1 >= 26'd0 && Count1 <= 26'd25_000_000)

- rf_Out <= 1'b0;

- else

- rf_Out <= 1'b1;

- assign f_Out = rf_Out;

- endmodule

第二个为数码管模块:

- module hex_module

- (

- f_out,hex

- );

- input f_out;

- output [6:0] hex;

-

- parameter _0=7'b0000001, _1=7'b1111001, _2=7'b0010010, _3=7'b0000011, _4=7'b1001100, _5=7'b0100100,

- _6=7'b0100000, _7=7'b0001111, _8=7'b0000000, _9=7'b0000100, _A=7'b0001000, _B=7'b1100000,

- _C=7'b0110001, _D=7'b1000010, _E=7'b0110000, _F=7'b0111000;

-

- reg [4:0] i;

- reg [6:0] rhex;

- always@(posedge f_out)

- case(i)

- 5'd0 : begin rhex<=_0; i<=i+1'b1; end //0

- 5'd1 : begin rhex<=_1; i<=i+1'b1; end //1

- 5'd2 : begin rhex<=_2; i<=i+1'b1; end //2

- 5'd3 : begin rhex<=_3; i<=i+1'b1; end //3

- 5'd4 : begin rhex<=_4; i<=i+1'b1; end //4

- 5'd5 : begin rhex<=_5; i<=i+1'b1; end //5

- 5'd6 : begin rhex<=_6; i<=i+1'b1; end //6

- 5'd7 : begin rhex<=_7; i<=i+1'b1; end //7

- 5'd8 : begin rhex<=_8; i<=i+1'b1; end //8

- 5'd9 : begin rhex<=_9; i<=i+1'b1; end //9

- 5'd10: begin rhex<=_A; i<=i+1'b1; end //A

- 5'd11: begin rhex<=_B; i<=i+1'b1; end //B

- 5'd12: begin rhex<=_C; i<=i+1'b1; end //C

- 5'd13: begin rhex<=_D; i<=i+1'b1; end //D

- 5'd14: begin rhex<=_E; i<=i+1'b1; end //E

- 5'd15: begin rhex<=_F; i<=i+1'b1; end //F

-

- default: begin rhex<=_F; i<=1'b0; end //F

- endcase

-

- assign hex=rhex;

- endmodule

第三个为顶层模块,即将分频模块和数码管模块连接一起- module top_module

- (

- CLK,hex

- );

- input CLK;

- output [6:0] hex;

-

- wire f_out;

- divider_module u1

- (

- .CLK(CLK),

- .f_out(f_out)

- );

-

- hex_module u2

- (

- .f_out(f_out),

- .hex(hex)

- );

-

- endmodule

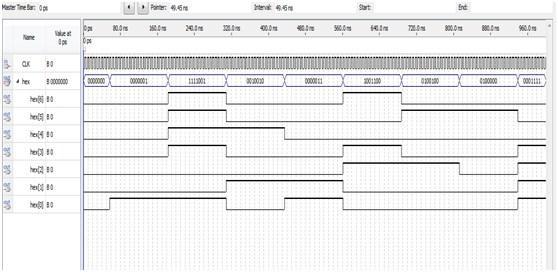

注:仿真使用20分频

仿真图:

|